(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1985 |

|

SU1251184A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU849307A1 |

| Программируемый генератор импульсов | 1984 |

|

SU1248029A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU765880A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

| Устройство цифроаналогового преобразования | 1985 |

|

SU1361716A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU799014A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Аналоговое запоминающее устройство | 1980 |

|

SU943852A1 |

| УСТРОЙСТВО ДЛЯ СВАРКИ ДАВЛЕНИЕМ | 1992 |

|

RU2049627C1 |

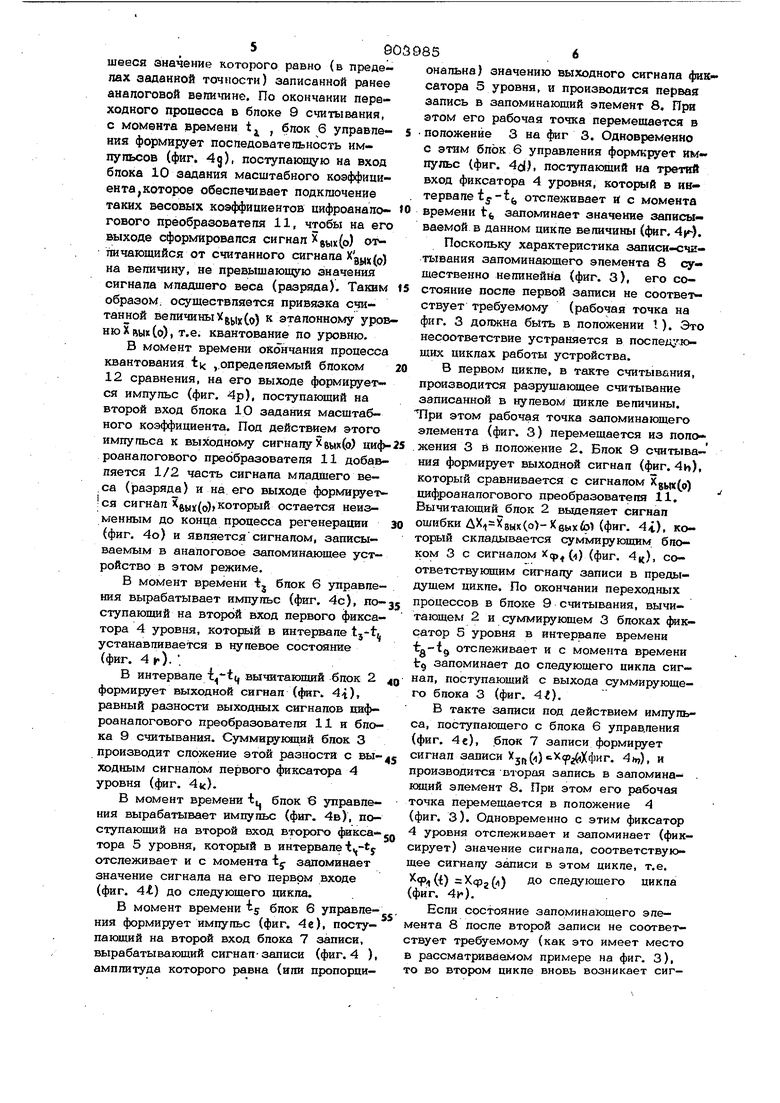

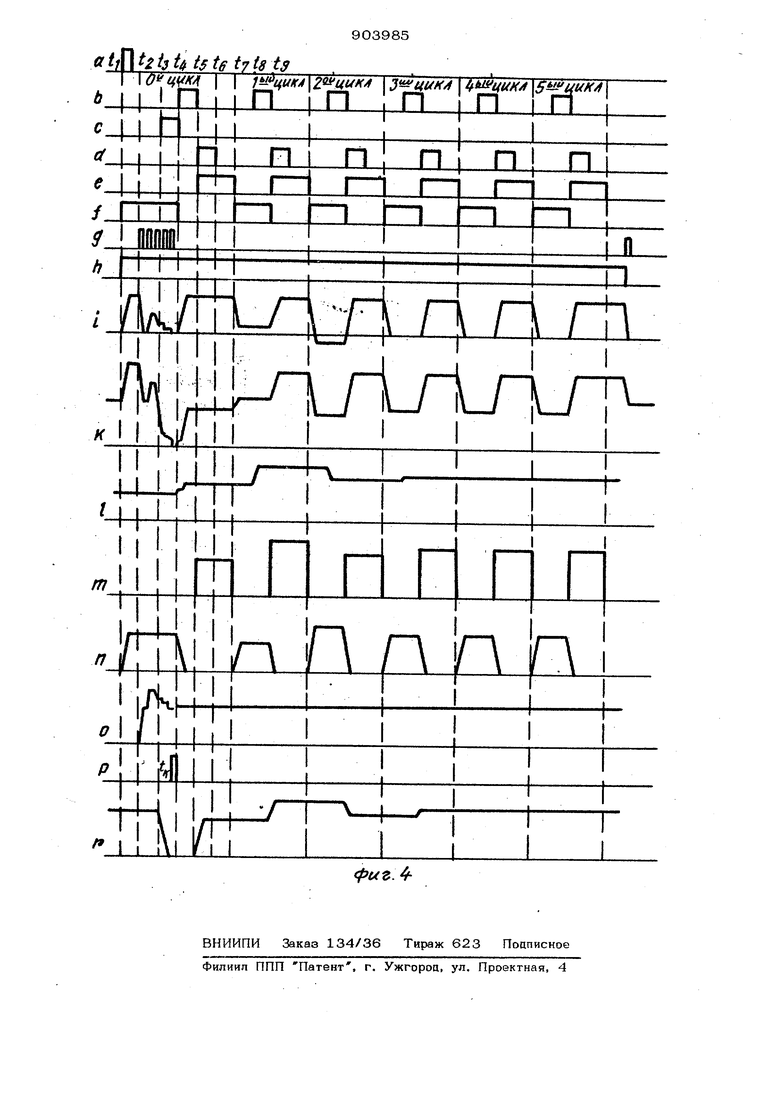

Изобретение относится к аналоговой вычиспитепьной технике и может быть использовано в устройствах обработки аналоговой информации, устройствах автоматики, измеритепьной и вычислительной техники. По основному авт. св. № 76588О из вестно аналоговое запоминающее устройство, содержащее вычитающий и суммирующий блоки, два фиксатора уровня, блок записи, запоминающий элемент с разрушающим считыванием информации, блок считывания и блок управпенияЙЗОднако известное аналоговое запоми нающее устройство позволяет производить только однократное считывание информации, что сужает его использование. Цель изобретения - повышение точное ти устройства при обеспечении многокра ного считывания информации. Поставленная цепь достигается тем, что в устройство введены блок сравнения, цифроаналоговый преобразоватетш, бпок задания масштабного коэффициента И коммутатор, первый вход которого яв- , ляется входом устройства, второй вход подключен к выходу цифроанапогового преобразователя, третий вход подключен к выходу блока управления, а выход - ко входу бпока вычитания, при этом выход блока управления подключен к первому входу блока задания масштабного -коэффициента, второй вход которого подключен к выходу блока сравнения, первый вход которого подключен к выходу блока считывания, второй вход - к выходу цифроаналогового преобразователя, входы которого подключены к выходам блока задания масштабного коэффициента, а выход цифроаналогового преобразователя является выходом устройства. На фиг. 1 приведена бпок-схема уст- рюйства; на фиг. 2 - принцип привязки аналоговой величины к эталонному уровню; на фиг. 3 - идеапизированная харак- теристика записи-считывания запоминающего элемента; на фи1 4 - упрошенная

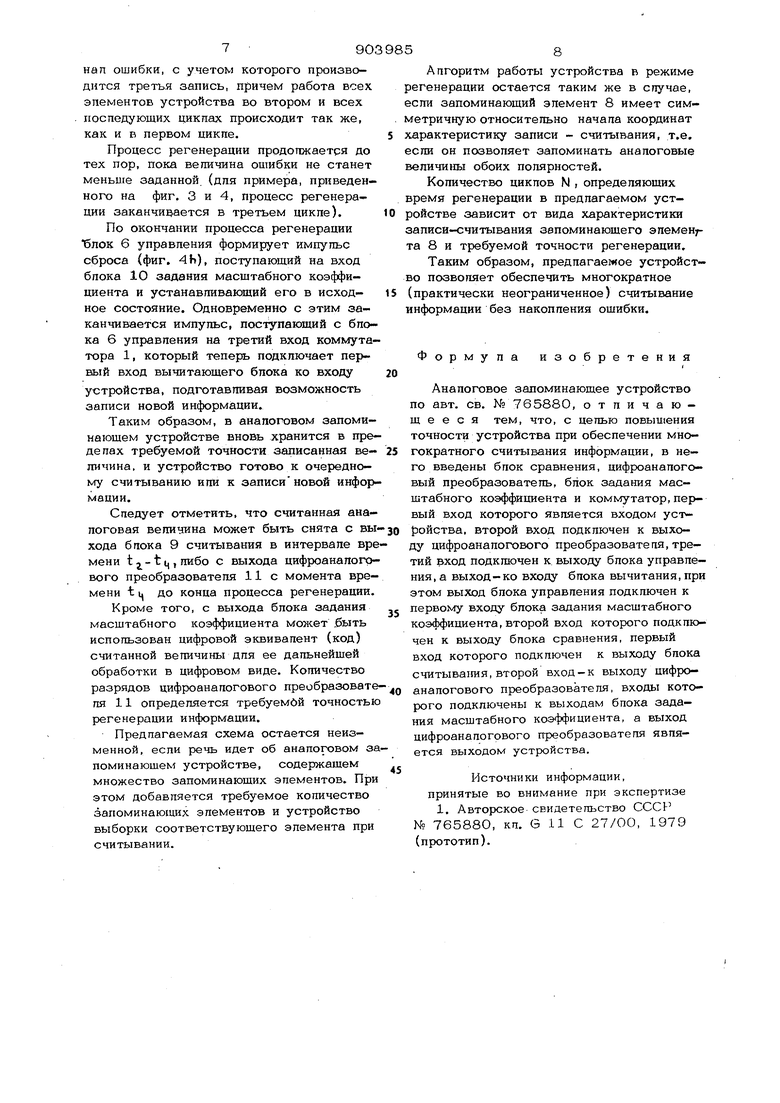

временная диаграмма работы блока аналоговой памяти.

Устройство (фиг. 1) содержит комму.татор 1, вычитающий блок 2, суммирующий блок 3, два фиксатора 4 и 5 уровня, блок 6 управления, блок 7 записи, . запоминающий элемент 8, блок 9 считывания, б пок 10 задания масщТабного коэффициента, цифроаналоговый преобразователь 11, блок 12 сравнения.

Устройство работает спедующим образом.

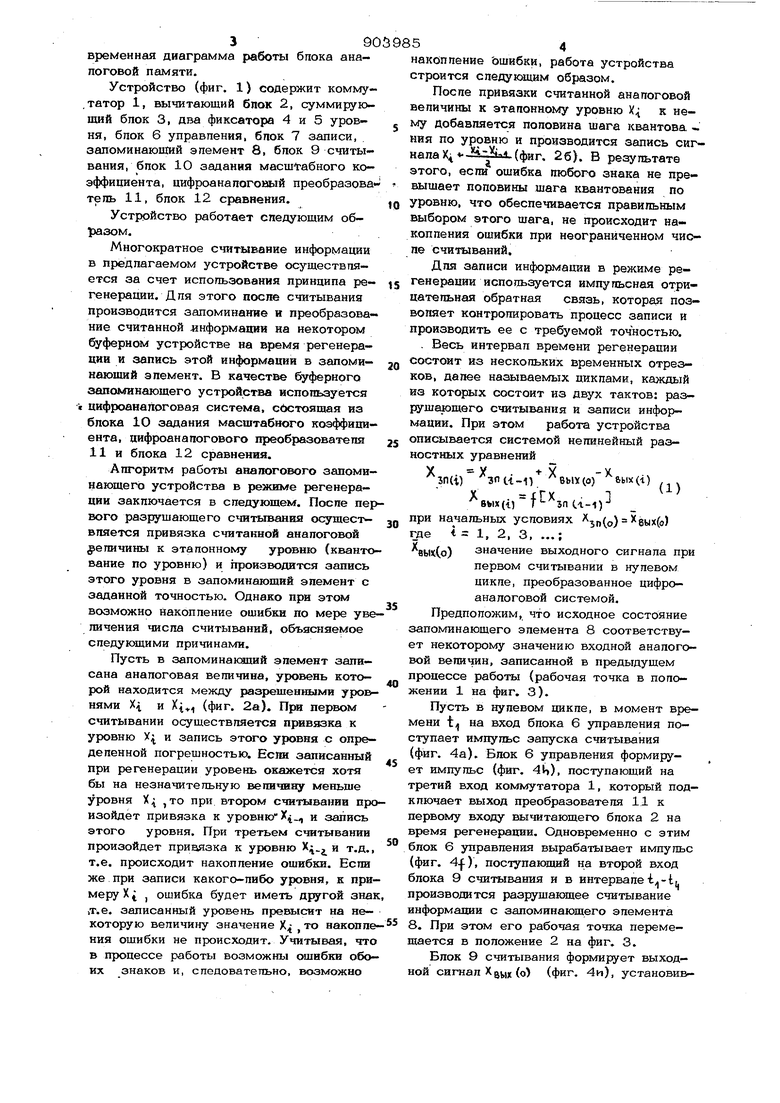

Многократное считывание информации в предлагаемом устройстве осушествляется за счет использования принципа регенерации. Для этого поспе считывания производится запоминание и преобразование считанной информации на некотором буферном устройстве на время регенерации и запись этой информации в заломинаюший элемент. В качестве буферного запоминающего устройства используется -. цифроанапоговая система, сбстояшая из блока 1О задания масштабного коэффициента. цифроаналогового преобразоватетга 11 и блока 12 сравнения. Алгоритм работы аватгогового запоминающего устройства в режиме регенерации заключается в следующем. Поспе первого разрушающего считывания осущест- вляется привязка считанной аналоговой величины к эталонному уровню (квантование по уровню) и производится запись этого уровня в запоминающий элемент с заданной точностью. Однако при этом возможно накопление ошибки по мере увеличения числа считываний, объясняемое следующими причинами. Пусть в запоминающий элемент записана аналоговая величина, уровень которой находится между разрешенными уровнями Х и Х. (фиг. 2а). Прт первом считывании осуществляется привязка к уровню Х и запись этого уровня с определенной погрешностью. Если записанный при регенерации уровень окажется хотя бы на незначительную вепичвну меньше уровня Х ,то при втором считывании про изойдет привязка к уровню Х, н запись этого уровня. При третьем считывании произойдет привязка к уровню X.j и т.д., т.е. происходит накопление ошибки. Если же при записи какого-либо уровня, к приMepy i , ошибка будет иметь другой знак ,т.е. записанный уровень превысит на некоторую величину значение Х , то накопле ния ошибки не происходит. Учитывая, что в процессе работы возможны ошибки обоих знаков и, спедоватепьно, возможно

накоппение ошибки, работа устройства строится спедующим образом.

После привязки считанной аналоговой величины к эталонному уровню Х к неыу Добавляется половина шага квантова ния по уровню и производится запись сигнала .(фиг. 26). В результате этого, если ошибка тобого знака не превышает половины шага квантования по уровню, что обеспечивается правильным выбором этого шага, не происходит накопления ошибки при неограниченном числе считываний.

Для записи информации в режиме регенерации используется импульсная отрицательная обратная связь, которая позволяет контролировать процесс записи и производить ее с требуемой точностью. . Весь интервал времени регенерации нескольких временных отрезков, далее называемых циклами, каждый из которых состоит из двух тактов: разрушающего считывания и записи информацни. При этом работа устройства описывается системой нелинейный раз- ностных уравнений у- уt у V ъпа snti-l) ВЫХ(о) 6bix(i) (i)f- зпи-1)при начальных условиях зп(о) 8ых(о) где t 1, 2, 3, ...; аых(о) значение выходного сигнала при первом считывании в нулевом цикле, преобразованное цифроаналоговой системой. Предположим, что исходное состояние запоминающего элемента 8 соответствует некоторому значению входной аналоговой величин, записанной в предыдущем процессе работы (рабочая точка в положении 1 на фиг. 3). Пусть в нулевом цикле, в момент времени t на вход блока 6 управления поступает импульс запуска считывания (фиг. 4а). Блок 6 управления формирует импульс (фиг. 4Ц). поступающий на третий вход коммутатора 1, который подключает выход преобразователя 11 к первому входу вычитающего блока 2 на время регенерации. Одновременно с этим блок 6 управления вырабатывает импульс (фиг. 4f), поступающий на второй вход блока 9 считывания и в интервале производится разрушающее считывание информации с запоминающего элемента 8. При этом его рабочая точка переме- щается в положение 2 на фиг. 3. Блок 9 считывания формирует выходной сигнал Xцу (о) (фиг, 4и), установив- 590 шееся значение которого равно (в пределах заданной точности) записанной ранее анапоговой вепичинс. По окончании пераходного процесса в бпоке 9 считывания, с момента времени t , бпок 6 управпения формирует последовательность импупьсов (фиг, 4д), поступающую на вход блока 10 задания масштабного коэффициента которое обеспечивает подкшочение таких весовых коэффициентов цифроанапогового преобразоватепя 11, чтобы на его выходе сформировался сигнал 5вык(о) отличающийся от считанного сигнала на величину, не превышающую значения сигнала младшего веса (разряда). Таким образоМ; осуществляется привязка считанкой величины У |ух (о) к эталонному уров ню X дых (о)) т.е. квантование по уровню. В момент времени окончания процесса квантования tx ,.определяемый блоком 12 сравнения, на его выходе формируется импульс (фиг. 4р), поступающий на второй вход блока Ю задания масштабного коэффициента. Под действием этого импульса к вызсодному сигнащг Хбых(о) ци4 роаналогового преобразователя 11 добавпяется 1/2 часть сигнала младшего веса (разряда) и на его выходе формируе-рся сигнал Л jyjf (о), который остается неизменным до конца процесса регенерации (фиг. 4о) и является сигналом, записыВаемым в аналоговое запоминающее устройство в этом режиме. В момент времени ij блок 6 управления вырабатывает импульс (фиг. 4с), noступающий на второй вход первого фиксатора 4 уровня, который в интервале tj-t устанавливается в нулевое состояние (фиг. 4 |f). В интервале , вычитающий блок 2 формирует выходной сигнал (фиг. ), равный разности выходных сигналов цнфроаналогового преобразоватепя 11 и блока 9 считывания. Суммируюший блок 3 производит сложение этой разности с выходным сигналом первого фиксатора 4 уровня (фиг. 4к). В момент времени Ьц блок 6 управления вырабатывает импульс (фиг. 4в), поступающий на второй вход второго фиксатора 5 уровня, который в интервале t,,-ty отслеживает и с момента ty запоминает значение сигнала на его первом входе (фиг. 44) до следующего циктю. В момент времени ty блок 6 управления формирует импульс (фиг. 4е), поступающий на второй вход блока 7 записи, вырабатывающий сигнал-записи (фиг. 4 ), амплитуда которого равна (или пропорци856онапьна) значению выходного сигнала фиксатора 5 уровня, и производится первая запись в запоминающий эпемент 8. При этом его рабочая точка перемещается в положение 3 на фиг 3. Одновременно с этим блок 6 управления формк1:ует импупьс (фиг. 4о1), поступающий на третий вход фиксатора 4 уровня, который в интервале tj-t отслеживает и с момента времени t{, зaпo raнaeт значение записываемой в данном цикле величины (фиг. 4(). Поскольку характеристика записи-считывания запоминающего элемента 8 существенно нелинейна (фиг. З), его состояние после первой записи не соответствует требуемому (рабочая точка на фиг. 3 должна быть в положении 1). Это несоответствие устраняется в послед;лющих циклах работы устройства. В первом цикле, в такте считывания, производится разрушающее считывание записанной в нулевом цикле величины. При этом рабочая точка запоминающего элемента (фиг. 3) перемещается из положения 3 в положение 2. Блок 9 считывания формирует выходной сигнал (фиг. 4и), который сравнивается с сигналом яифроаналогового преобразоватепя 11, Вычитающий блок 2 сигнал ошибки ,(x((xfo (фиг. 44,), который складывается суммирующим блоком 3 с сигналом )Cq) () (фиг. 4ц), соответствующим сигналу записи в предыдущем цикле. По окончании переходных процессов в блогсе 9 считывания, вычитающем 2 и суммирующем 3 блоках фиксатор 5 уровня в интервале времени t-fQ отслеживает и с момента времени Ц запоминает до следующего цикла поступающий с выхода суммирующего блока 3 (фиг. 41). В такте записи под действием импульса, поступающего с блока 6 управления (фиг. 4с), блок 7 записи формирует сигнал завися Х5(,))(,Хфиг. 4ъ), и производится вторая запись в запомина- . кший элемент 8. При этом его рабочая точка перемещается в положение 4 (фиг. 3). Одновременно с этим фиксатор 4 уровня отслеживает и запоминает (фиксирует) значение сигнала, соответствующее сигналу записи Б этом цикле, т.е. Хср() Хфг(4) ДО следующего цикла (фиг. 4), Если состояние запоминающего эле- ента 8 после второй записи не соответтвует тре емому (как это имеет место в рассматриваемом примере на фиг. 3), о во втором цикле вновь возникает сиг- 790 нап ошибки, с учетом которого произво- днтся третья запись, причем работа всех элементов устройства во втором и всех поспедующих циклах происходит так же, как и в первом цикле. Процесс регенерации продолжается до тех пор, пока величина ошибки не станет меньше заданной, (для примера, приведенного на фиг. 3 и 4, процесс регенерации заканчивается в третьем цикле). По окончании процесса регенерации блок 6 управления формирует импульс сброса (фиг. 4Ь), поступающий на вход блока 10 задания масштабного коэффициента и устанавливающий его в исходное состояние. Одновременно с этим заканчивается импульс, поступающий с блока 6 управления на третий вход коммутатора 1, который теперь подключает первый вход вычитающего блока ко входу устройства, подготавливая возможность записи новой информации. Таким образом, в аналоговом запоминающем устройстве вновь хранится в пределах требуемой точности зацисанная величина, и устройство готово к очередному считыванию или к записи новой инфор мации. Следует отметить, что считанная аналоговая величина может быть снята с вы хода блока 9 считывания в интервале вре мени tJ,-tц,либo с выхода цифроаналогрвого преобразователя 11с момента времени t ц до конца процесса регенерации. Кроме того, с выхода блока задания масштабного коэффициента может .быть использован цифровой эквивалент (код) считанной величины для ее дальнейшей обработки в цифровом виде. Количество разрядов цифроаналогового преобразовате ля 11 определяется требуембй точностью регенерации информации. Предлагаемая схема остается неизменной, если речь идет об аналоговом за поминаюшем устройстве, содержащем множество запоминающих элементов. При этом добавляется требуемое количество запоминающих элементов и устройство выборки соответствующего элемента при считывании. Алгоритм работы устройства в режиме егенерации остается таким же в случае, сли запоминающий элемент 8 имеет симетричную относительно начала координат арактеристику записи - считывания, т.е. сли он позволяет запоминать аналоговые еличины обоих полярностей. Количество циклов N , определяющих ремя регенерации в предлагаемом устойстве зависит от вида характеристики аписи-считывания запоминающего элемента 8 и требуемой точности регенерации. Таким образом, предлагаемое устройсто позволяет обеспечить многократное (практически неограниченное) считывание нформации без накопления ошибки. Формула изобретения Аналоговое запоминающее устройство по авт. св. № 765880, отличающееся тем, что, с целью повышения точности устройства при обеспечении многократного считывания информации, в него введены блок сравнения, цифроаналоговый преобразователь, блок задания масштабного коэффициента и коммутатор, первый вход которого является входом устройства, второй вход подключен к выходу цифроаналогового преобразователя,третий вход подключен к выходу блока управления, а выход-ко входу блока вычитания, при этом выход блока управления подключен к первому входу блока задания масштабного коэффициента, второй вход которого подключен к выходу блока сравнения, первый вход которого подключен к выходу блока считыва1гая, второй вход-к выходу цифроаналогового преобразователя, входы которого подключены к выходам блока задания масштабного коэффициента, а выход цифроаналогового гтреобразователя является выходом устройства. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССЬ № 765880, кл. 6 11 С 27/00, 1979 (прототип).

Фиг.2

Хзл{ 9/ X3rf7fJ ХМ(2ГХЗП13)

фи.З

Авторы

Даты

1982-02-07—Публикация

1979-02-09—Подача