1

Изобретение относится к вычислительной технике, в частности к технике запоминающих устройств, и может быть использовано в качестве устройства хранения аналоговой информации в устройствах автоматики и измерительной техники.

Цель изббретения - повышение точности устройства.

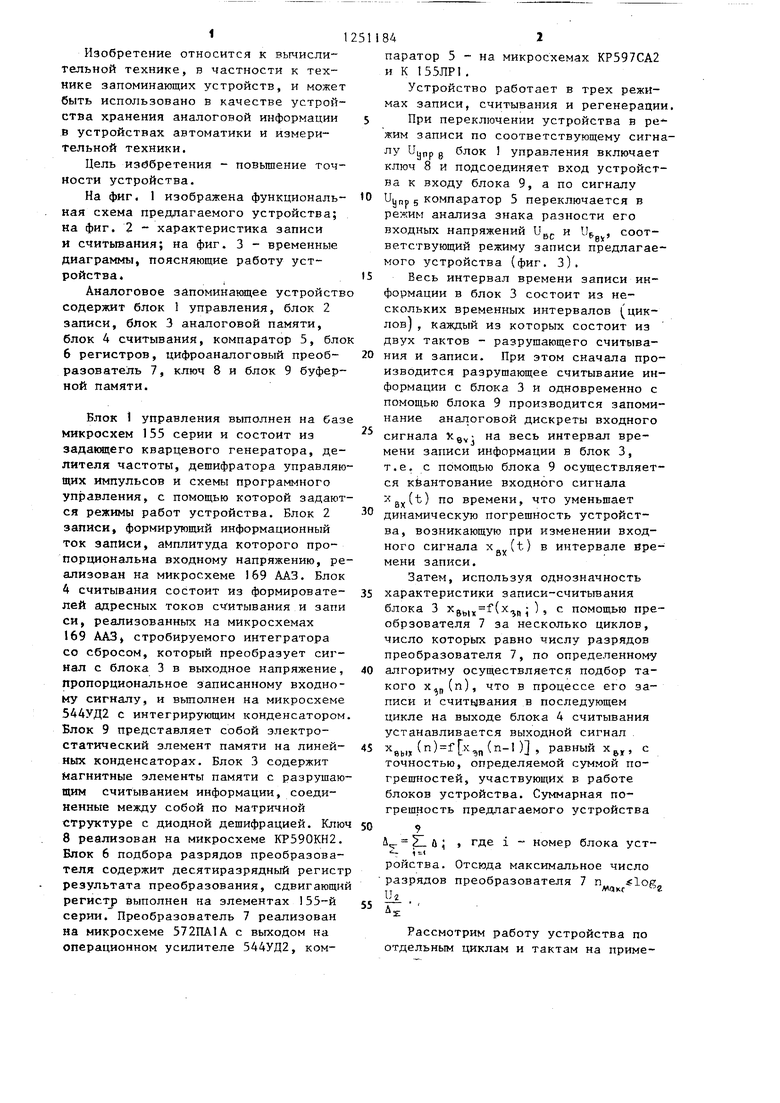

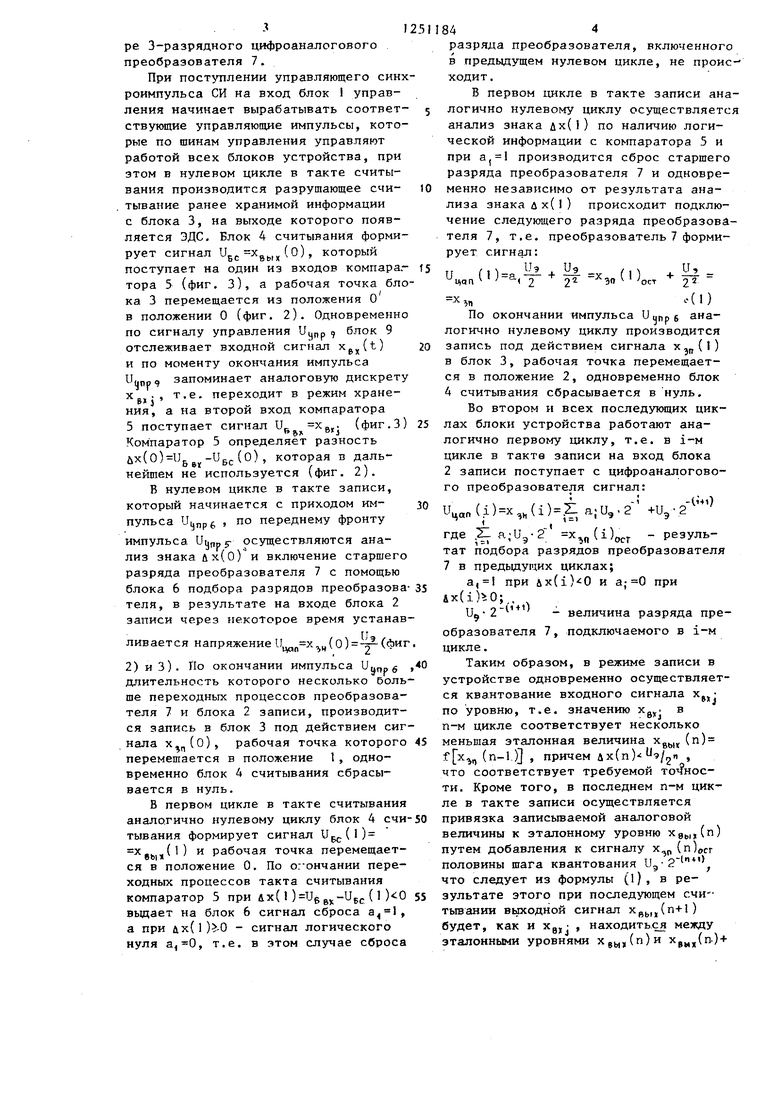

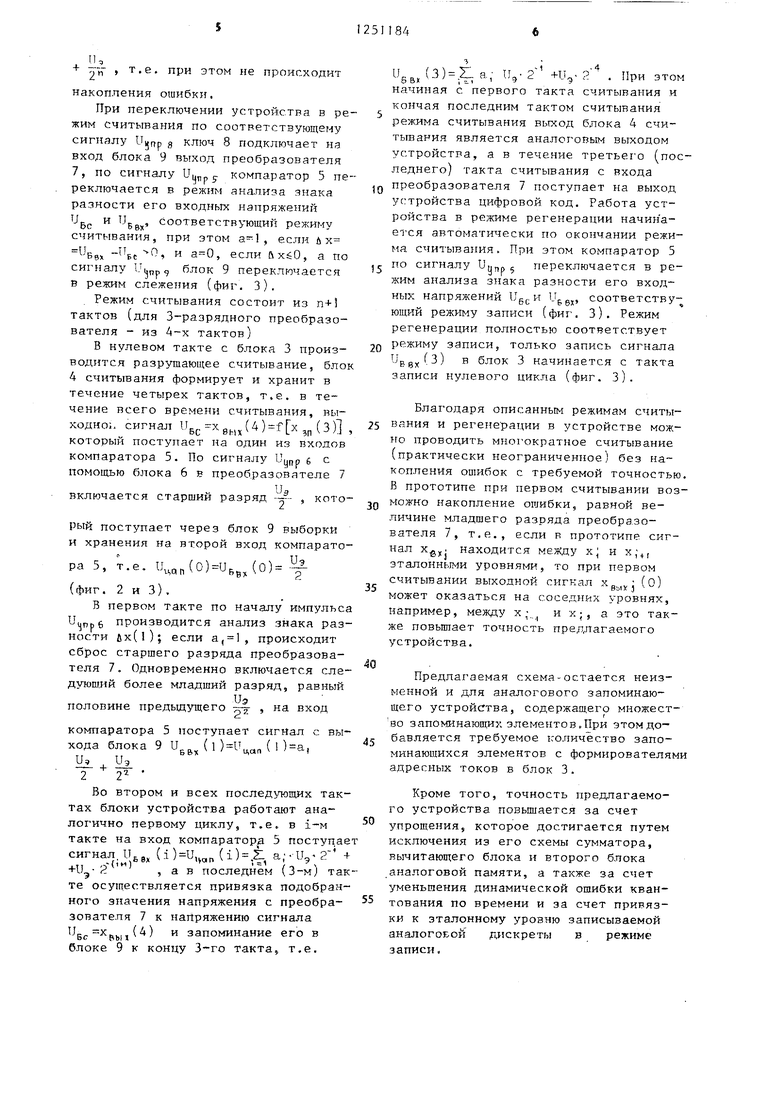

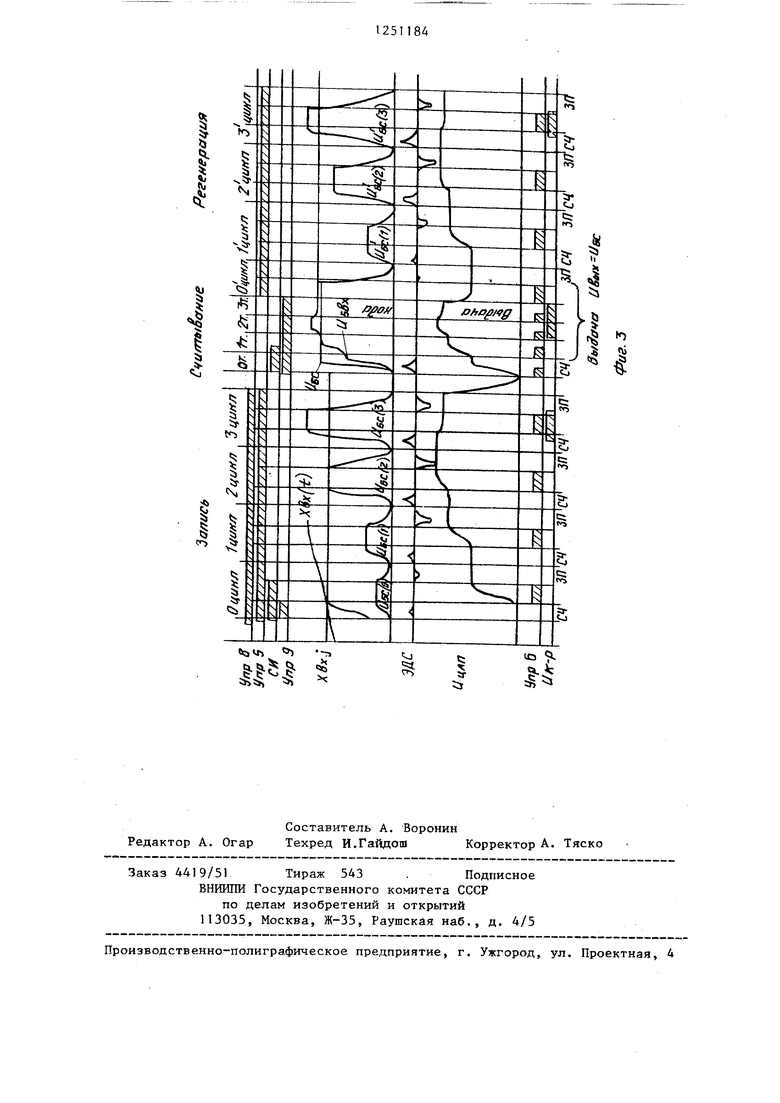

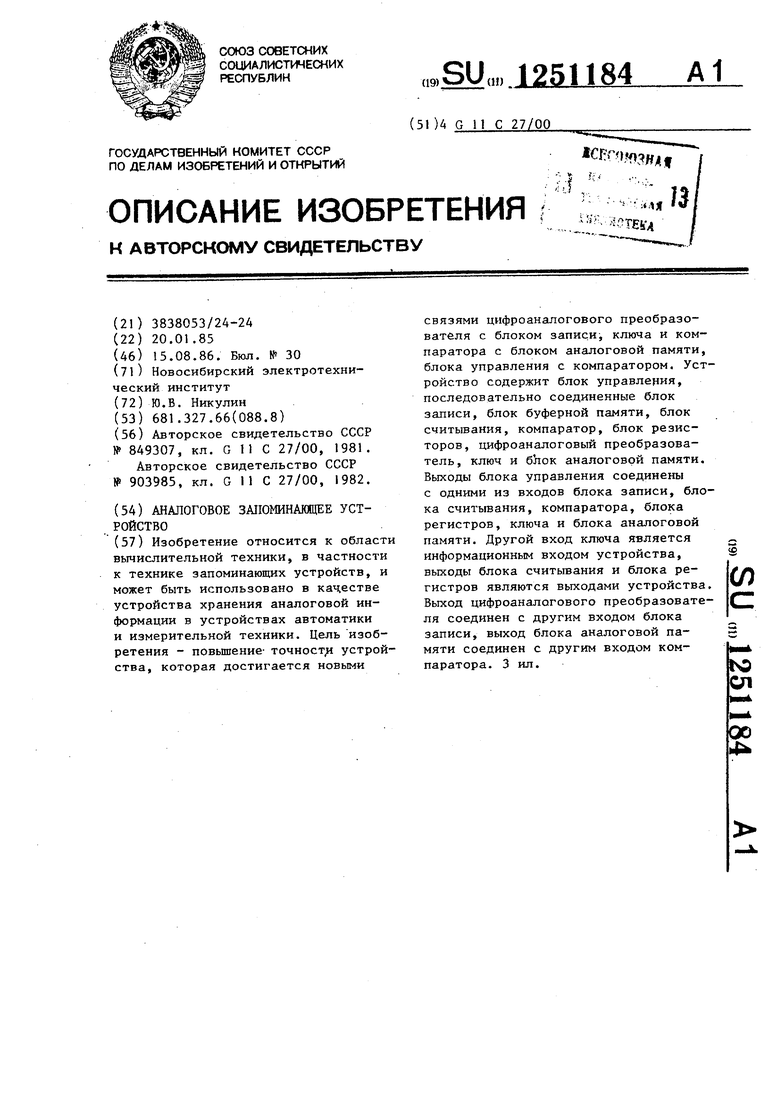

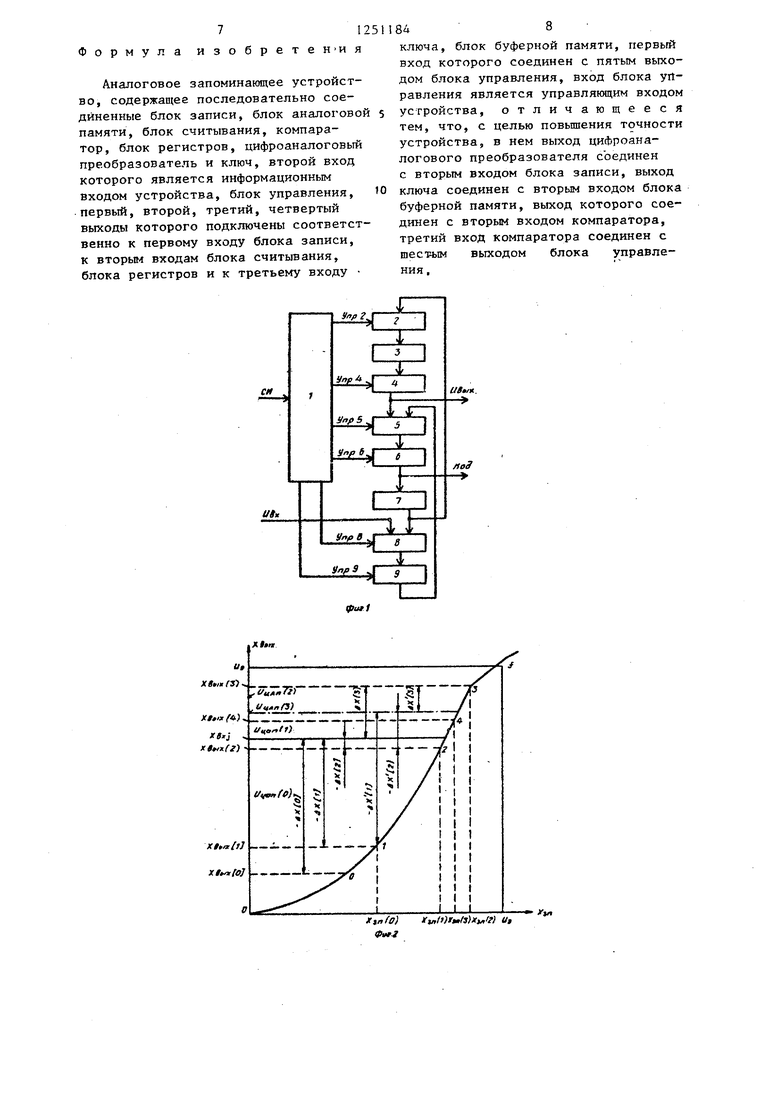

На фиг. 1 изображена функциональ- ная схема предлагаемого устройства; на фиг. 2 - характеристика записи и считьгаания; на фиг. 3 - временные диаграммы, поясняющие работу устройства.

Аналоговое запоминающее устройство содержит блок 1 управления, блок 2 записи, блок 3 аналоговой памяти, блок 4 считывания, компаратор 5, блок 6 регистров, цифроаналоговый преоб- разоватеЛь 7, ключ 8 и блок 9 буферной памяти.

Блок 1 управления выполнен на базе микросхем 155 серии и состоит из задающего кварцевого генератора, делителя частоты, дешифратора управляющих импульсов и схемы программного управления, с помощью которой задаются режимы работ устройства. Блок 2 записи, формирующий информационный ток записи, амплитуда которого пропорциональна входному напряжению, реализован на микросхеме 169 ААЗ. Блок 4 считывания состоит из формировате- лей адресных токов считывания и запи си, реализованньтх на микросхемах 169 ААЗ, стробируемого интегратора со сбросом, который преобразует сигнал с блока 3 в выходное напряжение, пропорциональное записанному входному сигналу, и выполнен на микросхеме 544УД2 с интегрирующим конденсатором Блок 9 представляет собой электростатический элемент памяти на линей- ных конденсаторах. Блок 3 содержит Магнитные элементы памяти с разрушающим считыванием информации, соединенные между собой по матричной структуре с диодной дешифрацией. Ключ 8 реализован на микросхеме КР590КН2. Блок 6 подбора разрядов преобразователя содержит десятиразрядный регистр результата преобразования, сдвигающий регистр выполнен на элементах 155-й серии. Преобразователь 7 реализован на микросхеме 572ПА1А с выходом на операционном усилителе 544УД2, ком8Д2

паратор 5 - на микросхемах КР597СА2 и К 155ЛР1,

Устройство работает в трех режимах записи, считывания и регенерации

При переключении устройства в режим записи по соответствующему сигналу Uypp g блок 1 управления включает ключ 8 и подсоединяет вход устройства к входу блока 9, а по сигналу Uynp 5 компаратор 5 переключается в режим анализа знака разности его входных напряжений U.,., и U

- .,,, COOTветствующий режиму записи предлагаемого устройства (фиг. З).

Весь интервал времени записи информации в блок 3 состоит из нескольких временных интервалов (циклов) , каждый из которых состоит из двух тактов - разрушающего считывания и записи. При этом сначала производится разрушающее считывание информации с блока 3 и одновременно с помощью блока 9 производится запоминание аналоговой дискреты входного сигнала х на весь интервал времени записи информации в блок 3, т.е. с помощью блока 9 осуществляется кбантование входного сигнала Xgjj(t) по времени, что уменьшает динамическую погрещность устройства, возникающую при изменении входного сигнала „„(t) в интервале вреоХ

мени записи.

Затем, используя однозначность характеристики записи-считьгаания блока 3 помощью пре- обрзователя 7 за несколько циклов, число которых равно числу разрядов преобразователя 7, по определенному алгоритму осуществляется подбор такого х.„(п), что в процессе его записи и считывания в последующем цикле на выходе блока 4 считывания устанавливается выходной сигнал .

) равный х,, с точностью, определяемой суммой погрешностей, участвующих в работе блоков устройства. Суммарная погрещность предлагаемого устройства

9

4 21 U J г Де i номер блока уст- -- Ui

ройства. Отсюда максимальное число разрядов преобразователя 7 Иг.

АЧГ

м.

Рассмотрим работу устройства по отдельным циклам и тактам на приме- 1

ре 3-разрядного цифроаналогового преобразователя 7.

При поступлении управляющего синхроимпульса СИ на вход блок I управления начинает вырабатывать соответ- ствующие управляющие импульсы, которые по шинам управления управляют работой всех блоков устройства, при этом в нулевом цикле в такте считывания производится разрушающее счи- тывание ранее хранимой информации с блока 3, на выходе которого появляется ЭДС. Блок 4 считывания формирует сигнал UBC вых который поступает на один из входов компара.- тора 5 (фиг. 3), а рабочая точка блока 3 перемещается из положения О в положении О (фиг. 2). Одновременно по сигналу управления блок 9 отслеживает входной сигнал Xg(t) и по моменту окончания импульса U(inp9 запоминает аналоговую дискрету X ., т.е. переходит в режим хранения, а на второй вход компаратора 5 поступает сигнал U ,- (фиг.З) Компаратор 5 определяет разность ux(0)(о) , которая в дальнейшем не используется (фиг. 2).

В нулевом цикле в такте записи, который начинается с приходом им- пульса U;jnp , по переднему фронту

импульса Uijnps- осуществляются анализ знака лх(о) и включение старшего разряда преобразователя 7 с помощью блока 6 подбора разрядов преобразова- теля, в результате на входе блока 2 записи через некоторое время устанавТ

ливается напряжение (О) -- (фиг

2) и 3). По окончании импульса Uunng длительность которого несколько боль ше переходных процессов преобразователя 7 и блока 2 записи, производится запись в блок 3 под действием сигнала X (о), рабочая точка которого перемешается в положение I, одновременно блок 4 считывания сбрасывается в нуль.

В первом цикле в такте считывания аналогично нулевому циклу блок 4 считывания формирует сигнал х.. (1) и рабочая точка перемещаетoOl я

ся В положение 0. По окончании переходных процессов такта считывания компаратор 5 при 4х( 1 )Ue -11 (1 ) вьодает на блок 6 сигнал сброса , а при 4х( 1 )-0 - сигнал логического нуля а,0, т.е. в этом случае сброса

844

разряда преобразователя, включенного в предыдущем нулевом цикле, не происходит .

В первом цикле в такте записи аналогично нулевому циклу осуществляется анализ знака дх(I) по наличию логической информации с компаратора 5 н при производится сброс старшего разряда преобразователя 7 и одновременно независимо от результата анализа знака дх(1) происходит подключение следующего разряда преобразователя 7, т.е. преобразователь 7 формирует сигнал:

и 9

0,2 х

ff -Зо()ос.

Ill - 22 зпЛ1)

По окончании импульса Uunpe аналогично нулевому циклу производится запись под действием сигнала х-„(1) в блок 3, рабочая точка перемещается в положение 2, одновременно блок 4 считывания сбрасывается в нуль.

Во втором и всех последующих циклах блоки устройства работают аналогично первому циклу, т.е. в i-м цикле в такте записи на вход блока 2 записи поступает с цифроаналогового преобразователя сигнал:

Уцаг, ( i) х ,, (i ) .Z. а; и, . 2 +иэ

- резуль2 (1).

где Z- a,-Ug

тат подбора разрядов преобразователя

7 в предыдущих циклах;

а, 1 при ix(i) 0 и а, при ix(i)iO;

- величина разряда преобразователя 7, подключаемого в i-м цикле.

Таким образом, в режиме записи в устройстве одновременно осуществляется квантование входного сигнала х,,

J по уровню, т.е. значению х. в

п-м цикле соответствует несколько меньшая эталонная величина х. (п) (п-1.) , причем дх(п) 9/2п , что соответствует требуемой TO JHOC- ти. Кроме того, в последнем п-м цикле в такте записи осуществляется привязка записьгоаемой аналоговой величины к эталонному уровню ,(п) путем добавления к сигналу х (п)осг половины шага квантования Ug-2 что следует из формулы (1), в результате этого при последующем счи тьшании выходной сигнал Xp,j(n+l) будет, как и Хц, , находиться между эталонными уровнями х.у,(п)и Хв,,(п.) +

Чмх

+ -„- , т.е. при этом не происходит

накопления ошибки.

При переключении устройства в ре- жим считывания по соответствующему сигналу Uijnp 8 ключ 8 подключает на вход блока 9 выход преобразователя 7, по сигналу UL,;,p5- компаратор 5 переключается в режим анализа знака разности его входных напряжений и и Ug, соответствующий режиму считывания, при этом а--1 , если л х ввх БС и , если , а по сигналу -Чпр 9 йлок 9 переключается в режим слежения (фиг. З).

Режим считывания состоит из тактов (для 3-разрядного преобразователя - из А-х тактов)

В нулевом такте с блока 3 произ- водится разрушающее считывание, блок 4 считывания формирует и хранит в течение четырех тактов, т.е. в течение всего времени считывания, вы- ходно;. сигнал g,, (4 )f х , (З) который поступает на один из входов компаратора 5. По сигналу 6 с помощью блока 6 в преобразователе 7

Из включается старший разряд , котора 5, т.е. и,дп

(0)-и,, (0):

Рый поступает через блок 9 выборки и хранения на второй вход компаратоиэ Т

(фиг. 2 и 3).

В первом такте по началу импульса Uypp производится анализ знака разности fix(l); если а,1, происходит сброс старшего разряда преобразователя 7. Одновременно включается следующий более младший разряд, равный

иэ

половине предьщутдего

2.

, на вход

компаратора 5

хода блока 9 U, (1 )U,,„„()

поступает сигнал с вы- бвх 1

Mi 4. УЭ.

Во втором и всех последующих тактах блоки устройства работают аналогично первому циклу, т.е. в i-м такте на вход компаратора 5 постуцае сигнал, ILg (l)-U,c,n (i),, a;-Ug- + +U 2 , a в последнем (3-м) такте осуществляется привязка подобранного значения напряжения с преобра- зователя 7 к напряжению сигнала - с ,,() и запоминание его в

ОС РЫ л

блоке 9 к концу 3-го такта, т.е.

БВХ) 5-2

1 -4 +Ug 2 . При этом

5

0 5

5

5

0

-

Начиная с первого такта считывания и кончая последним тактом считывания режима считывания выход блока 4 считывания является аналоговым выходом устройства, а в течение третьего (последнего) такта считывания с входа преобразователя 7 поступает на выход устройства цифровой код. Работа устройства в режиме регенерации начин а- ется автоматически по окончании режима с 1итывания. При этом компаратор 5 по сигналу U(jr,p 5 переключается в режим анализа знака разности его входных напряжений b g,., и , соответствующий режиму записи (фиг. З). Режим регенерации полностью соответствует режиму записи, только запись сигнала

URDv(3) в блок 3 начинается с такта

/

записи нулевого цикла (фиг. 3).

Благодаря описанным режимам считывания и регенерации в устройстве мож- fro проводить многократное считывание (практически неограниченное) без накопления ошибок с требуемой точностью. В прототипе при первом считывании возможно накопление ощибки, равной величине младшего разряда преобразователя 7, т.е., если в прототипе сигнал х,. находится между х; и х;+, эталонными уровнями, то при первом считывании выходной сигнал х.,.,; (О)

оЫ К J

может оказаться на соседних уровнях, например, между х их;, а это также повышает точность предлагаемого устройства.

Предлагаемая схема-остается неизменной и для аналогового запоминающего устройства, содержащего множест- во запоминающих элементов,При этом добавляется требуемое 1голичество запоминающихся элементов с формирователями адресных токов в блок 3.

Кроме того, точность предлагаемого устройства повыщается за счет упрощения, которое достигается путем исключения из его схемы сумматора, вычитающего блока и второго блока аналоговой памяти, а также за счет уменьшения динамической ошибки квантования по времени и за счет привязки к эталонному уровню записываемой аналоговой дискреты в режиме записи.

712

Формула изобрете Н И я

Аналоговое запоминающее устройство, содержащее последовательно соединенные блок записи, блок аналоговой памяти, блок считывания, компаратор, блок регистров, цифроаналоговый преобразователь и ключ, второй вход которого является информационным входом устройства, блок управления, первый, второй, третий, четвертый выходы которого подключены соответственно к первому входу блока записи, к вторым входам блока считывания, блока регистров и к третьему входу

848

ключа, блок буферной памяти, первый вход которого соединен с пятым выходом блока управления, вход блока управления является управляющим входом устройства, отличающееся тем, что, с целью повьшения точности устройства, в нем выход цифроана- логового преобразователя соединен с вторым входом блока записи, выход ключа соединен с вторым входом блока буферной памяти, выход которого соединен с вторым входом компаратора, третий вход компаратора соединен с шестым выходом блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Аналоговое запоминающее устройство | 1984 |

|

SU1244724A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для регистрации и определения параметров импульсных сигналов | 1986 |

|

SU1368819A2 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

| Способ многоканального аналого-цифрового преобразования и многоканальный аналого-цифровой преобразователь | 1986 |

|

SU1451858A1 |

| Многоканальное устройство для ввода аналоговых данных | 1986 |

|

SU1335972A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

Изобретение относится к области вычислительной техники, в частности к технике запоминающих устройств, и может быть использовано в качестве устройства хранения аналоговой информации в устройствах автоматики и измерительной техники. Цель изобретения - повьшение- тoчнocт c устройства, которая достигается новыми связями цифроаналогового преобразователя с блоком записи-, ключа и компаратора с блоком аналоговой памяти, блока управления с компаратором. Устройство содержит блок управления, последовательно соединенные блок записи, блок буферной памяти, блок считывания, компаратор, блок резисторов, цифроаналоговый преобразователь, ключ и блок аналоговой памяти. Выходы блока управления соединены с одними из входов блока записи, блока считьгеания, компаратора, блока регистров, ключа и блока аналоговой памяти. Другой вход ключа является информационным входом устройства, выходы блока считывания и блока регистров являются выходами устройства. Выход цифроаналогового преобразователя соединен с другим входом блока записи, выход блока аналоговой памяти соединен с другим входом компаратора. 3 ил. о (Л

ЛЬ

| Аналоговое запоминающее устройство | 1979 |

|

SU849307A1 |

| Прибор с двумя призмами | 1917 |

|

SU27A1 |

| Аналоговое запоминающее устройство | 1979 |

|

SU903985A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-08-15—Публикация

1985-01-20—Подача