. 1

Изобретение относится к области артоматического управления сложными объектами и может быть использовано для автоматического регулирования летательных аппаратов.

Известен многоканальный регулятор, содержащий коммутатор, преобразователь аналог-код и устройство управления, осуществляющее регулирование большого числа параметров

К недостаткам известного устройства относятся невозможность регулирования пр сложным законам, а также невысокая точность.

Наиболее близким к изобретению техническим решением является управляющий процесс, содержащий первый преобразователь код-напряжение, цифровой вход которого через цифровой запоминающий блок соединен с первым выходом устройства управления, вторым выходом подключенного к управляющему входу коммутатора, первые входы которого соединены с соответствующими выходами объекта регулирования, остальные вторые входы - с соответствукйцими выходами регулятора, а выход - с аналоговым входом преобразователя код-напряжение {2 .

Основной недостаток известного устройства заключается в его низкой точности при усложнении алгоритмов с управления.

Цель изобретения - повышение точности регулятора.

Указанная цель достигается тем,

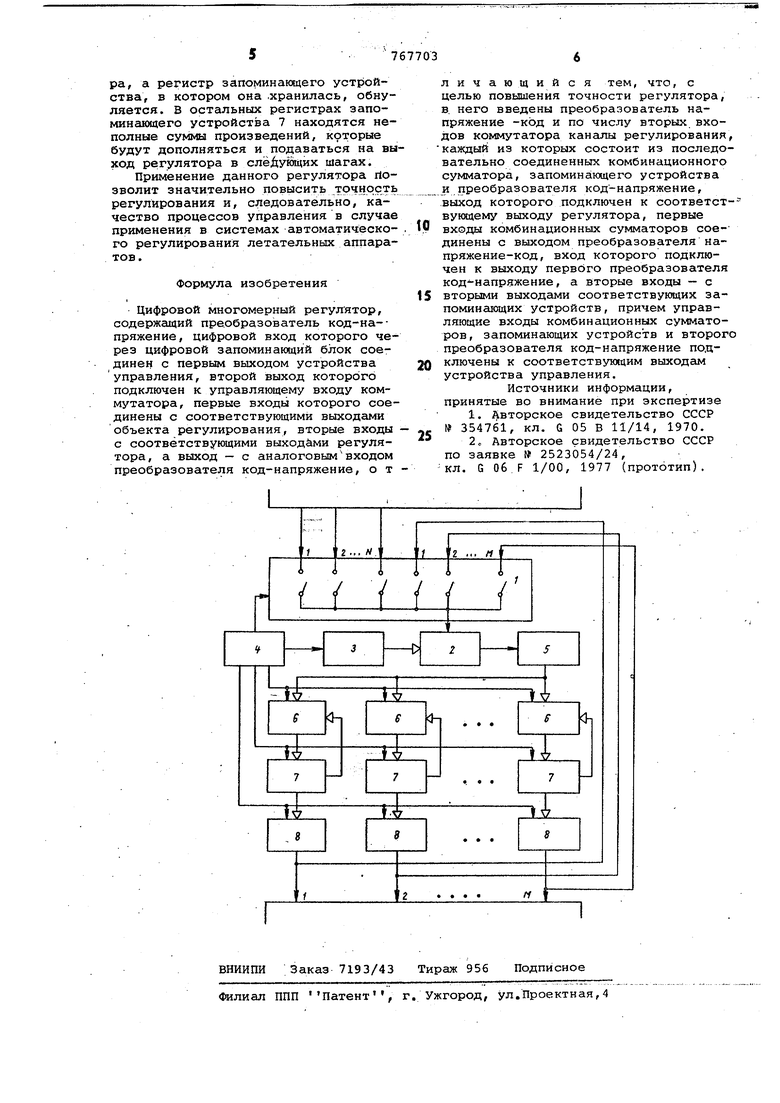

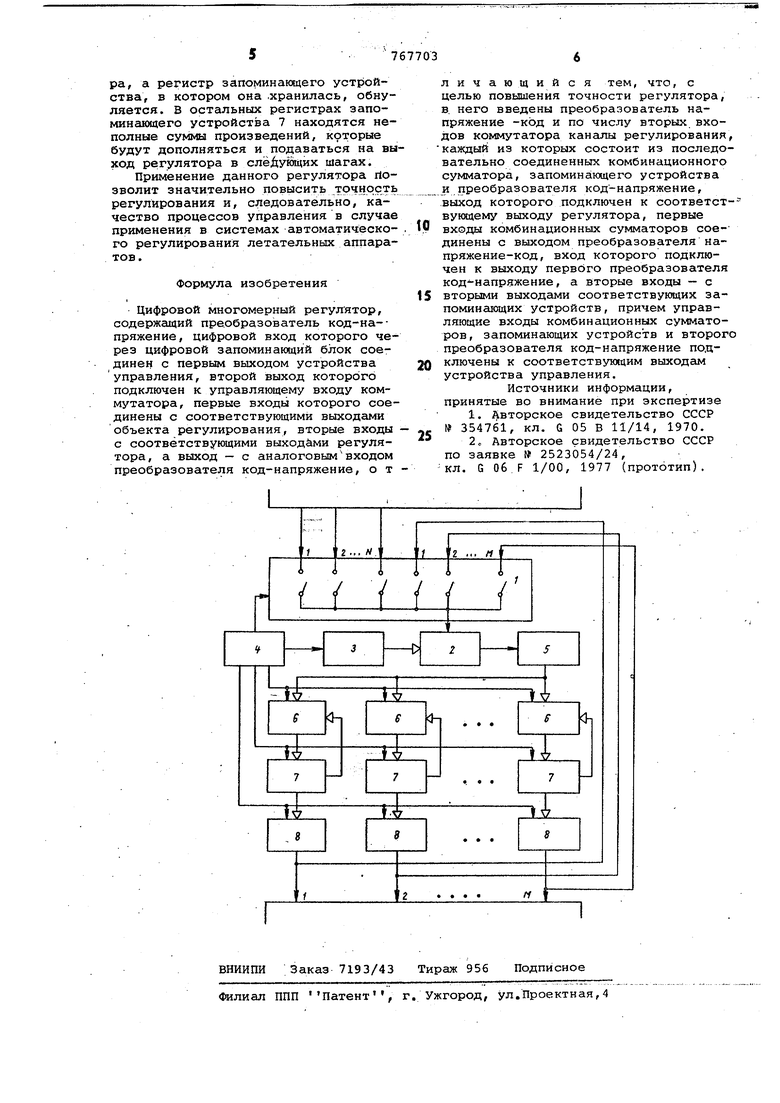

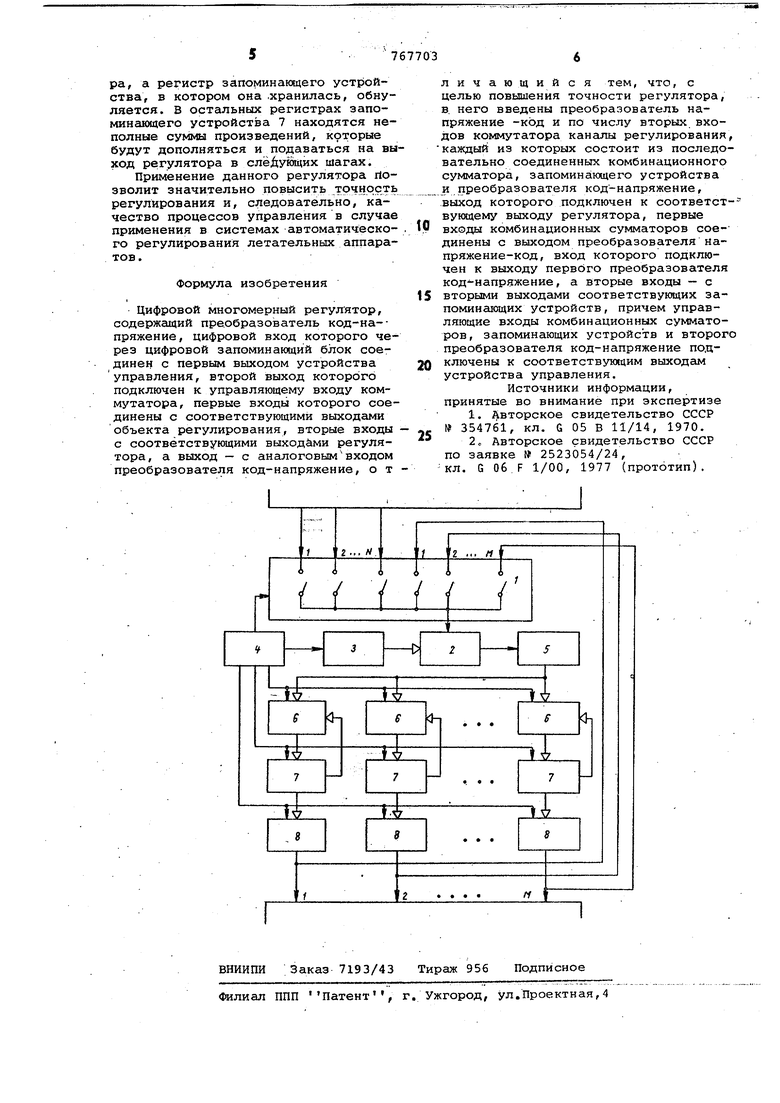

10 что в него введены преобразователь напряжение-код и по числу вторых входов коммутатора каналы регулирования, каждый из которых состит из последовательно соединенных комбинационного сумматора, запоминающего устройства и второго преобразователя коднапряжение, выход которого подключен, к соответствующему выходу регулятора. Первые входы комбинационных сумматоров соединены с выходом преобразователя напряжение-код, вход которого подключен к выходу первого преобразователя код-напряжение,.а вторые входы-со вторыми выходами соответствующих запоминающих устройств. Управляющие входы комбинационных сумматоров, запоминающих устройств и второго преобразователя код-напряжение подключень к соответствующим выходам устройства управления. Блок-ехема регулятора приведена на чертеже. . бн содержит коммутатор 1 входных -ё11гнгтов, первый преобразователь 2 кбд-напряжение, цифровой запоминающий блок 3, устройство 4 управления преобразователь 5 напряжение-код и в каждом канадце комбинационный сумматор 6, запоминающее устройство 7/ второй преобразователь 8 код-напряжение. . Работа регулятора происходит сле дующим образом. Синхронизация работы осуществляет ся устройством управления, связанньм со всеми блоками регулятора. Закон регулирования описывается следующим уравнением: ,.. „Л llr,ci)U)|. С1)рЫ) lIUnH - матрица управляющих воз . действий/ „Ci) L-i)pCd) ,,t) % матрица чи-tiV ,.Ci.) a) Ci) сел MNl4ll-4 MN MM размеромMX( -матрица входных координат цифрового многомерно го регуля тора;Ч 1 , i ; i j- число предыдущих значе ний управляющих воздей ствий, йсполЬзуёг х дл ,--...---..-вьгчиЬлёййй у г1Егавле;йия на текущем шаге; К - н оме р шагаг; : ;;: т М -ЧИСЛО выходных координ цифрового многомерного регулятора;. N -число входных координа цифрового многомерного регулятора. N переменных IIYll с выхода объе та управления и М переменных llull с вЩода1 1ШрбШ1еС ШШТ вй1ф1ге тора подаются на первые и вторые со ответственно входы коммутатора 1 вх ных сигналов, обра.зуя множество вхо нШ перемен них цйфзрШоШмЙогШефно тоТрёгулятораГ Кб1Шу а Й|Г ШЩ|ЙШ; сигналов последовательно, подключает переменные на ангшогбвый вхад перво преобразователя 2 кода-напряжение. цй фровой вход прёббразователя koSйапрййсё ние , подаются постоянные числ матрицы , из цифрового запоминакадего блока 3. В результате работы .преобразователя .на его выходе формируется величина, равная произведению входной переменной и постоянной из цифрового запоминающего блока. Полученная аналоговая величина переводится первым преобразователем 5 напряжение-код в цифровую, и далее процесс вычисления производится в цифровой форме. С выхода преобразователя 5 напряжение-код произведение засылается , например, в первый комбинационный сумматор б, где складывается с содержимым последнего регистра запоминающего устройства, состоящего из (Ч + 1) регистров, и засылается в первый регистр этого же запоминающего устройства. Затем содержи- . мое всех регистров запоминающего устройства сдвигается на один регистр вниз. Следующее произведение из той же входной переменной и следующей постоянной из цифрового запоминающего блока 3 складывается во втором комбинационном сумматоре с содержимым пЬследнего (-V + 1)-го регистра второго запоминающего устройства и засылается в первый регистр этого же запоминающего устройства. Затем содержимое всех регистров запоминающего устройства сдвигается на один регистр вниз. М-е произведение этой же входной величины подается на вход М-го сумматора, а (М + 1)-е произведение - опять на вход первого сумматора и т.д. . Таким образом, при действии первой переменной на входе первого преобразователя 2 код-напряжение он формирует М«Ч произведений с М-Ч постоянными из цифрового запоминающего блока 3 и через преобразователь 5 напряжение-код и комбинационные сумматоры 6 складывает их с содержимым Ч регистров каждого из М сдвигов запоминающего устройства. На этом завершается малый вычислительный цикл. Следующий малый вычислительный цикл начинается с появлением второй переменной на выходе коммута:тора входных сигналов. После того как произведения последней (М + М)-й входной величины на соответствующие постоянные из цифрового запоминающего блока.3 будут в соответствующих сумматорах б сложены с содержимым (Ч + 1)-х регистров запоминающих устройств 7 и записаны в первые регистрй этих устройств, закончится большой вычисли- , тельный цикл, т.е. закончится время одного из Ц шагов. В этот момент времени в одйом из регистров каждого сдвигового запоминающего устройства, нйхбдится Тэёлйчйна, равная управляющему воздействию данного канала на следующем (k + 1)-м шаге. Эта величина посту пает на второй преобразователь 8 кой- 1йапряжение и далее на выход цифрового, многомерного регулятоpa, a регистр запоминающего устройства, в котором она .хранилась, обнуляется. В остальных регистрах запоминающего устройства 7 находятся неполные суммы произведений, крторые будут дополняться и подаваться на выход регулятора в слёДу1отцих шагах.

Применение данного регулятора Позволит значительно повысить точность регулирования и, следовательно, качество процессов управления в случае применения в системах автоматического регулирования летательных аппаратов .

Формула изобретения

Цифровой многомерный регулятор, содержащий преобразователь код-на-пряжение, цифровой вход которого через цифровой запоминающий блок соединен с первым выходом устройства управления, второй выход которого подключен к управляющему входу коммутатора, первые входы которого соединены с соответствующими выходами объекта регулирования, вторые входы с соответствующими выходами регулятора, а выход - с аналоговым входом преобразователя код-напряжение, о т

личающийся тем, что, с целью повышения точности регулятора, в. него введены преобразователь напряжение -код и по числу вторых входов коммутатора каналы регулирования, каждый из которых состоит из последовательно соединенных комбинационного сумматора, запоминающего устройства и преобразователя код-напряжение, ,выход которого подключен к соответст-вующему выходу регулятора, первые входы комбинационных сумматоров соединены с выходом преобразователя напряжение-код, вход которого подключен к выходу первого преобразователя код- напряжение, а вторые входы - с

5 вторыми выходами соответствующих запоминающих устройств , причем управляющие входы комбинационных сумматоров, запоминающих устройств и второго преобразователя код-напряжение подключены к соответствующим выходам

0 устройства управления.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 354761, кл. G 05 В 11/14, 1970.

5

2 о Авторское свидетельство СССР по заявке № 2523054/24, кл. G Об F 1/00, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляющий процессор | 1977 |

|

SU711593A1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА ОБЪЕКТОВ ПО ОПТИЧЕСКОМУ ИЗОБРАЖЕНИЮ | 1971 |

|

SU294145A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1117655A1 |

| Цифровой регулятор | 1980 |

|

SU938255A1 |

| ПРОГРАММИРУЕМЫЙ ЦИФРОВОЙ ФИЛЬТР | 1992 |

|

RU2057364C1 |

| Многоканальный преобразователь аналог-код | 1977 |

|

SU744969A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Преобразователь активной мощности в цифровой код | 1989 |

|

SU1780033A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU1005300A1 |

Авторы

Даты

1980-09-30—Публикация

1978-11-20—Подача