Устройство относится к вычислительной технике и может найти применение в системах автоматического регулирования летательных аппаратов,

Известны и широко применяются управляющие процессоры,.имеющие в своем составе преобразователь напряжение-код, код-напряжекие

для приема аналоговых сигналов

от объекта и формирования выходных

аналоговых сигналов процессоров {.

Недостатком известных устройств является относительно низкое быстродействие.

Наиболее близким по технической сущности к предложенному изобретению является управляющий процессор, содержащий преобразователь кода в напряжение f цифровой вход которого подключен через цифровой запоминающий блок к первому выходу блока управления, а вход опорного напряжения .соединен с выходом коммутатора выходных сигналов, управляющий вход которого подсоединен ко второму выходу блока управления, одна группа входов коммутатора входных сигна-лов является группой входов процесеооа а другая группа входов подключена к группе выходов аналогового запоминающего блока и группе выходов процессора (2.

Недостатком такого управляющего процессора является то, что при вычислении алгоритма цифрового многомерного регулятора (1ШР) во-первых, необходимо записывать в память вход0ные переменные У,- (i-1,2. ,.. ,п) и управляющие воздействия IjCjr ,2,...,i), получаегФае в результате вычислений, так как они используются для вычислений в последующих тактах, во-вто-.

5 рых, при использовании управляющего процессора в качестве ШР резко увеличивается число пересыпок промежуточных результатов и, в-третьих, хранимые в памяти значения и

0

У

в каждом последующем такте

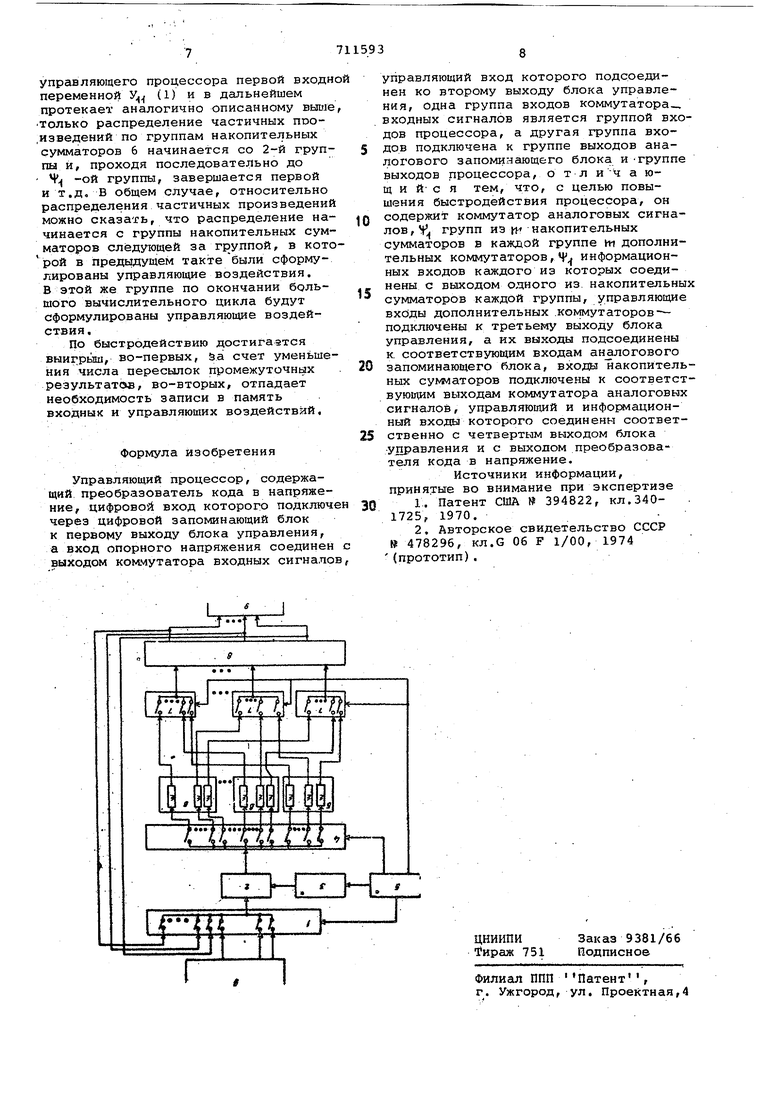

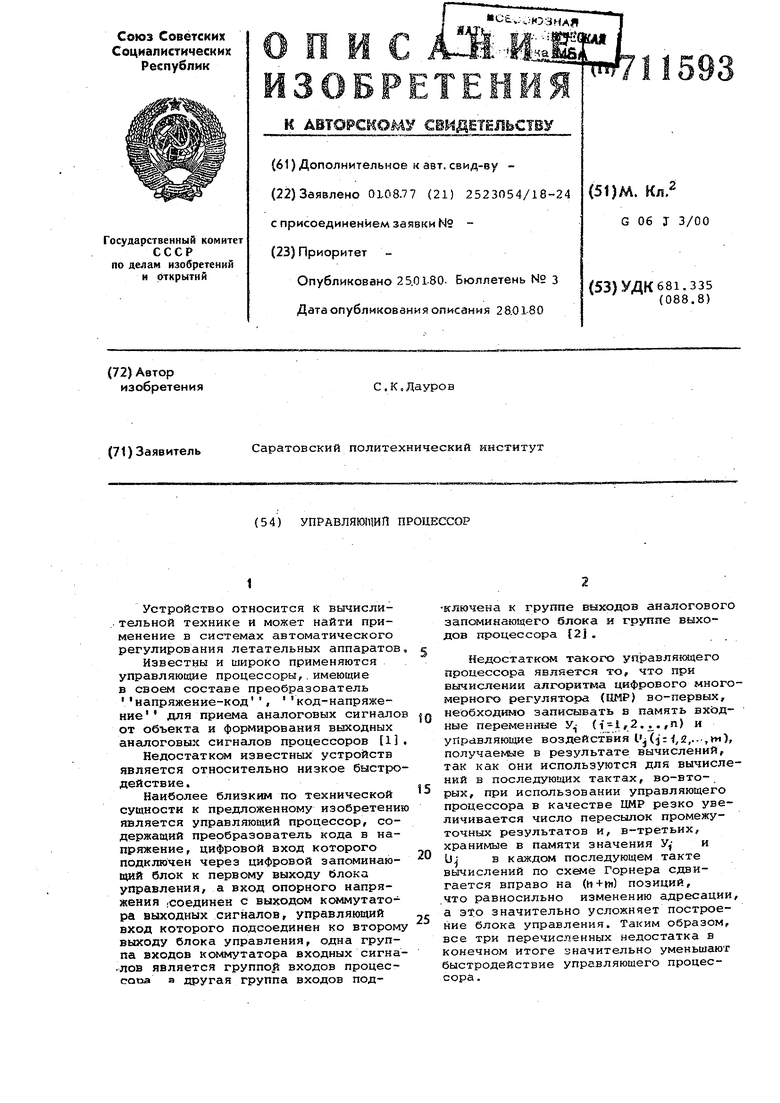

вычислений по схеме Горнера сдвигается вправо на (h+Ы позиций, что равносильно изменению адресации, а это значительно усложняет построе5ние блока управления. Таким образом, все три перечисленных недостатка в конечном итоге значительно уменьшают быстродействие управляющего процессора . Цель изобретения - повышение быстродействия процессора. Поставленная цель достигается тем, что процессор содержит коммутатор аналоговых сигналов. Ч групп из ш накопительных сумматоров в каждой группе ,№ дополнительных комму таторов , Ч информационных входов каждого из которых соединены с выходом одного из накопительных сумматоров каждой группы, управляющие входы дополнительных коммутаторов подключены к третьему выходу блока управления, а их выходы подсоединены к соответствующим входам аналогового запоминающего блока, входы накопительных сумматоров подключены к соответствующим выходам коммутатора аналоговых сигналов, управляющий и информационный входы которого соед нены соответственно fc четвертым выходом -блока управления и с выкодом .прео азователя кода в напряжение. На чертеже приведена схема управляющего процесссфа. Управляющий процессор содержит коммутатор входных сигналов 1, преовразователь кода-напряхсение - 2 цифровой запоминающий блок 3, коммутатор аналоговых сигиалов 4, блок управления 5, накопительные сумматоры б, дополнительные .коммутаторы 7, аналоговый запоминающий блок 8,объек управления 9. Управляющий процессор содержит щ еобразователь кода в напряжение 2 вход опорного напряжения которого соединен с выходом коммутатора входных сигналов 1, Цифровой вход преобразователя кода в напряжение 2 соединен с выходом цифрового запог/вяиающе.го блока 3. Выход преобразова теля кода в напряжевИ© 2 соедине со входом коммутатора аналоговых сиг налов 4. Выходы коммутатора аналого вых сигналов 4 соединены с соответствующими входами накопительных сумматоров ё, выходы которык в свою очередь соединены со входами яопоя нительных коммутаторов 7. Управляющ процессор содержит также аналоговый запоминающий блок 8, входы которого соединены с выходами дополнительных ко№4утаторов 7, а выходы аналоговог запоминающего блока соединены с Объектом управления 9 и со входами .коммутатора входных сигналов 1, Работа управляющего процессора организуется блоком управления 5, имеющим связи с коммутатором аналоговых сигналов, с управляющими вхо дами дополнительных коммутаторов 7, с коммутатором входных сигналов 1 и с цифровым запоминающим блоком 3. Работа управляющего процессора организована следующим образом, N переменных 11 У|| с выхода объекта . управления и М управляющих воздействий//и1/ с выхода управляющего процессора Подается на вход коммутатора входных сигналов 1, образуя множество входных переменных управляющего процессора. Коммутатор входных сигналов 1 последовательно подключает входные переменные на аналоговый вход преобразоватбля кода в напряжение 2 (вход опорного напряжения), на цифровой вход преобразователя кода в напряжение 2 подаются постоянные числа матрицы J(Ri р (з) 1143 цифрового запоминающего блока 3. В результате преобразования на выходе преобразователя 2 формируется величина, равная произведению входной переменной и постоянной из цифрового запоминающего блока. Полученная аналоговая величина посредством.коммутатора аналоговых сигналов 4 засылается, например, в первый накопительный сумматор первой группы сумматоров б, следующее частичное произведение той же входной переменной и следующей постоянной из цифрового запоминающего блока 3, засылается во второй накопительный сумматор 6 первой группы сумматоров и т.д. Таким образом, при действии3 первой переменной На входе преобразователя кода в напряжение 2, преобразователь формирует Mf частичных произведений с МЧ постоянными из цифрового запоминающего устройства и засылает их в МЧ накопительных сумматоров б. На этом завершается первый малый вычислительный цикл, Следующий малый вычислительный цикл начинается с появлением следующей входной переменной на выходе коммутатора входных сигналов 1, и вычислительный процессповторяется. После того как процедура малого вычислительного цикла будет проведена со всеми входными переменными, что означает завершение большого вычислительного цикла, в одной из групп накопительных сумматоров 6, например в первой, формируется М управляющих воздействий, которые с помощью дополнительных коммутаторов 7 подаются на входы аналогового запоминающего блока 8 и далее на управляющие входы объекта 9 и на входы коммутатора входных сигналов 1. Следующий большой.вычислительный цикл начинается подачей первой ВХОДНОЙ переменной на .аналоговый вход преобразователя 2, только распределение частичных произведений начинается со 2-ой группы, Т.е.в об.щем случае со следующей За группой, в которой в предыдущем большом вычислительном цикле были сформированы управляющие воздействия. Для синхронизации и управления работой управляемого процессора использован блок управления 5, пред тавляющий собой, например, микропрограммный автомат. Пример 1. В управляющем процессоре вычисляются алгоритмй ЦМР летательных аппаратов вида: 11-- ё lllb 11 1 Р 1||1и ) dгде II и матрица управляющих воздействий или вход координат ЦМР на дан шаге К, размеров М х l|,jCK.-i)j| матрица входных коорд нат ЦМР на (К-1)-ом шаге, размером М х 1 ни И - матрица выходных коор динат ЦМР на (K-J) ш ге, размером М х 1 : - 1-тая матрица чисел, размером MXN; -j-тая матрица, чисел размером М х М; - количество используемых в алгоритме преды значений У (К-i); -количество используем в алгоритме предыду1аи значений и (K--f) г К - текущий шаг (такт); ,2, Для удобства реализации алгорит ЦМР на управляющем процессоре к правой части алгоритма IIMP прибавляем сумму произведений вида: 1|Р -«Ч11 и к-(%и)1|....Ч|11и1к-ч.. ™.||p ||j|piv 4,;||pc.0||. нулевые матрицы размером М х Тогда аглоритм ЦМР можно записать в виде: llUiKlUs llR P l||pt - l i-.:. tniKK-illl ,..,«,р,...рш }p(lc-i HuiK--j bli) pli) pU) JAM CK-i) ,lK-i) л (К-р Распишем алгоритм по текущим та там, начиная с нулевого момента вр мени. lluu i| l|T P imSlL iuTHi--ii.p iiiisii n raii 1R 11-|1R P -1||JJ VV,11. -Ih lliruSSIh-lh iai lluwMf-p,P 4i|pih. IIB;a-HI« . -4IIISr Как видно из последнего выражения измеренные в момент времени K-i входные координаты и вычисленные в предыдущем такте управляющие воздействия используются в вычислительном процессе до (Ч )-го такта, входные переменные в момент времени К-2 и управляющие воздействия, вычисленные в предьлдущем такте, используются до (V.-t--{ )-го такта .и т,д. Таким образом вычислительный процесс, в управлении процессора может быть организован так, что при поступлении на вход управляющего процессора первой входной переменной, например, У (0) можно сформировать М частичных произведений У (о) с элементами 1-го столбца матрицы ptflПолученные частичные произведения засылаются в первую группу М накопительных сумматоров ь, частичг ые произведения с элементами первого столбца матрицы IIRi, . засылаются во вторую группу накопительных сумматоров 6 и т.д. Частичные произведения с элементами первого столбца матрицьт 1К р | засылаются в 4 -ю группу М накопительных сумматоров б и на этом завершается малый вычислительный цикл. На вход управляющего процессора поступает вторая входная переменная y,j (0), которая участвует в формировании частичных произведений йо вторыми столбцами выше перечисленных матриц. Расгчэеделение произведений по группам накопительных сумматоров б происходит в той же последовательности, что и в предыдущем вычислительном цикле. В накопительных су маторах Ь осуществляется процесс суммирования частичных произведений, полученных в малых вычислительных циклах. Подобная вычислительная процедура проводится со всеми входными переменными и после завершения малого вычислительного цикла с последней переменной У (0) заканчивается большой вычислительный цикл, в результате которой в 1-й группе М накопительных суматоров сформированы М управляющих оздействий, которые выводятся на ыход управляющего процессора и даее на управляющие входы.объекта. Следующий большой вычислительный цикл начинается с подачи на вход

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой многомерный регулятор | 1978 |

|

SU767703A1 |

| Многоканальный аналого-цифровой процессор | 1983 |

|

SU1120375A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ УПРАВЛЯЮЩИХ ВОЗДЕЙСТВИЙ ДЛЯ ОБЕСПЕЧЕНИЯ УСТОЙЧИВОЙ РАБОТЫ СЛОЖНЫХ ТЕХНИЧЕСКИХ СИСТЕМ | 2011 |

|

RU2475828C1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для преобразования координат | 1980 |

|

SU898426A1 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

| СПОСОБ И УСТРОЙСТВО КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ | 2007 |

|

RU2352060C1 |

| Цифровой вольтметр среднеквадратического значения переменного напряжения | 1988 |

|

SU1652933A1 |

| Инкрементный умножитель аналоговых сигналов | 1983 |

|

SU1113820A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ | 1968 |

|

SU209032A1 |

Авторы

Даты

1980-01-25—Публикация

1977-08-01—Подача