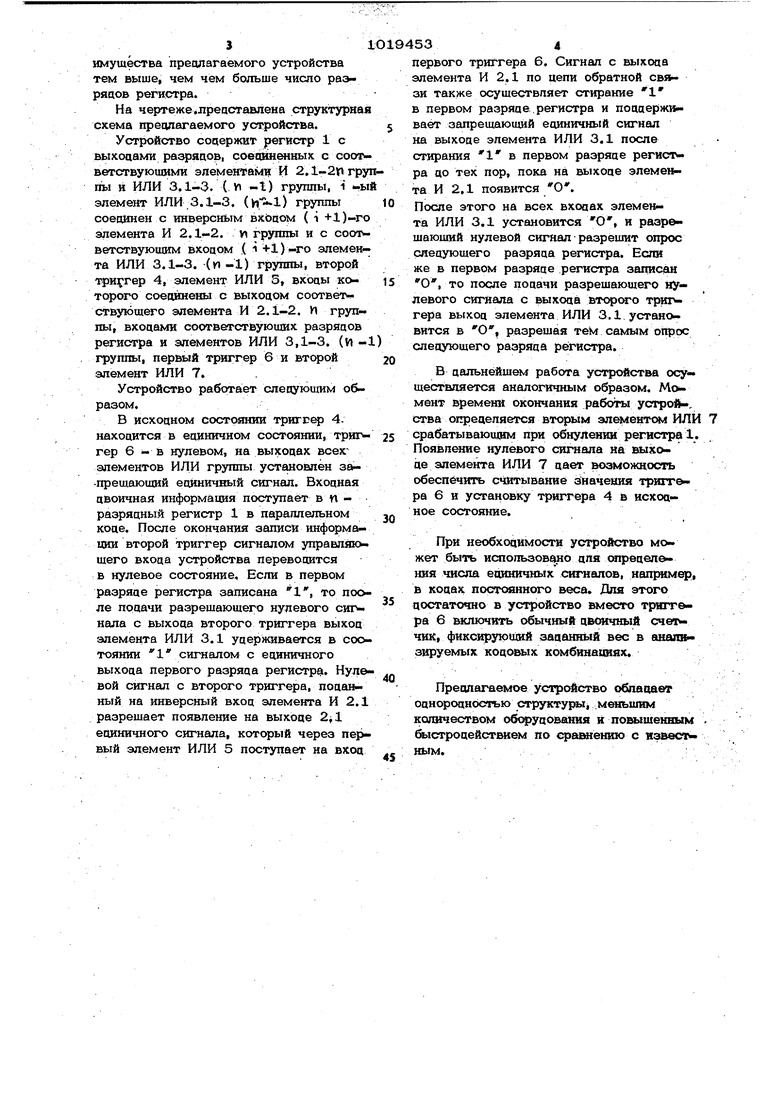

Изобретение относится к вычисл тельной тегшнке и может быть использо вано ОЛЯ проверки на четность или в цекосмрующих устройствах для опрецепения веса в кодовых комбинациях корректирующих коцов, принимаемых в пара лельном коде. Известно асинхронное устройство ОЛЯ определения четности информации, содержащее регистр, элемент ИЛИ, три1 гер со счетным входом, пороговый блок группу элементов ИЛИ и группу элемен тов И 1 . Недостаток этого устройства заключ ся в довольно большом объеме оборудования порогового блока, который везрас ет с увеличением числа разрядов регистра. Тактовью импульсы, опрашиваю щие состояние регистра, проходят по сравнительно длинной цепочке последовательно соединенных элементов И, вносящих задержку особенно при больших значениях разрядности информацион ного кода и высокой частоте поступления информации. Без дополнительного оборудования невозможен подсчет числа еаиниц в регистре. Наиболее близким техническим р&шением к предлагаемому является устройство Ш1Я определения четности информации, содержащее регистр.: элементы ИЛИ, счетный триггер, группу, элементов И группу элементов ИЛИ, причем выход каждого элемента И груп пы соединен с нулевым входом соответ ствующего разряда регистра и с соот. ветствукзщим входом элемента ИЛИ. Вы ход кажаого -i го элемента И группы соединен с соответствующим входом всех эл(гментов ИЛИ группы от 1 -го до ( я ..1)-го 2 , Недостатком этого устройства я&ляется то, что число входов элементов ИЛИ группы возрастает по закону арифметической прогрессии и приводит к увеличению количества и типов интегральных микросхем. Из-за ограничения на количество входов микросхем при увеличешш разрядности регистра возникает необходимость выполнения элементов группы ИЛИ в виде каскацного со&динения микросхем, что увеличивает количество оборудования и снижает быстродействие. При увеличении разряцнести регистра возрастает нагрузка элементов И группы, что вынуждает при h+1 ni (где VI -длина информационного кода, m - нагрузочная способность элемента И группы) дублировать элементы И группы. Это также увеличивает количество оборудования. В этом устройстве независимо от содержимого разряда регистра (1 или О,), сигнал проходит по одинаковой цепи ИЛИ-И, что снижает быстродейст. вие. Цель изобретения - упрощение уст ройства и повышение быстродействия. Поставленная цель достигается тем, что в устройство для определения чет ности информации, содержащее регистр, первый и второй элементы ИЛИ, первый и второй триггеры, группу элементов И и группу элементов ИЛИ, причем единичные входы каждого разряда регистра образуют группу входов устройства, выход первого элемента ИЛИ соединен со счетным входом первого триггера, выход которого является выходом уст ройства, единичный выход каждого разряда регистра соединен с соответ ствующим входом второго элемента ИЛИ, выход которого соединен с единичным входом второго триггера и с управляю щим входом первого триггера, нулевой вхоц второго триггера является управл5йОщнм входом устройства, единичный выход каждого разряда регистра соединен с первым входом соответствующего эл&мента И группы, а выход каждого зломента И группы соединен с соответствующим входом первого элемента ИЛИ, с нулевым входом соответствующего разряда регистра и входом соответствук. щего элемента ИЛИ группы нулевой выход второго триггера соединен с соответствующими входами всех элементов ИЛИ группы и с инверсным входом первого элемента И группы, выход i -го элемента ИЛИ группы, где (и-1), а и -количество . разрядов регистра, соесшкен с шшерсным входом ( +1)-го элемента И группы, выход каждого 1 -го элемента ИЛИ группы, кроме ( h -1)-го соединен с соответствующим входом ( ( 1 +1) - го элемента ИЛИ группы, единичный выход i -го разряда регистра соединен с соответствующим входом i -го элемента ИЛИ группы. В связи с тем, что число входов элементов ИЛИ группы не возрастает по закону арифметической прогрессии, структура устройства приобретает однородность и упрощается, а быстродействие йовышается из-за сокращения цяины логических цепей опроса состояний нулевых разрядов, регистра. Преимущества преопагаемого устройства тем выше, чем чем больше число разрядов регистра. На чертеже лреаставпена структурная схема предлагаемого устройства. Устройство содержит регистр 1 с выхоцами разрядов, соеофшенных с соот ветствующими элементами И 2,1-21П гру пы и ИЛИ 3.1-3. ( VI -t) группы, 1 -ы элемент ИЛИ 3.1-3. () группы соединен с инверсным входом ( i +1)-го элемента И 2.1-2. м группы и с соот ветствующим входом ( i +1) -го элемента ИЛИ 3.1-3. (и-) группы, второй триггер 4, элемент ИЛИ 3, входы которого соединены с выходом cooTBeiv ствующего элемента И 2.1-2. И группы, входами соответствуюишх разрядов регистра и элементов ИЛИ 3,1-3. (и группы, первый триггер 6 и второй элемент ИЛИ 7.. Устройство работает следующим образом. В исходном состоянии трнгЕ 4. находится в единичном состоянии, 6 - в нулевом, на выходах всехэлементов ИЛИ группы установлен запрещаюишй единичный сигнал. Входная двоичная информация поступает в п разрядный регистр 1 в параллельном коде. После окончания записи информации второй триггер сигналом управляющего входа устройства переводится в нулевое состояние. Если в первом разряде регистра записана 1, то пооле подачи разрешающего нулевого сигнала с выхода второго триггера выход элемента ИЛИ 3.1 удерживается в состоянии 1 сигналом с единичного выхода первого разряда регистру. Нулевой сигнал с второго триггера, поданный на инверсный вход элемента И 2.1 разрешает появление на выходе 2Д единичного сигнала, который через первый элемент ИЛИ 5 поступает на вход первого триггера 6. Сигнал с выхода элемента И 2.1 по цепи обратной свяг зи также осуществляет стирание 1 в первом разряде регистра и поддерживает запрещающий единичный сигнал на выходе элемента ИЛИ 3.1 после стирания в первом разряде регистр ра до тех пор, пока на элемента И 2,1 появится О. После этого на всех входах элемента ИЛИ 3.1 установится О, и разр&шаюший нулевой сигнал разрешит опрос следующего разряда регистра. Если асе в первом разряде регистра запис|ан О, то после подачи разрешающего нулевого сигнала с выхода вторсяго триг гера выход элемента ИЛИ 3.1 установится в О, разрешая тем самым опрос следующего разряда регистра. В дальнейшем работа устройства осуществляется аналогичным образом. Мо мент времени окончания работы устрой-, ства определяется вторым элементом ИЛИ 7 срабатывающим при обнулении регистра 1. Появление нулевого сигнала на выходе элемента ИЛИ 7 дает возможность обеспечить считывание значения триггера 6 и установку триггера 4 в исходное состояние. При необходимости устройство может быть использов о для сшрздел ния числа единичных сигналов, нап1Н1мер, в кодах постоянного веса. Для этого достаточно в устройство вместо триггера 6 включить обычный двоичный счет чик, фиксируюийий заданный вес в анализируемых кодовых комбинавсиях. Предлагаемое устройство обладает однородностью структуры, .меньшим количеством оборудования к повышенволм . ба 1стродейстш{ем по сраш1ению с известным.

i

ф «

1

,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля 2-кода Фибоначчи | 1988 |

|

SU1662009A1 |

| Устройство для контроля параллельного кода на четность | 1983 |

|

SU1103239A1 |

| Буферное запоминающее устройство | 1980 |

|

SU858109A1 |

| Мультимикропрограммное устройство управления | 1985 |

|

SU1256026A1 |

| Однородная вычислительная среда | 1974 |

|

SU618738A1 |

| Устройство для деления | 1981 |

|

SU1051535A1 |

| Устройство для контроля параллельного кода на четность | 1983 |

|

SU1100626A1 |

| Устройство для контроля параллельного кода на четность | 1979 |

|

SU883910A1 |

| Сигнатурный анализатор | 1987 |

|

SU1531098A1 |

| Устройство для контроля параллельного двоичного кода на четность | 1981 |

|

SU999057A1 |

УСТРОЙСТВО ДЛЯ ОПРЕДБЛЕНИЯ ЧЕТНОСТИ ИНФОРМАЦИИ, соафжащбе рвпкпгр, nefmiift в второй аа мёпггЫ ИЛИ, первый я вторс Г1штЕрь1, j группу апементов И группу ИЛИ, пртпсм еяявтш е входы хая цого рваряоа релкяра об|равуюг грушу вхоаов устройства, мыхоц первого эявмевн те ИЛИ соесшвен со сметным вхоаом первого триггера, выхоц которого яв« мшвтся вых;оЕЕс « ycrpoflcrata, ешоэтяый выхов к 1жабп раз{ЖЕ|а регистра соеш не с соогвотсугоуюпшм вхощомг BTopidro ИЛИ, выхоц которого coeoifiieR с ешшвшодм вхоаом второго трэттера я у1фааляюищм вхоаом первого трнггё- paj ууя&мЛ вхоа Трвгг(фа я яяется у1фавлякшшм вхоаом устройства, еютвчвый кыход квкаого раоряпа регист ра соейвиен с 1Юрвым входом соогвет ству1гаюч} И группы, а выхоц кажаого элемпгга И rffymat соеовнен с соответстцгкмикм вхоцом первого эц ммЕта ИЛИ, : вулмдам tatow соответи. ствунжюто разрхаа рогкстра в входом соогвётстфующего алемднта ИЛИ грул- ом, иул9кЛ выхоа второго .1рвгг«ра сОд ошен с сОонФетствуюшнмв вхоаамв всех ап«мевт « ИЛИ группы в с BXOQOM первого элемента И грушш, выхоа 4 -го элемента ИЛИ груцаы (гае (и..1), а щ -коюяество рафяаоЁ регистра) соесжвев с вйвв1Х BbtM кодом (Ч4-1)нго пе} |Гента Игруп иы, о т л в ч а ю ш е ее тш, «сто, с ашЕЬю ущх ще«вя устройства, выхоп каждого i-i-ro 9пви&пл ШМ группы, кроме ( i «iO ro coeeiflaReB о codinMiw ст)Едпощдал вхоаом (| апёмента ИЛИ грушпд, еавиичш 1й ш1хо(| квжаого i нго : раврясса регвстра сое1Швея с роотвепу : OTByiotsHM вхоаом алшдента ИПИ , группы.сл 60

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Асинхронное устройство для определения четности информации | 1978 |

|

SU767765A2 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для определения четности информации | 1978 |

|

SU767766A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-05-23—Публикация

1981-11-13—Подача