1

1 зобретение относится к автоматик и вычислительной технике и может быть использовано при реализации средств тестового диагностирования блоков дискретной техники.

Целью изобретения является повы- 1ление достоверности контроля.

На фиг. 1 приведена функциональная схема предлагаемого устройства; на фиг. 2 - временная диаграмма работы генератора тактовых импульсов .

Устройство для контроля схем сравнения (фиг. 1) содержит контролируемую схему 1 сравнения, блок памяти 2, регистр 3 адреса, регистр 4 микрокоманд, регистры 5,6 сдвига, триггер 7, генератор 8 тактовых импульсов, мультиплексор 9, элемент Ю срапЕгенпя, блок 11 анализа, со- деряшщий элемент И-ИЛИ НЕ 12, элементы ИЛИ 13, 14; элементы И 15, 16, элементы tl 17, 18, элементы ШШ 19, 20, пход.. пуска 21, выход ошибки устройства 22, первьй-четвертый выходы 23-26, блока памяти, первьш-де- вят)1й выходы 27-35 регистра 4 микрокоманд, первьй-третий выходы 36- 33 схемы сравнения, выходы 39-41 старшего разряда регистра 5, младшего и старшего разрядов регистра 6 соответственно, выходы 42-44 генератора 3 тактовых импульсов (выходы поля адреса блока памяти 23, признака модификации адреса 24, признака следующего адреса микрокоманды 25, выход 26 поля управления, выход 27 признака сброса первого регистра сдвига, выход 28 признака разрешени выход 29 признака сравнения, выход 30 признака сброса второго регистра сдвига, выход 31 признака разрешения, выход 32 признака несравнения, выход 33 признака анализа, выходы признака кода логических условий 34, признака конца контроля 35, выход Неравно 36, выход Равно 37, выход Неравно 38, выходы старшего разряда, выходы младшего и . старших разрядов регистров 5 и 6, соответственно 39-41, выходы 42,44 генератора тактовых импульсов Устройство работает следующим образом.

В исходном состоянии все элементы памяти устройства находятся в нулевом состоянии. На фиг. 1 цепи установки в исходное состояние усло но не показаны.

83862

Устройство осуществляет проверку схемы 1 сравнения последовательно в следующих режимах.

Первьй режим. На первый вход

схемы 1 подается число А О, ас помощью регистра 6 сдвига последовательно формируются и подаются на второй вход схемы 1 числа В-содержащие единицу только в одном разря0 де от до .В результате выполнения этого режима проверяется работоспособпость и правильность реакции схемы 1 на единичный сигнал по всем входам числа В .

s Второй режим. На вход В схемы 1 задается число, содержащее единицу в старшем разряде ( DV,. 1), а на вход А последовательно пода- , ются числа, содержащие единицу

0 в разрядах a,.,.,c. После этого на вход В задается число с -1, а на вход А последовательно задаются числа, содержащие единицу в разрядах 1, cia, . . . , (и так далее

5 по b 1 1 и ). В результате выполнения этого режима проверяется правильность формирования схемой 1 сигнала А В для всех входов , i 1 п и правильность

0 формирования схемой 1 сигнала для всех пар разрядов Bj , Q ; , i 1, п, aj 1, i. Это позволяет эффективно проверить работоспособность цепей блокировки младших разрядов старшими по всем входам схемы 1.

Третий режим. Этот режим полностью эквивалентен первому режиму. На вход схемы 1 подается число В - О, а на вход Д последовательно зада- ются числа, содержащие о т- , -i- 1,...,Q(-,- 1. В результате выполнения этого режима проверяется работоспособность всех цепей формирования сигнала А В схемы 1 по всем входам числа А .

Четвертый режим. Этот режим эквивалентен второму режиму контроля. Отличие состоит в том, что для каждого числа А , содержащего одну единицу (а, 1, а. 1,..., а -1), последовательно формируются числа В, содержащие единицу в разрядах bj, j 1, i, если а| 1. Благодаря выполнению этого режима проверяется работоспособность цепей формирования сигнала А В схемой 1 и работоспособность цепей блокировки старшими разрядами младших при формировании сигнала по всем входам схемы 1

5

5

0

5

Последовательный контроль схемы 1 с помощью предлагаемого устройства обеспечивает существенное повьшение достоверности результатов контроля при высоком быстродействии за счет реализации минимальной совокупности проверок, обеспечивающих контроль всех цепей формирования сигналов , А ,а также цепей блокировки младших разрядов старшими.

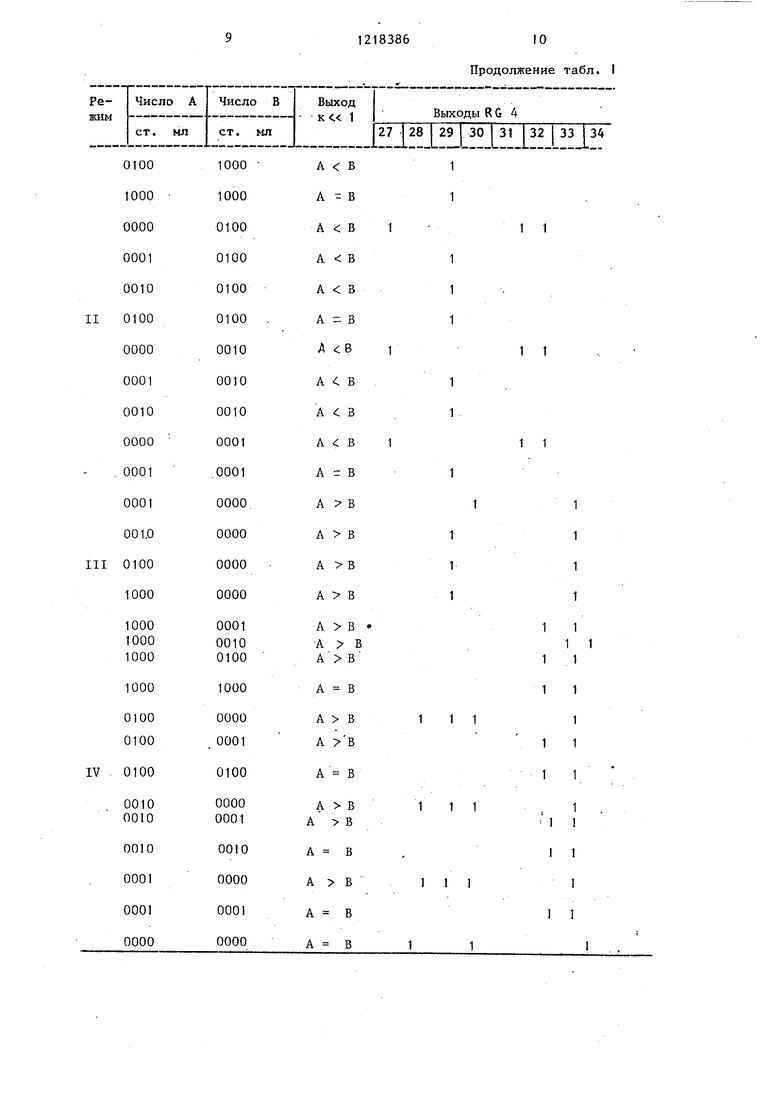

В табл. 1 представлена таблица кодов чисел А и В , последовательно подаваемых на входы схемы 1, при реализации первого-четвертого режимов контроля (при п 4).

Рассмотрим функционирование устроства в перечисленных режимах.

По сигналу Пуск, поступающему на вход 21 устройства, триггер 7 устанавливается в единичное состояние и запускает генератор 8 тактовых импульсов, который начинает формировать последовательности синхроимпульсов .

На выходе 35 регистра 4 микрокоманд присутствует нулевой код, поэтому выходной сигнал мультиплексора 9 равен единице, и элемент И 18 открыт . Первьш синхроимпульс с выхода 42 генератора 8 тактовых импульсов поступает на шестой вход блока 11 анализа, который осуществляет контроль правильности работы схемы 1 на числах Л В 0. Одновременно этот синхроимпульс проходит на вход синхронизации регистра 3 адрес по его заднему фронту в регистр 3 адреса записывается адрес первой микрокоманды, который хранится в ячейке с нулевым адресом. В результте этого первая микрокоманда считывается из блока памяти 2. По заднему фронту второго синхроимпульса с выхода 43 генератора 8 тактовых импульсов ее микрооперационная част и код проверяемого логического условия записываются в регистр 4 микрокоманд. В результате этого устройство переходит в первьй режим контроля.

На выходе 32 регистра 4 микрокоманд появляется единичный сигнал, которьй открывает элемент И 16, на который последовательно подаются импульсы с выхода 44 генератора 8 тактовых импульсов. В результате этого в младший разряд регистра 6 сдвига записывается единица, котора

25

218386

последовательно сдвигается в сторону старшего разряда. При каждом положении единицы в регистре 6 сдвига на шестой вход блока 11 анализа

5 подается синхроимпульс с выхода 42 генератора 8 тактовых импульсов, который следует каждьй раз после импульса на выходе 44 генератора 8 тактовых импульсов (см. фиг. 2). В

10 результате этого осуществляется проверка исправности схемы 1 в первом режиме контроля по всем разрядам входа В . Код логических условий, поступающий на мультиплексор 9, ключает выход 41 регистра 6 сдвига к ВХОДУ) элемента И 18. Поэтому до тех пор, пока единица в регистре 6 не достигнет его старшего разряда, в регистр 3 адреса не запишется адрес

20 следующей микрокоманды..

После появления единицы в старшем разряде регистра 6 сдвига элемент И 17 откроется, и очередной импульс с выхода 42 генератора 8 тактовых импульсов запишет в регистр 3 адреса, адрес следующей микрокоманды, а ее операционная часть с кодом логических условий по синхроимпульсу с выхода 43 генератора 8 тактовых импульсов запишется в регистр 4 микрокоманд. В результате этого устройство перейдет во второй режим контроля.

На выходе 29 регистра 4 микрокоманд появится единичный сигнал, который откроет элемент И 15, ив младший разряд регистра 5 сдвига запишется единица, которая будет последовательно сдвигаться в сторону старшего разряда до тех пор, пока не достигнет его (А В). В каждом такте по синхроимпульсу с выхода 42 генератора 8 тактовых импульсов будет производиться контроль правильности работы схемы 1 блоком 11 анализа. Код логического условия настроит мультиплексор 9 таким образом, что к входу элемента И 18 будет подключен элемент 10 сравнения. Поэтому очередной тактовый импульс пройдет

50 на вход синхронизации регистра 3 только при кодах чисел А. В 1000. ...0. По этому Импульсу из блока памяти 2 будет считана очередная микрокоманда, и на выходах 27,

55 31, 32 регистра 4 микрокоманд появятся единичные сигналы. По этим сигналам регистр 5 сдвига сбросится в ноль, а в регистре 6 сдвига

30

35

40

45

единица из старшего (п го) разряда сдвинется в (п - 1)-й разряд (обратный сдвиг). После этого по следующей паре синхроимпульсов с вы- хода 42 и 43 генератора 8 тактовых импульсов будет считана очередная микрокоманда, на выходе 29 регистра 4 микрокоманд появится единичный сигнал, и цикл проверки схемы 1 повторится до совпадения кодов А 6 010..,0.

При А В в регистр 4 микрокоманд будет считана микрокоманда проверки логического условия Ь 1; для чего с помощью мультиплексора 9 к входу элемента И 18 будет подключе выход триггера 7 (константа 1), а на выходе 24 блока памяти 2 будет сформирован единичный сигнал, которьй откроет элемент И 17, разрешающий модификацию адреса значением младшег разряда регистра 6 (выход 40). При bi О модификации не будет, в регистр 4 микрокоманд вновь будет счи- тана микрокоманда сброса- регистра 5 и сдвига на единицу вправо содержимого регистра б сдвига, и цикл работы устройства повторится. Так будет продолжаться до тех пор, пока не будет получено равенство А -6

00001, т.е. единица в регистре

6 сдвига не достигнет младшего разряда. После этого произойдет модификация адреса следующей микрокоманды единичным значением младшего разряда регистра б сдвига, и устройство вьй- дет из цикла (см. фиг. 1). В регистр

4микрокоманд будет считана очередна микрокоманда сброса регистра б сдвига, а затем микрокоманда сдвига еди ницы в регистре 5 сдвига. Устройство перейдет в третий режим контроля.

Работа устройства контроля в третьем и четвертом, режимах аналогична его работе в первом и втором режимах соответственно. Отличие состоит в том, что функции регистра

5сдвига в этих режимах вьтолняет регистр б сдвига и наоборот соответственно микрокоманды, считываемые в этих режимах, содержат микрооперации, инверсные предьщущим.

По окончании четвертого режима Контроля, который будет также характеризоваться условием А В О 0. ..01, в регистр 4 микрокоманд бу- дет считана микрокоманда, содержащая микрооперацию конец работы. На выходе 34 регистра 4 микрокоманд появится единичный сигнал, который, пройдя через элемент ПЛИ 19, возвратит триггер 7 Б исходное состояние, и работа устройства прекратится.

Если в каком-либо такте работы устройства блок 11 анализа обнаружит неправильную работу контролируемой схемы 1 сравнения, на его выходе появится единичный сигнал, который остановит работу устройства,(сбросит триггер 7) и пройдет на выход 22 устройства, сигнализируя о неправильном функционировании схемы 1.

В табл. 2 приведен один из возможных вариантов прошивки блока памяти 2 для реализации всех четырех режимов контроля.

Как следует из табл. 2 содержимое ячеек памяти блока 2 не зависит от разрядности проверяемых схем 1 и занимает весьма небольшой объем памяти.

Формула изобретения

Устройство для контроля схем сравнения, содержащее контролируемую схему сравнения, первый и второй регистры сдвига, триггеры, генератор тактовых импульсов yi блок анализа, причем вход пуска устройства соединен с единичным входом триггера, выход которого соединен с входом пуска генератора тактовых импульсов, группы выходов первого и второго регистров сдвига соединены с первой и второй группами информационных входов контролируемой схемы сравнени выход Равно и два выхода Неравно которой соединены с первым, вторым и третьим входами блока анализа соответственно выход которого является выходом ошибки устройства, о т- л и ч а ю щ е е с я тем, что, с целью повьппения достоверности контроля (, оно содержит блок памяти, регистр адреса, регистр микрокоманд, мультиплексор, элемент сравнения, первьй и второй элементы ИЛИ-НЕ, первый, второй, третий и четвертьй элементы И, первый и второй элементы ИЛИ, причем выходы признаков сброса регистра микрокоманд соединены с входами сброса первого и второго регистров сдвига соответственно, выходы признаков разрешения регистра микрокоманд соединены с входами

записи первого и второго регистров сдвига соответственно, группы выходо первого и второго регистров сдвига за исключением выходов младших разрядов, соединены с первой и второй группами информационных входов элемента сравнения и с группами входов первого к второго элементов ИЛИ-НЁ соответственно, выход признака сравнения регистра микрокоманд соединен с первым входом первого элемента И, выход которого соединен с входом синхронизации первого регистра сдвига, выход признака несравнения регистра микрокоманд соединен с первым входом второго элемента И, выход которого соединен с входом синхронизации второго регистра сдвига, информационные входы первого и второго регистров сдвига соединены с выходами первого и второго элементов ШШ-НЕ соответственно первый выход генератора тактовых импульсов соединен с входом синхронизации регистра микрокоманд,второй выход генератора тактовых импульсов соединен с вторыми входами первого и второго элементов И, выходы поля адреса блока памяти и выход первого элемента ИЛИ соединены с информационными входами регистра адрес вход синхронизации которого соединен с выходом третьего элемента И, выход адреса соединены с адресными входами блока памяти, выходы поля управле- НИН которого соединены с информационными входами регистра микроко

0000 0001 0010 0100 1000

0001 0010

1000 1000

0

5

о

5

0

манд, группа выходов признака кода логических условий которого соединена с группой управляющих входов мультиплексора, выход которого соединен с первым входом третьего элемента И, выход признака следующего адреса микрокоманды блока памяти соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выходом признака модификации адреса блока памяти, выход старшего разряда второго регистра сдвига соединен с вторым входом четвертого элемента И и первым информационным входом мультиплексора, выход старшего разряда первого регистра сдвига соединен с вторым информационным входом мультиплексора, вход управления которого соединен с выходом триггера, третий информа- ционньй вход мультиплексора соединен с выходом Равно элемента сравнения и с четвертым входом блока анализа, выход блока анализа соединен с первым входом второго элемента ИЛИ, выход которого соединен с нулевым входом триггера, второй вход второго элемента ИЛИ соединен с выходом признака конца контроля регистра микрокоманд, выход признака айализа которого соединен с пятым входом блока анализа, шестой вход которого соединен с третьим выходом генера- тора тактовых импульсов и с вторым входом третьего элемента И.

Таблица 1

А В А В

I

0100 1000 0000 0001 0010 0100 0000 0001 0010 0000 . 0001 0001 001.0

II0100 1000

1000 1000 1000

1000

0100 0100

V0100

0010 0010

1000 1000 0100 0100 0100 0100 0010 0010 0010 0001 .0001 0000 0000 0000 0000

0001 0010 0100

1000

0000 . 0001

0100

0000 0001

А Б

А- в

А в

А в

А в

А. в

А в

А в

в

А- в

в

А в

А в

А в

А В

А; В

А в

А В

А В

А В

А В

А В

Продолжение табл. I

1 1

1 1

1 1

1 1

1 1

1 1 1

1 1

1 1

1 1 1

1 1

Таблица2

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1988 |

|

SU1500994A1 |

| Устройство для программного управления и контроля | 1991 |

|

SU1784943A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммный модуль | 1986 |

|

SU1427366A1 |

| Программируемый управляющий модуль | 1989 |

|

SU1649507A1 |

| Микропрограммное устройство управления | 1986 |

|

SU1310817A1 |

| Устройство для имитации объекта контроля | 1984 |

|

SU1188743A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1183964A1 |

| Программируемое устройство управления | 1988 |

|

SU1659983A1 |

| Устройство для обучения | 1988 |

|

SU1663618A1 |

Изобретение относится к области автоматики и вычислительной техники. Цель изобретения - повьшение достоверности контроля. Устройство содержит блок памяти, регистр микрокоманд, мультиплексор, регистр адреса, триггер, генератор тактовых импульсов, два регистра сдвига, элемент сравнения, контролируемую схему сравнения, блок анализа, два элемента И, два элемента Ш1И-НЕ, три элемента И. Устройство осуществляет проверку схемы сравнения в четырех режимах. В первом режиме на первую группу входов схемы сравнения подается число Л 0, а на другую при помощи регистра сдвига число В ,в котором единица присутствует только в одном разряде. Во втором режиме контроля подается число, содержащее единицу в разрядах Л, а на другой вход число, в котором единица содержится в предпоследнем разряде, и так далее, до тех пор, пока эта единица не перепишется в первый разряд регистра сдвига. В этом режиме проверяется равенство А В всех входов Qi Ь, . Третий и четвертый режимы эквивалентны первому и второму. За счет последовательного контроля реализуется минимальная совокупность проверок, обес- печиЬающих контроль всех цепей формирования сигналов .Л..В,А в, 5 ил. i (Л С

| Устройство для проверки схем сравнения | 1976 |

|

SU583436A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля схем сравнения | 1978 |

|

SU767767A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-03-15—Публикация

1984-08-09—Подача