Щиг.1

Изобретение относится к вычислительной технике и предназначено для решения одномерных задач математической физики, описываемых уравнениями вида

au(x.t) ,чэи(х.о + Эх2 -с(х at

+ f(x), х О, L. t О, (1)

с граничными условиями в точке х 0 одного из следующих видов:

U(0, t) - V°;(2)

(3)

(° ) -a, VcP° - U(0.t) (4)

и с граничными условиями в точке х L

одного из следующих видов: U(L.t) - VL;

,.

Эх

qt;

.

Эх

а также с начальными условиями вида U(x, 0) - VH(x).(8)

Цель изобретения - повышение точности решения.

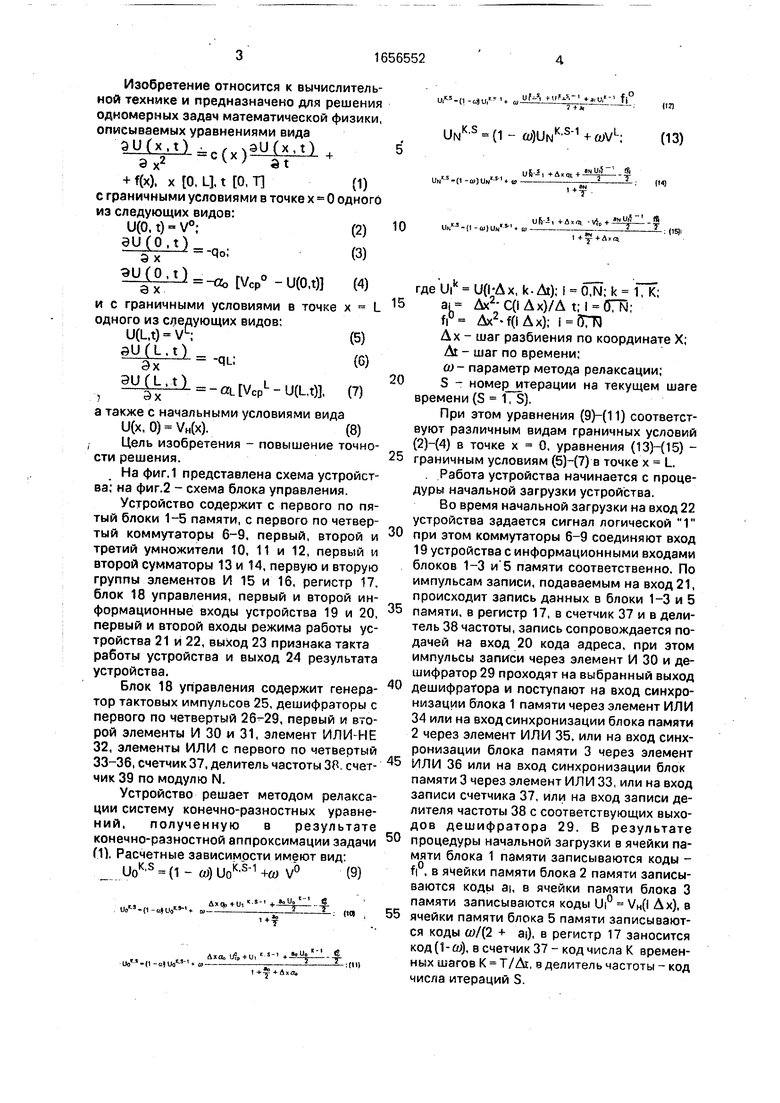

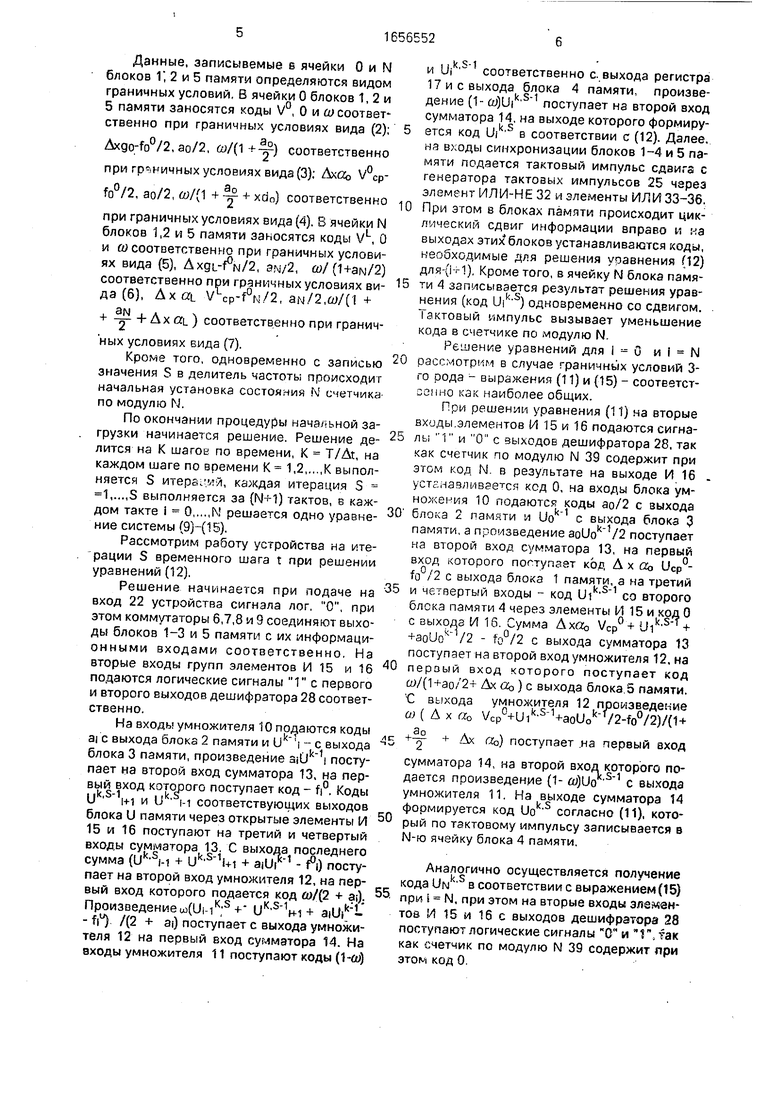

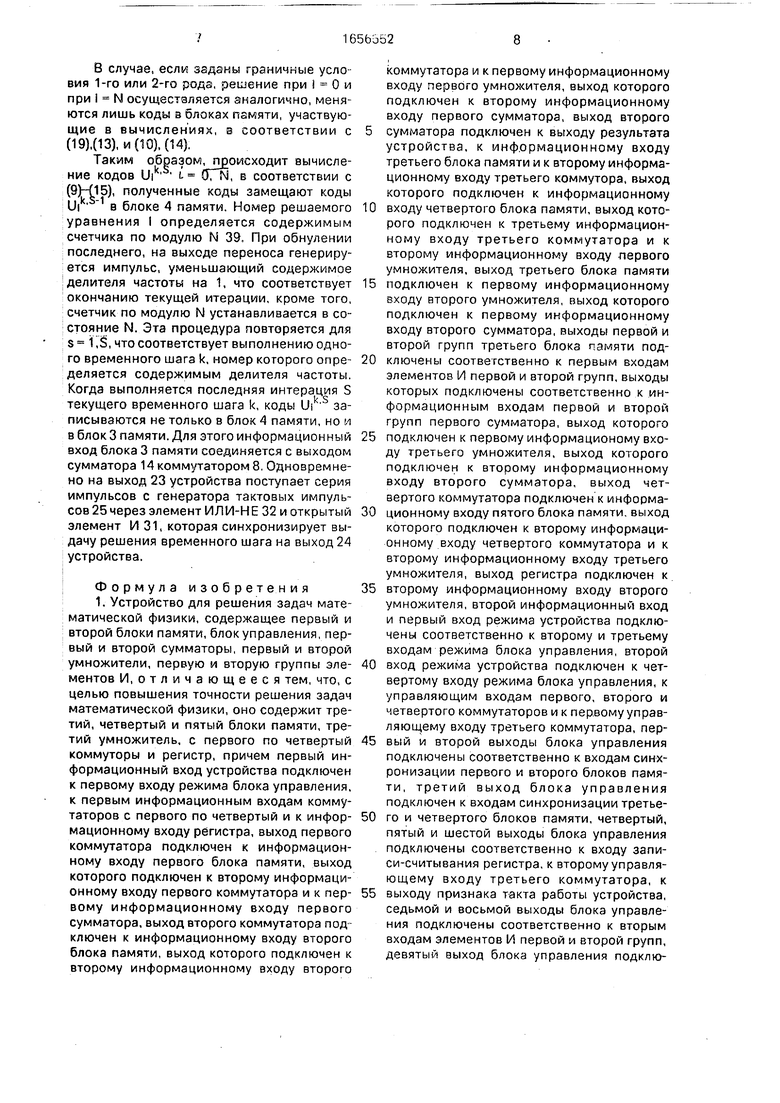

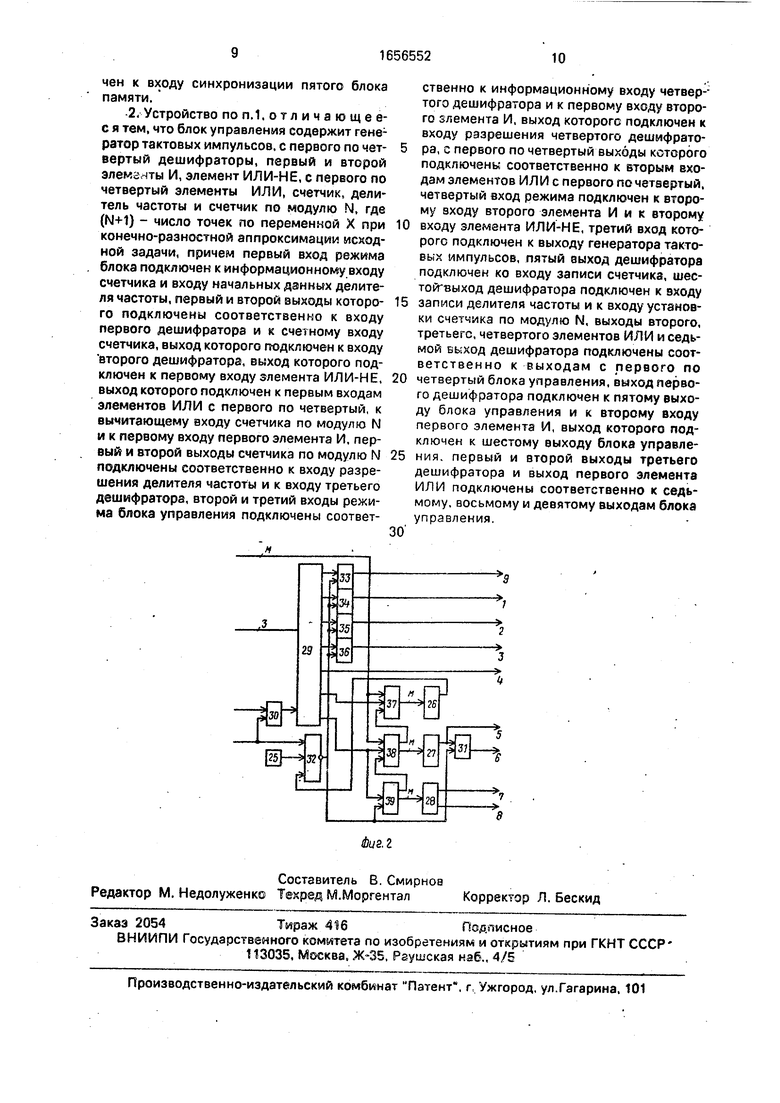

На фиг.1 представлена схема устройства; на фиг.2 - схема блока управления.

Устройство содержит с первого по пятый блоки 1-5 памяти, с первого по четвертый коммутаторы 6-9, первый, второй и третий умножители 10, 11 и 12, первый и второй сумматоры 13 и 14, первую и вторую группы элементов И 15 и 16, регистр 17, блок 18 управления, первый и второй информационные входы устройства 19 и 20, первый и второй входы режима работы устройства 21 и 22, выход 23 признака такта работы устройства и выход 24 результата устройства.

Блок 18 управления содержит генератор тактовых импульсов 25, дешифраторы с первого по четвертый 26-29, первый и второй элементы И 30 и 31, элемент ИЛИ-НЕ 32, элементы ИЛИ с первого по четвертый 33-36, счетчик 37, делитель частоты ЗП счетчик 39 по модулю N.

Устройство решает методом релаксации систему конечно-разностных уравнений, полученную в результате конечно-разностной аппроксимации задачи (1). Расчетные зависимости имеют вид; UoK S (1- V°(9)

(i и) «и till

+-Ь-У-с

Ana, uf,+ L ,

-atUo11

uf -(t

Ч

(Ш

UN S - (1 - w)UNK S 1 + oA/L;(13)

„,,., иМ.+л.

10И -И-йЦим -1. ш-- i- (IS

1 ч у + Дхя

15

20

30

35

где иг

%

U(i-Ax, k-At); l 0,N;k 1, К; Дх2 С(1 Дх)/Д t; i .

fiu Дх2-К1Дх); I-ДТП

Дх - шаг разбиения по координате X;

At - шаг по времени;

ш - параметр метода релаксации;

S - номер итерации на текущем шаге времени (, S).

При этом уравнения (9)-(11) соответствуют различным видам граничных условий (2)-(4) в точке х 0, уравнения (13Н15) - 25 граничным условиям (5)-(7) в точке х L

Работа устройства начинается с процедуры начальной загрузки устройства.

Во время начальной загрузки на вход 22 устройства задается сигнал логической 1 при этом коммутаторы 6-9 соединяют вход 19 устройства с информационными входами блоков 1-3 и 5 памяти соответственно. По импульсам записи, подаваемым на вход 21, происходит запись данных в блоки 1-3 и 5 памяти, в регистр 17, в счетчик 37 и в делитель 38 частоты, запись сопровождается подачей на вход 20 кода адреса, при этом импульсы записи через элемент И 30 и дешифратор 29 проходят на выбранный выход 40 дешифратора и поступают на вход синхронизации блока 1 памяти через элемент ИЛИ 34 или на вход синхронизации блока памяти 2 через элемент ИЛИ 35, или на вход синхронизации блока памяти 3 через элемент ИЛИ 36 или на вход синхронизации блок памяти 3 через элемент ИЛИ 33, или на вход записи счетчика 37, или на вход записи делителя частоты 38 с соответствующих выходов дешифратора 29. В результате процедуры начальной загрузки в ячейки памяти блока 1 памяти записываются коды - fi , в ячейки памяти блока 2 памяти записываются коды ai, в ячейки памяти блока 3 памяти записываются коды Ui° VH(I Дх), в ячейки памяти блока 5 памяти записываются коды ш/(2 + ai), в регистр 17 заносится код (1-w), в счетчик 37 - код числа К временных шагов К Т/Дг, в делитель частоты - код числа итераций S.

45

50

55

Данные, записывемые в ячейки 0 и N блоков 1, 2 и 5 памяти определяются видом граничных условий. В ячейки 0 блоков 1, 2 и 5 памяти заносятся коды V0, 0 и а)соответственно при граничных условиях вида (2):

Axgrj-fo /2.30/2, 6cV(1 +-Ј) соответственно при гр минных условиях вида (3); ЛхОо V°Cp- fo°/2. ao/2, w/(1 + -у- + xcin) соответственно

при граничных условиях вида (4). Е ячейки N блоков 1,2 и 5 памяти заносятся коды VL, j и ш соответственно при граничных условиях вида (5), AxgL-f N/2, N/2, (1+ar;/2) соответственно при граничных условиях ви да (6), AxaL VcP-f°rj 2. arj/2.w/(l +

-ь -я- + Ах «L ) соответственно при граничных условиях вида (7).

Кроме того, одновременна с записью значения S в делитель частоть; происходи начальная установка состоянии К ; по модулю N.

По окончании процедуры начальной загрузки начинается решение. Решение делится на К uiarot по времени, К Т/At, на каждом шаге по времени К 1,2К выполняется S итеро/ /м, каждая итерация 3 -- 1,..,,S выполняется за (N-M) гактоа, г. кь-кдом такте I 0N решается одно ypaF i- eние системы (9)-(15).

Рассмотрим работу устройства па гте- рации S временного шага t при решот.и уравнений (12).

Решение начинается при подаче на вход 22 устройства сигнала лог. С при этом коммутаторы 6,7,8 и 9 соединяют выходы блоков 1-3 и 5 памяти с их информационными входами соответственно. На вторые входы групп элементов И 15 и 16 подаются логические сигналы 1 с первого и второго выходов дешифратора 28 соответственно.

На входы умножителя 10 подаются коды at с выхода блока 2 памяти и U i - с выхода блока 3 памяти, произведение ail) i поступает на второй вход сумматора 13, на первый вход которого поступает код - fi°. Коды U и-1 и U (-1 соответствующих выходов блока U памяти через открытые элементы И 15 и 16 поступают на третий и четвертый входы сумматора 13. С выхода последнего сумма (Uk si-i + + ailir1 - f°i) поступает на второй вход умножителя 12, на первый вход которого подается код (2 + ai).

Произведениеw(Ui-iK s+ + aiUik - - ft) 1(2 + ai) поступает с выхода умножителя 12 на первый вход сумматора 14. На входы умножителя 11 поступают коды ()

k Ч-1

и Ui соответственно с выхода регистра 17 и с выхода блока 4 памяти, произведение (1- w)UiklS 1 поступает на второй вход сумматора 14, на выходе которого формиру5 ется код Ui e соответствии с (12). Далее. на входы синхронизации блоков 1-4 и 5 памяти подается тактовый импульс сдвига с генератора тактовых импульсов 25 чзреэ элемент ИЛИ-НЕ 32 и элементы ИЛИ 33-36.

О При этом в блоках памтти происходит цик- лмческий сдвиг информации вправо и (J,a выходах этих4блоков устанавливаются ходы, необходимые для решения уоавнения (12) для-{ г 1), Кроме того, в ячейку N блока памяг ти 4 записывается результат решения уравнения (код UjklS) одновременно со сдвигом. Iактовый импульс вызывает уменьшение кода в счетчике по модулю N

Решение уравнений для i - 0 и I N

О рассмотрим в случае граничных условий 3- го рода - Во1ражения (11) и (15) - соотеетст- oinio как наиболее общих.

При решении уравнения (11) на вторые вхиды элементов И 15 и 16 подаются сигна ; лы 1 и С с чыходое дешифратора 28, так как счетчик по модулю N 39 содержит при этом код N в результате на выходе И 16 уст: -1ачлив етс:: кед 0, на входы блока ум- ноемия 10 подаются коды ао/2 с выхода блока 2 памяти и Uo с выхода блока 3 памяти, а произведение aoUok /2 поступает на второй вход сумматора 13, на первый

ВХСД КОТОРОГО ПОГТуГ| ЙТ КОД А X Оо UCp fo /2 с выхода блока 1 памяти, а на третий и четвертый входы - код Uik S 1 со второго блока памяти 4 через элементы И 15 и код О с выхода И 1Я. Сумма АхОо VCp - Uikl + aoUo4 /2 - fi.i°/2 с выхода сумматора 13 поступает на второй вход умножителя 12, на первый вход которого поступает код w/(1+ao/2-f Ax OQ ) с выхода блока 5 памяти. С выхода умножителя 12 произведение о ( А х (to VCp°+Uik s 1+aoU0k 72-fo°/2)/(H

0

0

ao 2

- +

.Ax fZo) поступает на первый вход

0

5,

сумматора 14, на второй вход которого подается произведение (1- a)(Jo с выхода умножителя 11. На выходе сумматора 14 формируется код Uo согласно (11), который по тактовому импульсу записывается в N ю ячейку блока 4 памяти.

Аналогично осуществляется получение кода UNk s в соответствии с выражением (15) при i N. при этом на вторые входы элемен- тоь И 15 и 16с выходов дешифратора 28 поступают логические сигналы О и t. гак как счетчик по модулю N 39 содержит при этом код 0.

В случае, если заданы граничные уело вия 1-го или 2-го рода, решение при I 0 и при i N осуществляется аналогично, меняются лишь коды в блоках памяти, участвующие в вычислениях, в соответствии с (19).(13).и(10).(14).

Таким образом,гфоисходит вычисление кодов Ui L 07N, в соответствии с (9Н15), полученные коды замещают коды Uik в блоке 4 памяти. Номер решаемого уравнения I определяется содержимым счетчика по модулю N 39. При обнулении последнего, на выходе переноса генерируется импульс, уменьшающий содержимое делителя частоты на 1, что соответствует окончанию текущей итерации, кроме того, счетчик по модулю N устанавливается в состояние N. Эта процедура повторяется для s 1,5, что соответствует выполнению одного временного шага k, номер которого определяется содержимым делителя частоты. Когда выполняется последняя интерация S текущего временного шага k, коды Ui записываются не только в блок 4 памяти, но л в блок 3 памяти. Для этого информационный вход блока 3 памяти соединяется с выходом сумматора 14 коммутатором 8. Одновремне- но на выход 23 устройства поступает серия импульсов с генератора тактовых импульсов 25 через элемент ИЛИ-НЕ 32 и открытый элемент И 31, которая синхронизирует выдачу решения временного шага на выход 24 устройства.

Формула изобретения 1. Устройство для решения задач математической физики, содержащее первый и второй блоки памяти, блок управления, первый и второй сумматоры, первый и второй умножители, первую и вторую группы элементов И, отличающееся тем, что, с целью повышения точности решения задач математической физики, оно содержит третий, четвертый и пятый блоки памяти, третий умножитель, с первого по четвертый коммуторы и регистр, причем первый информационный вход устройства подключен к первому входу режима блока управления, к первым информационным входам коммутаторов с первого по четвертый и к информационному входу регистра, выход первого коммутатора подключен к информационному входу первого блока памяти, выход которого подключен к второму информационному входу первого коммутатора и к первому информационному входу первого сумматора, выход второго коммутатора под ключей к информационному входу второго блока памяти, выход которого подключен к второму информационному входу второго

коммутатора и к первому информационному входу первого умножителя, выход которого подключен к второму информационному входу первого сумматора, выход второго

сумматора подключен к выходу результата устройства, к информационному входу третьего блока памяти и к второму информационному входу третьего коммутора, выход которого подключен к информационному

входу четвертого блока памяти, выход которого подключен к третьему информационному входу третьего коммутатора и к второму информационному входу первого умножителя, выход третьего блока памяти

подключен к первому информационному входу второго умножителя, выход которого подключен к первому информационному входу второго сумматора, выходы первой и второй групп третьего блока гомяти подключены соответственно к первым входам элементов И первой и второй групп, выходы которых подключены соответственно к информационным входам первой и второй групп первого сумматора, выход которого

подключен к первому информационому входу третьего умножителя, выход которого подключен к второму информационному входу второго сумматора, выход четвертого коммутатора подключен к информационному входу пятого блока памяти, выход которого подключен к второму информационному входу четвертого коммутатора и к второму информационному входу третьего умножителя, выход регистра подключен к

второму информационному входу второго умножителя, второй информационный вход и первый вход режима устройства подключены соответственно к второму и третьему входам режима блока управления, второй

вход режима устройства подключен к четвертому входу режима блока управления, к управляющим входам первого, второго и четвертого коммутаторов и к первому управляющему входу третьего коммутатора, первый и второй выходы блока управления подключены соответственно к входам синхронизации первого и второго блоков памяти, третий выход блока управления подключен к входам синхронизации третьего и четвертого блоков памяти, четвертый, пятый и шестой выходы блока управления подключены соответственно к входу записи-считывания регистра, к второму управляющему входу третьего коммутатора, к

5 выходу признака такта работы устройства, седьмой и восьмой выходы блока управления подключены соответственно к вторым входам элементов И первой и второй групп, девятый выход блока управления подключем к входу синхронизации пятого блока памяти.

2. Устройство по п.1. о т л и ч а ю щ е е- с я тем, что блок управления содержит генератор тактовых импульсов, с первого по чет- вертый дешифраторы, первый и второй элем,; ты И, элемент ИЛИ-НЕ, с первого по четвертый элементы ИЛИ, счетчик, делитель частоты и счетчик по модулю N, где (N+1) - число точек по переменной X при конечно-разностной аппроксимации исходной задачи, причем первый вход режима блока подключен к информационному входу счетчика и входу начальных данных делителя частоты, первый и второй выходы которо- го подключены соответственно к входу первого дешифратора и к сменному входу счетчика, выход которого подключен к входу второго дешифратора, выход которого подключен к первому входу элемента ИЛИ-НЕ, выход которого подключен к первым входам элементов ИЛИ с первого по четвертый, к вычитающему входу счетчика по модулю N и к первому входу первого элемента И, первый и второй выходы счетчика по модулю N подключены соответственно к входу разрешения делителя частоты и к входу третьего дешифратора, второй и третий входы режима блока управления подключены соответ

ственно к информационному входу четвертого дешифратора и к первому входу второго элемента И, выход которого подключен к входу разрешения четвертого дешифратора, с первого по четвертый выходы которого подключены соответственно к вторым входам элементов ИЛИ с первого по четвертый, четвертый вход режима подключен к второму входу второго элемента И и к второму входу элемента ИЛИ-НЕ, третий вход которого подключен к выходу генератора тактовых импульсов, пятый выход дешифратора подключен ко входу записи счетчика, шес- тоРгвыход дешифратора подключен к входу записи делителя частоты и к входу установки счетчика по модулю N. выходы второго, третьего, четвертого элементов ИЛИ и седьмой выход дешифратора подключены соот- ветственно к выходам с первого по четвертый блока управления, выход первого дешифратора подключен к пятому выходу блока управления и к второму входу первого элемента И, выход которого подключен к шестому выходу блока управления, первый и второй выходы третьего дешифратора и выход первого элемента ИЛИ подключены соответственно к седьмому, восьмому и девятому выходам блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТЕСТЕР УРОВНЯ ИННОВАЦИОННОГО ИНТЕЛЛЕКТА ЛИЧНОСТИ | 2013 |

|

RU2522992C1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ РОЛЕВОЙ ФУНКЦИИ УЧАСТНИКА ТВОРЧЕСКОГО КОЛЛЕКТИВА | 2013 |

|

RU2541431C1 |

| Специализированный процессор | 1983 |

|

SU1144117A1 |

| Устройство для контроля и управления технологическими процессами испытаний и тренировки фотоэлектронных умножителей | 1988 |

|

SU1517041A1 |

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| ПРИБОР ДЛЯ РЕЙТИНГОВОЙ ОЦЕНКИ УРОВНЯ ГОТОВНОСТИ К ИННОВАЦИОННОЙ ДЕЯТЕЛЬНОСТИ | 2014 |

|

RU2548478C1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Цифровой измеритель показателей качества электрической энергии трехфазной сети | 1988 |

|

SU1633368A1 |

| Устройство для контроля и управления технологическим процессом тренировки и испытаний фотоэлектронных умножителей | 1986 |

|

SU1325516A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для решения одномерных задач математической физики Цель изобретения - повышение точности решения. Поставленная цель достигается тем, что устройство для решения задач математической физики содержит с первого по пятый блоки памяти 1-5, с первого по четвертый коммуторы 6-9. с первого по третий умножители 10-12, первый и второй сумматоры 13 и 14, первую и вторую группы элементов И 15 и 16, регистр 17 и блок 18 управления. 1 .ф-лы. 2 ил.

| Устройство для решения уравнения математической физики | 1976 |

|

SU584314A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для решения разностных краевых задач | 1977 |

|

SU691865A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-15—Публикация

1989-06-20—Подача