Изобретение относится к области вычислительной техники, в частности, к запоминающим устройствам.

Известны эапоминанлди.е устройст- 5 в а с самоконтролем р. , .2 .

Одно из известных устройств содержит матрица Пс1мяти, регистры, блок управления транслятором, блок анализа ошибок, блоки контроля четности Ю и коррекции ошибок, дешифраторы i .

К недостаткам этого устройства относятся большие аппаратурные затраты и низкое быстродействие устройства . 5

Из известных устройств наиболее близким техническим решением к изобретению является запоминающее устройство с самоконтролем, содержащее накопитель, блок кодирования, блок 20 анализа ошибок, блок коррекции ошибок , причем первые входы накопителя соединены с адресными входами устройства, вторые входы - с выходами блока кодирования, входы которого 25 подключены к выходам регистра слова, первый выход блока анализа ошибок соединен с первым контрольным выходом устройства, первый вхрД и второй выход - соответственно с пер- зо

вым и вторым входами блока коррекции ошибок, выход которого и вход регистра слова подключены соответственно к информационным выходу и входу устройства 2 .

Недостатками этого устройства являются большие аппаратурные затраты, уменьшение быстродействия запоминающего устройства из-за повторного считывания информации при выполнении контроля блоков устройства, отсутствие возможности контроля блока анализа ошибок устройства.

Цель изобретения - повышение быстродействия и упрощение устройства.

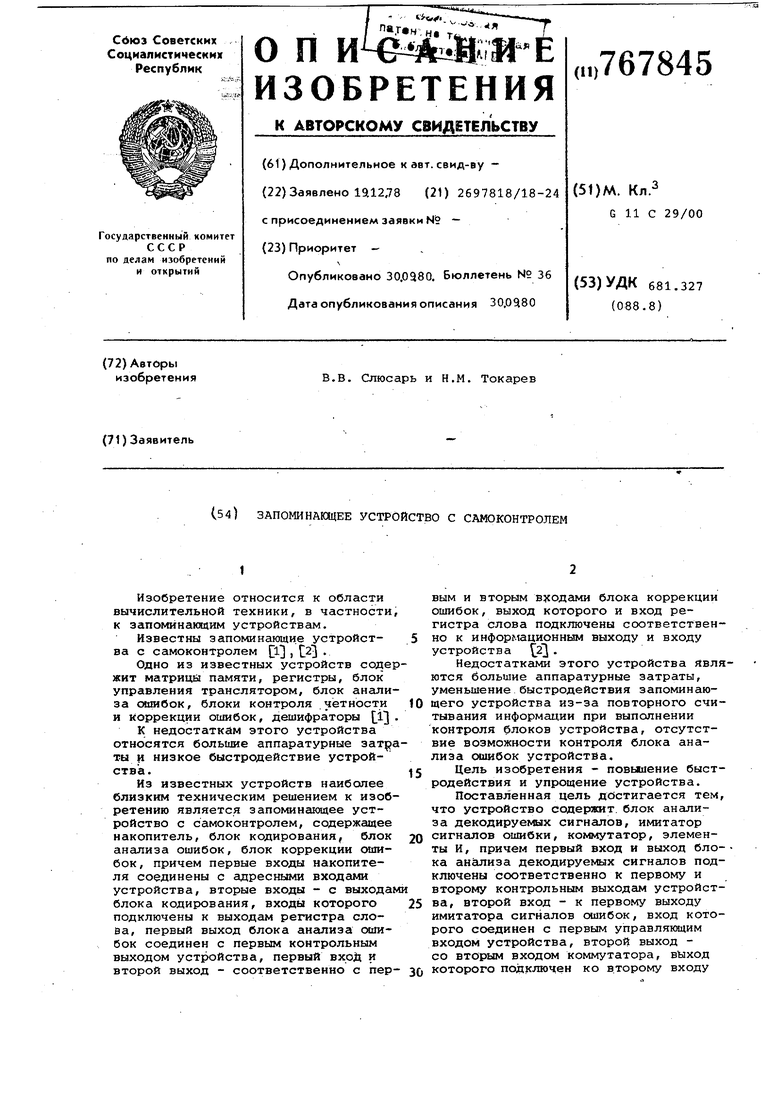

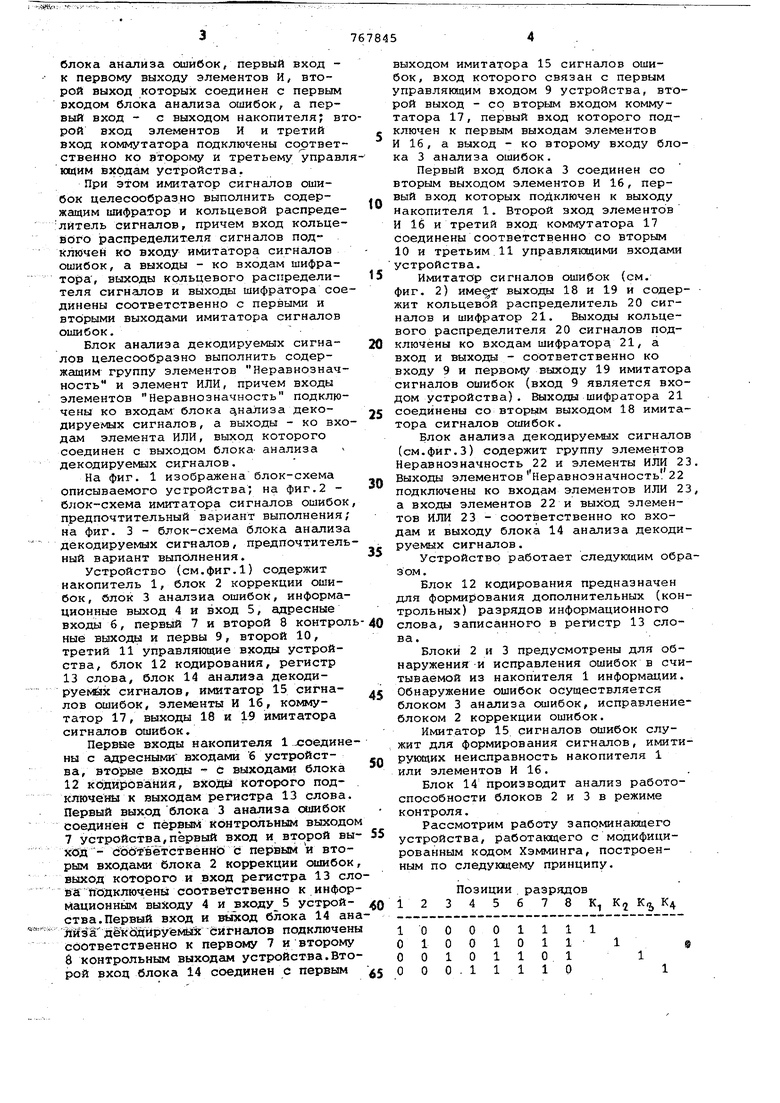

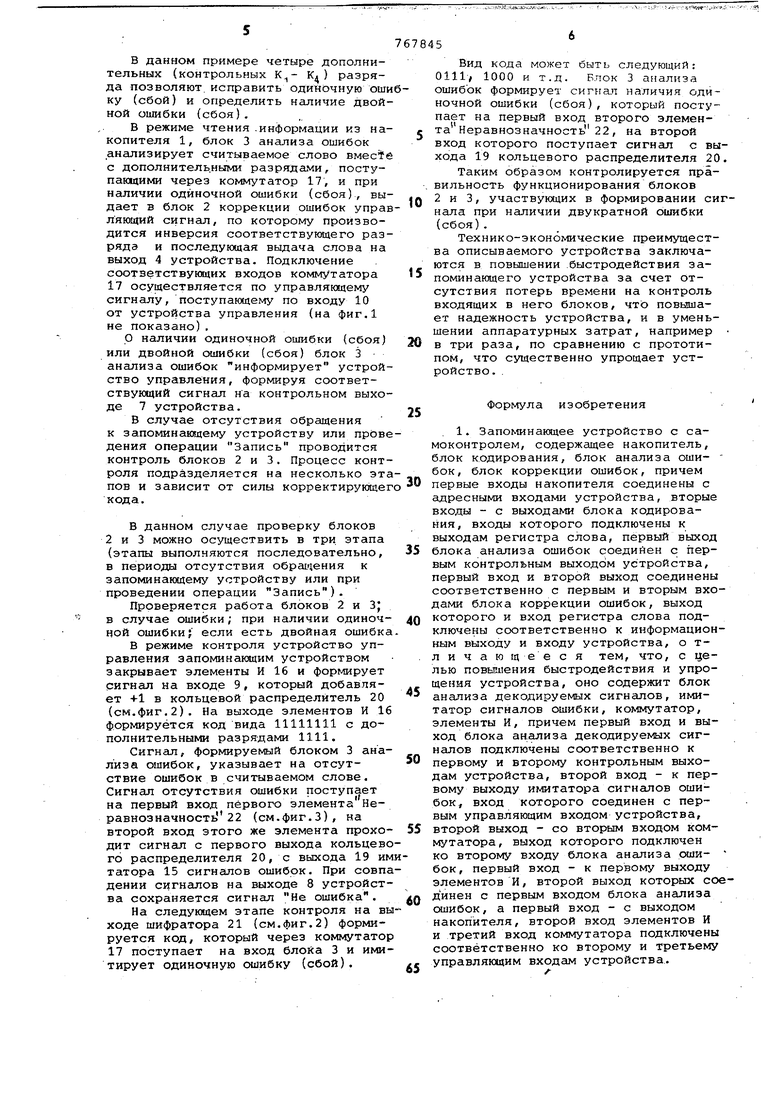

Поставленная цель достигается тем, что устройство содержит блок анализа декодируемых сигналов, имитатор сигналов ошибки, коммутатор, элементы И, причем первый вход и выход бло- ка анализа декодируемых сигналов подключены соответственно к первому и второму контрольным выходам устройства, второй вход - к первому выходу имитатора сигналов ошибок, вход которого соединен с первым управляющим входом устройства, второй выход со вторым входом коммутатора, вЪаход которого подключен ко в.торому входу блока анализа ошибок, первый вход к первому выходу элементов И, второй выход которых соединен с первым входом блока анализа ошибок, а первый вход - с выходом накопителя; в рой вход элементов И и третий вход коммутатора подключены соответ ственно ко второму и третьему Управл ющим входам устройства. При этом имитатор сигналов ошибок целесообразно выполнить содержащим шифратор и кольцевой распределйтель сигналов, причем вход кольцевого распределителя сигналов подключен ко входу имитатора сигналов ошибок, а выходы - ко входам шифратора, выходы кольцевого распределителя сигналов и выходы шифратора сое динены соответственно с первыми и BTCipbiMH выходами имитатора сигналов ошибок. Блок анализа декодируемых сигналов целесообразно выполнить содержащим группу элементов Неравнозначность и элемент ИЛИ, причем входы элементов Неравнозначность подключены ко входам блока наЛиза декодируемых сигналов, а выходы - ко вхо дам элемента ИЛИ, выход которого соединен с выходом блокз анализа декодируемых сигналов. На фиг. 1 изображена блок-схема описываемого устройства; на фиг.2 блок-схема имитатора сигналов ошибок предпочтительный вариант выполнения на фиг. 3 - блок-схема блока ангшиза декодируемых сигналов, предпочтитель ный вариант выполнения. Устройство (см.фиг.1) содержит накопитель 1, блок 2 коррекции ошибок, блок 3 аналзиа ошибок, информационные выход 4 и вход 5, адресные входы б, первый 7 и второй 8 контрол ные выходы и первы 9, второй 10, третий 11 управляющие входы устройства, блок 12 кодирования, регистр 13 слова, блок 14 анализа декодируемах сигналов, имитатор 15 сигналов ошибок, элементы И 16, коммутатор 17, выходы 18 и 19 имитатора сигналов ошибок. Первые входы накопителя 1 х:оедине ны с адресны1 э1 входами б устройства, вторые входы - с выходами блока 12 кодирования, Bxojttti которого подключены к выходам регистра 13 слова Первый выход блока 3 анализа ошибок соединен с первым контрольным выходо 7устройства,первый вход и второй вы - соЙтвётственнЬ с первь и вторым входами блока 2 коррекции ошибок вшсод которого и вход регистра 13 сл ви Лоаключены соответственно к инфор мационным выходу 4 и входу 5 устрой ства. Первый вход и выход блока 14 ан ДШойируемьйс сигналов подключен соответственно к первому 7 и второму 8контрольным выходам устройства.Вто рой вход блока 14 соединен с первым выходом имитатора 15 сигналов ошибок, вход которого связан с первым управляющим входом 9 устройства, второй выход - со вторым входом коммутатора 17, первый вход которого подключен к первым выходам элементов И 16 , а выход - ко второму входу блока 3 анализа ошибок. Первый вход блока 3 соединен со вторым выходом элементов И 16, первый вход которых подключен к выходу Накопителя 1. Второй вход элементов И 16 и третий вход коммутатора 17 соединены соответственно со вторым 10 и третьим 11 управляющими входгили устройства. Имитатор сигнсшов ошибок (см. фиг. 2) выходы 18 и 19 и содер- жит кольцевой распределитель 20 сигНсшов и шифратор 21. Выходы кольцевого распределителя 20 сигналов подключены ко входам шифратора 21, а вход и выходы - соответственно ко входу 9 и первому выходу 19 имитатора сигналов ошибок (вход 9 является входом устройства) . Выходы шифратора 21 соединены со вторьил выходом 18 имитатора сигналов ошибок. Блок анализа декодируемых сигналов (см.фиг.З) содержит группу элементов Неравнозначность 22 и элементы ИЛИ 23. Выходы элементов Неравнозначность 22 подключены ко входам элементов ИЛИ 23, а входы элементов 22 и выход элементов Или 23 - соответственно ко входам и выходу блока 14 анализа декодируемых сигналов. Устройство работает следующим образом. Блок 12 кодирования предназначен для формирования дополнительных (контрольных) разрядов информационного слова, записанного в регистр 13 слова. Блоки 2 и 3 предусмотрены для обнаружения и исправления ошибок в считываемой из накопителя 1 информации. Обнаружение ошибок осуществляется блоком 3 анализа ошибок, исправлениеблоком 2 коррекции ошибок. Имитатор 15 сигналов ошибок служит для формирования сигналов, имитирукмцих неисправность накопителя 1 или элементов И 16. Блок 14 производит анализ работоспособности блоков 2 и 3 в режиме контроля. Рассмотрим работу запоминакяцего устройства, работающего с модифицированным кодом Хэмминга, построенным по следующему принципу. Позиции . разрядов 12 3 4 5 6 7 8 К, Kj K.j К4 В данном примере четыре дополнительных (контрольных К,) разряда позволяют, исправить одиночную оши ку (сбой) и определить наличие двойной ошибки (сбоя). В режиме чтения.информации из накопителя 1, блок 3 анализа ошибок анализирует считываемое слово вмесТ е с дополнитель.ными разрядами, поступающими через коммутатор 17, и при наличии одиночной ошибки (сбоя), выдает в блок 2 коррекции ошибок управ лякщий сигнал, по которому производится инверсия соответствующего разряда и последующая выдача слова на выход 4 устройства. Подключение соответствувяцих входов коммутатора 17 осуществляется по управляющему сигналу, поступающему по входу 10 от устройства управления (на фиг.1 не показано), Р наличии одиночной ошибки (сбоя) или двойной ошибки (сбоя) блок 3 анализа ошибок информирует устройство управления, формируя соответствующий сигнал на контрольном выходе 7 устройства. В случае отсутствия обращения к запоминакхцему устройству или прове дения операции Запись проводится контроль блоков 2 и 3. Процесс контроля подразделяется на несколько эта пов и зависит от силы корректирующег кода. В данном случае проверку блоков 2 и 3 можно осуществить в три. этапа (этапы выполняются последовательно, в периоды отсутствия обра1пения к запоминающему устройству или при проведении операции Запись). Проверяется работа блоков 2 и 3J в случае садибки; при наличии одиночной ошибки; если есть двойная ошибка В режиме контроля устройство управления запоминакадим устройством закрывает элементы И 16 и формирует сигнал на входе 9, который добавляет +1 в кольцевой распределитель 20 (см.фиг.2). На выходе элементов И 16 формируется код вида 11111111 с дополнительными разря-дами 1111. Сигнал, формируемый блоком 3 анализа ошибок, указывает на отсутствие ошибок в считываемом слове. Сигнал отсутствия ошибки поступает на первый вход первого элемента Неравнозначность 22 (см.фиг.3), на второй вход этого же элемента проходит сигнал с первого выхода кольцево го распределителя 20, с выхода 19 им татора 15 сигналов ошибок. При совпа дении сигналов на выходе 8 устройства сохраняется сигнал Не ошибка. На следующем этапе контроля на вы ходе шифратора 21 (см.фиг.2) формируется кол, который через коммутатор 17 поступает на вход блока 3 и имитирует одиночную ошибку (сбой). Вид кода может быть следующий: 0111 1000 и т.д. Блок 3 анализа ошибок формирует сигнал наличия одиночной ошибки (сбоя), который поступает на первый вход второго элемента Неравнозначность 22, на второй вход которого поступает сигнал с выхода 19 кольцевого распределителя 20. Таким образом контролируется правильность функционирования блоков 2 и 3, участвующих в формировании сигнала при наличии двукратной ошибки (сбоя). Технико-экономические преимущества описываемого устройства заключаются в повышении быстродействия запоминающего устройства за счет отсутствия потерь времени на контроль входящих в него блоков, что повышает надежность устройства, и в уменьшении аппаратурных затрат, например в три раза, по сравнению с прототипом, что существенно упрощает устройство. . Формула изобретения 1. Запоминающее устройство с самоконтролем, содержащее накопитель, блок кодирования, блок анализа ошибок, блок коррекции ошибок, причем первые входы накопителя соединены с адресными входами устройства, вторые входы - с выходами блока кодирования, входы которого подключены к выходам регистра слова, первый выход блока анализа ошибок соедийен с первым контрольным выходом устройства, первый вход и второй выход соединены соответственно с первым и вторым входами блока коррекции ошибок, выход которого и вход регистра слова подключены соответственно к информационным выходу и входу устройства, о тличающееся тем, что, с целью повышения быстродействия и упрощения устройства, оно содержит блок анализа декодируемых сигналов, имитатор сигналов ошибки, коммутатор, элементы И, причем первый вход и выход блока анализа декодируемых сигналов подключены соответственно к первому и второму контрольным выходам устройства, второй вход - к первому выходу имитатора сигналов ошибок, вход которого соединен с первым управляющим входом устройства, второй выход - со вторым входом коммутатора , выход которого подключен ко второму входу блока анализа ошибок, первый вход - к первому выходу элементов И, второй выход которых соединен с первым входом блока анализа ошибок, а первый вход - с выходом накопителя, второй вход элементов И и третий вход коммутатора подключены соответственно ко второму и третьему управляющим входам устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1980 |

|

SU942163A2 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1249590A1 |

| Запоминающее устройство | 1981 |

|

SU1014042A1 |

| Устройство для обнаружения и исправления ошибок в блоках памяти | 1985 |

|

SU1277214A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1805503A1 |

| Запоминающее устройство | 1988 |

|

SU1547035A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Запоминающее устройство с коррекцией информации | 1982 |

|

SU1070610A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для кодирования и декодирования дискретной информации | 1983 |

|

SU1159166A1 |

Авторы

Даты

1980-09-30—Публикация

1978-12-19—Подача