1

Изобретение относится к области вводных устройств специализированных процессоров и предназначено для предварительного преобразования и ввода информации, полученной на сейсмических станциях, 5 и другой геофизической информации, и вывода результата обработки из процессора в ЭВМ.

Известно устройство для управления вводом-выводом 1, содержащее регистр хра- ю нения информации и коммутаторы.

Недостатком известного устройства является недостаточное быстродействие.

Наиболее близким по технической сущности к изобретению является устройство is 2, содержащее входной коммутатор, вход которого соединен с первым входом устройства, а выход через последовательно соединенные буферный сдвигающий регистр и выходиой коммутатор - с выходом устрой- 20 ства, первый коммутатор, выход которого соединен с входом буферного сдвигающего регистра.

В таком устройстве производится обработка только упакованной информации, 25 причем результат выдается в ЭВМ в неупакованном виде и упаковка информации производится в ЭВМ. Обработка материалов, полученных на цифровых сейсмических станциях, и другой геофизической информа- 30

цнн с плавающей запятой невозможна без предварительного преобразования информации в ЭВМ. Все это значительно снижает скорость ввода данных в процессор и вывода результата в ЭВМ.

Целью изобретения является повыщение быстродействия устройства.

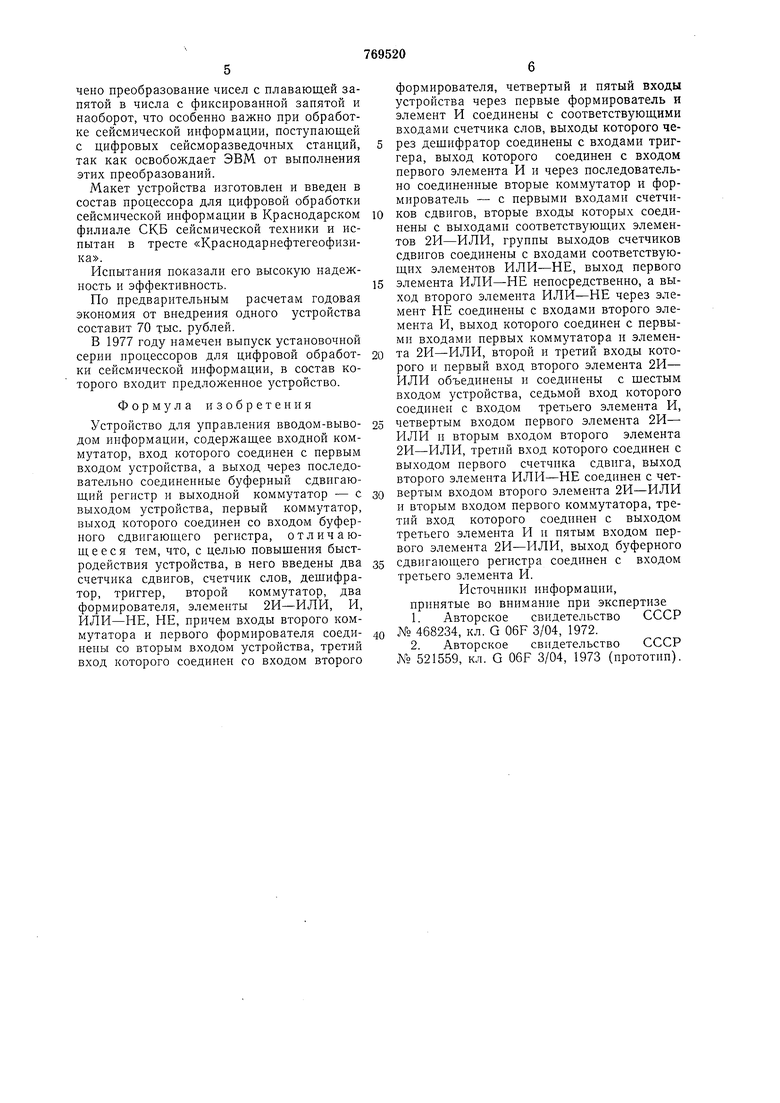

Поставлеииая цель достигается тем, что в иредложенное устройство введены два счетчика сдвигов, счетчик слов, дещифратор, триггер, второй коммутатор, два формирователя, элементы 2И-ИЛИ, И, ИЛИ-НЕ, НЕ. Входы второго коммутатора и нсрвого формирователя соединены со вторым входом устройства, третий вход которого соединен со входом второго формирователя. Четвертый и пятый входы устройства через первые формирователь и элемент И соединены с соответствующими входами счетчика слов, выходы которого через дещифратор соединены с входами триггера, выход которого соединен с входом первого элемента И н через последовательно соединенные вторые коммутатор н формнрователь с нервыми входами счетчиков сдвигов, вторые входы которых соединены с выходами элементов 2И-ИЛИ. Группы выходов, счетчиков сдвигов соединены с входами соответствующих элементов ИЛИ-НЕ. Выход первого элемента ИЛИ-НЕ непосредственно, а выход второго элемента ИЛИ-НЕ через элемент НЕ соединены с входами второго элемента И, выход которого соединен с первыми входами первых коммутатора и элемента 2И-ИЛИ, второй и третий входы которого и первый вход второго элемента 2И-ИЛИ объединены и соединены с шестым входом устройства, седьмой вход которого соединен с входом третьего элемента И, четвертым входом первого элемента 2И-ИЛИ и вторым входом второго элемента 2И-ИЛИ, третий вход которого соединен с выходом первого счетчика сдвига. Выход второго элемента ИЛИ-НЕ соединен с четвертым входом второго элемента 2И-ИЛИ и вторым входом первого коммутатора, третий вход которого соединен с выходом третьего элемента И и пятым входом первого элемента 2И-ИЛИ. Выход буферного сдвигающего регистра соединен с входом третьего элемента И. Структурная схема устройства приведена на чертеже.

Устройство содержит входной коммутатор 1, буферный сдвигающий регистр 2, выходной коммутатор 3, коммутаторы 4, 5, формирователи 6, 7, счетчик 8 слов, счетчики 9, 10 сдвигов, триггер 11, дешифратор 12, элементы 2И-ИЛИ 13, 14, элементы ИЛИ-НЕ 15, 16, элементы И 17-19 и элемент НЕ 20.

Устройство работает следующим образом.

При денормализации на формирователь 7 поступает код числа сдвигов вправо, который устанавливается в счетчиках 9, 10.

Если на выходах счетчика 10 будет хотя бы одна «1, то через элемент ИЛИ-НЕ 16 сигнал поступит на элемент 2И-ИЛИ 14, что разрешит прохождение синхросигнала на счетчик 10, на коммутатор 4 для разрещения сдвигов в буферном сдвигающем регистре 2 на четыре разряда за такт. Через элементы НЕ 20 и И 18 поступит запрет на элемент 2И-ИЛИ 13 и на коммутатор 4, что запретит поступление сигналов на счетчик 9 и сдвиги в регистре 2 на один разряд вправо и влево.

Таким образом, по каждому такту из счетчика 10 вычитается единица, а в регистре 2 происходит сдвиг на четыре разряда вправо. При установлении на счетчике 10 кода, имеющего все нули, запрещающий сигнал через элементы ИЛИ-НЕ 16 и 2И-ИЛИ 14 закроет вход счетчика 10 и через коммутатор 4 остановит сдвиги па четыре разряда вправо за такт в регистре 2, а через элемент НЕ 20 этот сигнал как разрешающий поступит на элемент И 18. Если на выходах счетчика 9 будет хотя бы одна «1, то через элементы ИЛИ-НЕ 15 и И 18 разрешение поступит на элемент 2И-ИЛИ 13 и на коммутатор 4.

Теперь за каждый такт в регистре 2 производится сдвиг на один разряд вправо, а из счетчика 9 - вычитание единицы, до тех

пор, пока на его выходах не установятся все «О. При этом запрет через элементы ИЛИ-НЕ 15 и И 18 поступит на элемент 2И-ИЛИ 13 и на коммутатор 4. На этом заканчивается процесс денормализации.

При упаковке или распаковке на коммутатор 5 и на формирователь 6 поступают сигналы, указывающие какой упакованный формат применяется. По синхросигналу в

счетчик 8 формирователя 6 заносится код количества упакованных слов минус единица. При наличии хотя бы одной «1 на выходе счетчика 8 через дешифратор 12, триггер 11 установится в такое состояние, при

котором разрешающий сигнал поступит на элемент И 17, что разрешит прохождение синхросигнала на счетчик 8 и на коммутатор 5, и код числа сдвигов из формирователя 7 перепишется в счетчики 9, 10. Сдвиги в

регистре 2 и управление этими сдвигами осуществляются так же, как и при денормализации. По окончании сдвигов в регистре 2 и счетчиках 9, 10 вновь устанавливается прежний код числа сдвигов, а из счетчика 8 вычитается «1. Как только на выходе счетчика 8 установятся все «О, триггер 11 через дешифратор 12 переключится в другое состояние и подаст запрет на коммутатор 5, что запретит установление кода числ а сдвигов в счетчиках 9, 10, и на элемент И 17, что запретит прохождение синхросигнала на счетчик 8. На этом заканчивается процесс упаковки или распаковки.

При нормализации на формирователь 7 поступает константа, которая устанавливается в счетчиках 9, 10, а на элементы И 19, 2И-ИЛИ 13 и 2И-ИЛИ 14 поступает разрешающий сигнал. Таким образом, при нормализации счетчики 9, 10 объединяются в

единый счетчик.

Элемент И 19 иодключается к инверсному выходу того триггера регистра 2, который является старшим разрядом мантиссы числа с плавающей занятой. На элементах И

19, 2И-ИЛИ 13 и на коммутаторе 4 будет разрешающий сигнал для сдвигов влево на один разряд до тех пор, пока в старшем разряде мантиссы числа будет «О. При этом по каждому такту в регистре 2 нроизводятся сдвиги на один разряд влево и вычитание единицы из содержимого счетчиков

9,10.

Как только в старшем разряде мантиссы появится «1, на элемент И 19 постунит запрещающий сигнал и через элемент 2И- ИЛИ 13 запретит поступление синхросигналов на вход объединенных счетчиков 9,

10,а через коммутатор 4 запретит сдвиги в регистре 2 и закончится нормализация.

При этом на прямых выходах счетчиков 9, 10 будет находиться прямой код порядка нормализованного числа, а в регистре 2- мантисса нормализованного числа.

Таким образом, значительно повышено

быстродействие устройства ввода .и обеспечено преобразование чисел с плавающей запятой в числа с фиксированной запятой и наоборот, что особенно важно при обработке сейсмической информации, поступающей с цифровых сейсморазведочиых станций, так как освобождает ЭВМ от выполнения этих преобразований.

Макет устройства изготовлен и введеи в состав процессора для цифровой обработки сейсмической информации в Краснодарском филиале СКВ сейсмической техники и испытан в тресте «Краснодарнефтегеофизика.

Испытания показали его высокую надежность и эффективность.

По предварительным расчетам годовая экономия от внедрения одного устройства составит 70 тыс. рублей.

В 1977 году намечен выпуск установочной серии процессоров для цифровой обработки сейсмической информации, в состав которого входит предложенное устройство.

Формула изобретения

Устройство для управления вводом-выводом ииформации, содержащее входной коммутатор, вход которого соединен с первым входом устройства, а выход через последовательно соединенные буферный сдвигающий регистр и выходной коммутатор - с выходом устройства, первый коммутатор, выход которого соединен со входом буферного сдвигающего регистра, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены два счетчика сдвигов, счетчик слов, дешифратор, триггер, второй коммутатор, два формирователя, элементы 2И-ИЛИ, И, ИЛИ-НЕ, НЕ, причем входы второго коммутатора и первого формирователя соедипены со вторым входом устройства, третий вход которого соединен со входом второго

формирователя, четвертый и пятый входы устройства через первые формирователь и элемент И соединены с соответствующими входами счетчика слов, выходы которого через дешифратор соединены с входами триггера, выход которого соединен с входом первого элемента И и через последовательно соединенные вторые коммутатор и формирователь - с первыми входами счетчиков сдвигов, вторые входы которых соединены с выходами соответствующих элементов 2И-ИЛИ, группы выходов счетчиков сдвигов соединены с входами соответствующих элементов ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ непосредственно, а выход второго элемента ИЛИ-НЕ через элемент НЕ соединены с входами второго элемента И, выход которого соединен с первыми входами первых коммутатора и элемента 2И-ИЛИ, второй и третий входы которого и первый вход второго элемента 2И- ИЛИ объединены и соединены с шестым входом устройства, седьмой вход которого соединен с входом третьего элемента И, четвертым входом первого элемента 2И- ИЛИ п вторым входом второго элемента 2И-ИЛИ, третий вход которого соединен с выходом первого счетчпка сдвпга, выход второго элемента ИЛИ-НЕ соединен с четвертым входом второго элемента 2И-ИЛИ и вторым входом первого коммутатора, третий вход которого соединен с выходом третьего элемента И и пятым входом первого элемента 2И-1--1ЛИ, выход буферного сдвигающего регистра соединен с входом третьего элемента И.

Источники информации, прпнятые во вннманне при экспертизе

1.Авторское свидетельство СССР № 468234, кл. G 06F 3/04, 1972.

2.Авторское свидетельство СССР N° 521559, кл. G 06F 3/04, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1983 |

|

SU1145340A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для ретрансляции речевых сигналов | 1990 |

|

SU1830627A1 |

| Коррелятор | 1983 |

|

SU1130874A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Генератор случайных чисел | 1981 |

|

SU980093A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| Устройство для отображения информации | 1986 |

|

SU1446642A1 |

| Устройство для нормализации чисел | 1980 |

|

SU862139A1 |

Авторы

Даты

1980-10-07—Публикация

1977-02-21—Подача