3

устройство функционирует так же, иок для микрокоманд первого типа.

Кром-е того, при реализации микрокоманд второго Бипа -и значении логического условия, равном нулю, происходит повторное считываиие одной п той же микрокоманды, что сопряжено с.дополиительными энергетическими затратами, и снижает надежность устройства.

изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что в микропрограммное устройство управления, содержащее регистр адреса, разрядный выход которого соедин-ен с первым входом дешифратора адреса, выход которого соечинен со входом блока памяти, выход которого соединен со входом информационного регистра, выход признаков которого через дешифратор признаков соединен с входом первого блока элементов И, управляю щий - вход которого является «ходом логических условий устройства, а выход соединен с единичным входом триггера условных переходов, единичный выход которого соединен с первым входом первого элемента И, выход которого соединен с первым входом регистра адреса, второй вход которого соединен с выходом второго .элемента И; первый вход которого соединен с нулевым выходом триггера условных переходов, второй вход второго элемепта И является адресным входом устройства, второй вход первого элемента И соединен с адресным выходом информационного регистра, группа выходов второго блока элементов И является группой выходов устройства, группа входов второго блока элементов И соединена с группой выходов дешифратора кода операций, вход которого соединен с выходом операционнопо поля информационного регистра, введены элементы И, ИЛИ и элементы задержки, единичный выход разряда совмещения операций информационного регистра соединен с третьим входом второго элемента И, первым входом первого элемента ИЛИ и с управляющим входом третьего элемента И, выход которого соединен с иервым входом второго элемента ИЛИ,.-выход .Которого через первый элемент задержки соединен со. вторым входом дешифратора адреса. Нулевой выход разряда совмещения операций информационого регистра соединен с управляющим ходом четвертого элемента И, второй ход которого соединен с выходом третьего лемента ИЛИ и с входом третьего элемента И. Группа входов третьего элемента

ЛИ соединена с группой выходсТв деифратора кода операции. Выход четверого элемента И через второй элемент заерЖ1щ соединен со входами пятого и шестого элементов И, управляющие входы оторых соединены соответственно с еди-ничным и нулевым выходами триггера условных переходов. Выход пятого элемента И соединен со вторыми входами первого и второго элементов ИЛИ, выход шестого элемента И - с едииичным входом разряда совмещения операций информационного регистра, а выход первого элемента ИЛИ- с управляющим входом второго блока эле.ментов И.

Сущность изобретения состоит в управлении длительностью времени между считыванием микрокоманд в зависимости от типа микрокоманды и значения логичесоадго условия.

Подключение единичного выхода триггера совмещения и выхода пятого элемента И через первый элемент ИЛИ к управляющим входам второго блока элементов И позволяет управлять считыванием микроопераций в зависимости от типа микрокоманды и значений логических условий.

Подключение выхода дешифратора кода оиерации через, третий элемент ИЛИ ко входам третьего и четвертого элементов И, которые управляются выходами разряда совмещения операций, позволяет формировать сигнал считывания следующей ми1крокоманды в зависимости от типа предыдущей и значения логического условия.

Подключением выхода третьего элемента И через второй элемент ИЛИ и первый элемент за.держки ко вторым входам дешифратора адреса образуется цепь подачи сигнала считывания очередной микрокоманды при реализации микрокоманд первого типа.

Подключение выхода четвертого элемента И через второй элемент задержки ко .ам пятого и miecToro элементов И служит для управления работой устройства при реализации микрокоманд второго типа.

Подключение выхода шестого элемента И кединичному входу разряда совмещения операций позволяет при ре.ализацип микрокоманд второго типа .в случае нулевого значения логического условия перейти к реализации микрокоманд первого типа без повторного считывания одной и той же микрокоманды.

Соединение единичного выхода триггера совмещения опер-аций с третьим входом первого элемента И служи,т для разрешения заииси единицы в регистр адреса.

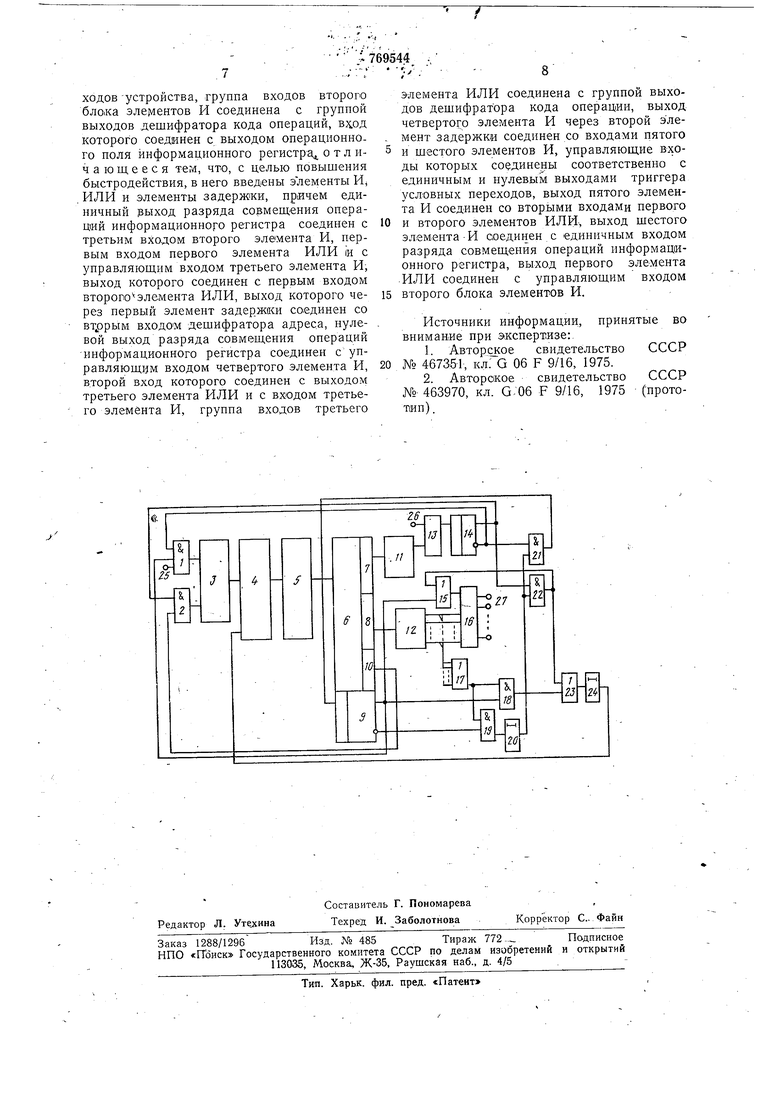

На чертеже изображена функциональная схема устройства.

Устройство содержит второй- / и первый 2 элементы И, регистр 5 адреса, дешифратор адреса 4, блок памяти 5, пнформациционный регистр 6, который состоит из поля признаков 7, операционного поля 8, разряда совмещения операций 9 и поля адреса 10 следующей микрокоманды, дешифратор 11 .признаков, дешифратор 12 кода операции, первый блок элементов И 5 13, триггер 14 условных переходов, первый элемент ИЛИ 15, второй блок элементов М 16, третий элемент ИЛИ 17, третий /8 и четвертый 19 элементы И, второй элемент задержки 20, шесток 21 и пятый 22 элементы И, второй элемент ИЛИ 23 н первый элемент задержки . .Адресный вход 25 устройства предназначен для установили кода начального адреса в регистре адреса .3, вход 26 - для ввода логических условий 26. При единичном значении логического условия триггер У4 устанавливается в единицу, при нулевом значении - в нуль. Устройство реализует микрокоманды двух типов. В исходном состоянии все элементы памяти находятся в нулевом состоянии. На адресный вхрд 25 устройства поступа-ет адрес перв,ой считываемой микрокоманды, жоторая при наличии сигнала на втором входе дешифратора адреса 4, считывается с блока памяти 5 врегистр 6. Если считанная микрокоманда является микрокомандой первого типа, то разряд совмещенияопераций 9 находится в состоянии единицы. Ири этом сигналом с .выхода разряда совмеихения операций 9 через элемент ИЛИ 15 разрешается считывание сигналов микроопераций с выходов 27 блока элементов И 16. С выходов дешифратора 12 через элемент ИЛИ 17 аигнал через открытый элемент И 18, элемент ИЛИ 23 поступает на вход элемента задержки 24. Одновременно с этим происходит проверка значения логического условия, код которого считывается с поля признаков 7 регистра 6 через дешифратор 11. Если значение логического условия равно нулю, то сигналом с нулевого выхода триггера 14 через открытый выход разряда совмешения операций 9, элемент И / прибавляется единица к содержимому регистра 3. Если значение логического условия равно единице, то через элемент И / с выхода поля адреса 10 регистра в в регистр 3 записыБается код очередиой микрокоманды. Сигналом с выхода элемента задержки 24, осуществляющего задержку на время выдачи выходных сигналов, опрашив ается дешифратор адреса 4 и считывается следующая микрокоманда. Если эта микрокоманда является микрокомандой первого, типа, то устройство функционирует аналогично описанному. При микрокоманде второго типа разряд совмещения операций 9 регистра 6 устанавливается в нуль, и открывается элемент И 19. Одновременно сигнал с выхода элемента ИЛИ 17 поступает через элемент И 19 на вход элемента задержки 20, осуществляющего задержку на время проверки логического условия. Кроме того, в это ж€ время происходит проверка логического условия, считанного с поля признаков 7 регистра 6. Если значение логического условия равно единице, то сигналами с выхода элемента задержки 20 и единичного выхода триггера 14 открывается элемент И 22, который через элемент ИЛИ 15 разрешает выдачу сигналов микроопераций с блока элемента И 16. Одновременно сигнал с выхода элемента И 22 поступает на вход элемента ИЛИ 23. Далее устройство функц1ионирует так же, как при реализации Ашкрокоманды первого типа, т. е. происходит выдача сигналов микроопераций с выхода 27, запись адреса следующей микрокоманды с выходов поля адреса следующей микрокоманды W регистра 6 в регистр адреса 3, далее опрос сигналом с выхода элемента задержки 24 дешифратора адреса 4 и считывание следующей микрокоманды. При нулевом значении лопического условия в случае реализации микрокоманды второго типа сигналами с выхода элемента задержки 20 и с нулевого выхода триггера 14 открывается элемент И 21, который устанавливает в единицу разряд совмещения операций 9 регистра 6, и устройство далее функционирует так же, как при реализации ми1крокоманды первого типа. При этом данная микрокоманда повторно с блока памяти не считывается. Таким образом, в устройстве происходнт считывание следующей миа-срокоманды через промежуток времени, длительность которого зависит от типа реализуемой микрокоманды и значения сигналов логических условий. Дополнительное введение элементов ИЛИ .и задержки указанных связей позволяет существенно повысить быстродействие устройства. Формула изобретения Микропрограммное устройство управления, содержащее регистр адреса, разрядный выход которого соединен с первым в.ходом дешифратора адреса, выход которого соединен со входом блока памяти, выход которого соединен со входом информационного регистра, -выход признаков которого через дешифратор признаков соединен с входом первого блока элементов И, управляющий вход которого является входом логических условий устройства, а выход соединен с единичным входом триггера условных переходов, единичный выход которого соединен с первым входом первого элемента И, выход которого соединен с первым входом регистра адреса, второй вход которого соединен с выходом второго элемента И, первый вход которого соединен с нулевым выходом триггера условных переходов, второй вход второго элемента И является адресным входом устройства, BTopofi вход первого элемента И соединен с адресным выходом информационного регистра, группа выходов второго блока элементов И является группой выходовустройства, группа входов второго блока элементов И соединена с группой выходов дешифратора кода операций, вход которого соединен с выходом операционного поля информационного регистра о тл ичающееся тем, что, с целью повышения быстродействия, в него введены элементы И . ИЛИ и элементы задерж ки, причем единичный выход разряда совмещения операций информационного регистра соединен с третьим входом второго элемента И, первым входом первого элемента ИЛИ и с управляющим входом третьего элемента И, выход которого соединен с первым входом второго элемента ИЛИ, выход которого через первый элемент задержали соединен со вторым входом дешифратора адреса, нулевой выход разряда совмещения операций Информационного регистра соединен с управляющим входом четвертого элемента И, второй вход которого соединен с выходом третьего элемента ИЛИ и с входом третьего элемента И, группа входов третьего

элемента ИЛИ соединена с группой выходов дешифратора кода операции, выход четвертого элемента И через второй элемент задержки соединен со входами пятого и шестого элементов И, управляющие входы которых соединены соответственно с единичным и нулевым выходами триггера условных переходов, выход пятого элемента И соединен со вторыми входами первого

и второго элементов ИЛИ, выход шестого элемента-И соединен с единичным входом разряда совмещения операций информационного регистра, выход первого элемента ИЛИ соединен с управляющим входом

второго блока элементов И.

Источники информации, принятые во внимание при акспертлзе:,

1.Авторское свидетельство СССР № 4673:51, кл. G 06 F 9/16, 1975.

2.Авторское свидетельство СССР № 463970, кл. О-Об F 9/16, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Многотактное микропрограммное устройство управления | 1983 |

|

SU1151963A1 |

| Мультимикропрограммная система управления | 1985 |

|

SU1291981A1 |

| Микропрограммное устройство управления с контролем | 1984 |

|

SU1233155A1 |

| Мультимикропрограммное устройство управления | 1982 |

|

SU1042017A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1142833A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1100624A1 |

| Устройство микропрограммного управления | 1982 |

|

SU1086431A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

| Микропрограммное устройствоупРАВлЕНия | 1979 |

|

SU830386A1 |

Авторы

Даты

1980-10-07—Публикация

1978-10-02—Подача