вых импульсов, генератора тестовых импульсов и компаратора f2.

Недостатком этого устройства является недостаточно высокое быстродействие, объяснякмцееся тем, что дл локализации неисправностей в блоке памяти требуется значительное время

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигается тем, что устройство содержит схему сравнения., первый вход-которой соединен с выходом генератора тестовых импульсов, второй вход - с выходом первого накопителя, а управляющие вход и выход соединены соответственно с одними из 9ЫХОДО8 И ВХОнов блока управления, выход адресioro мультиплексора подключен ко эходу первого накопителя.

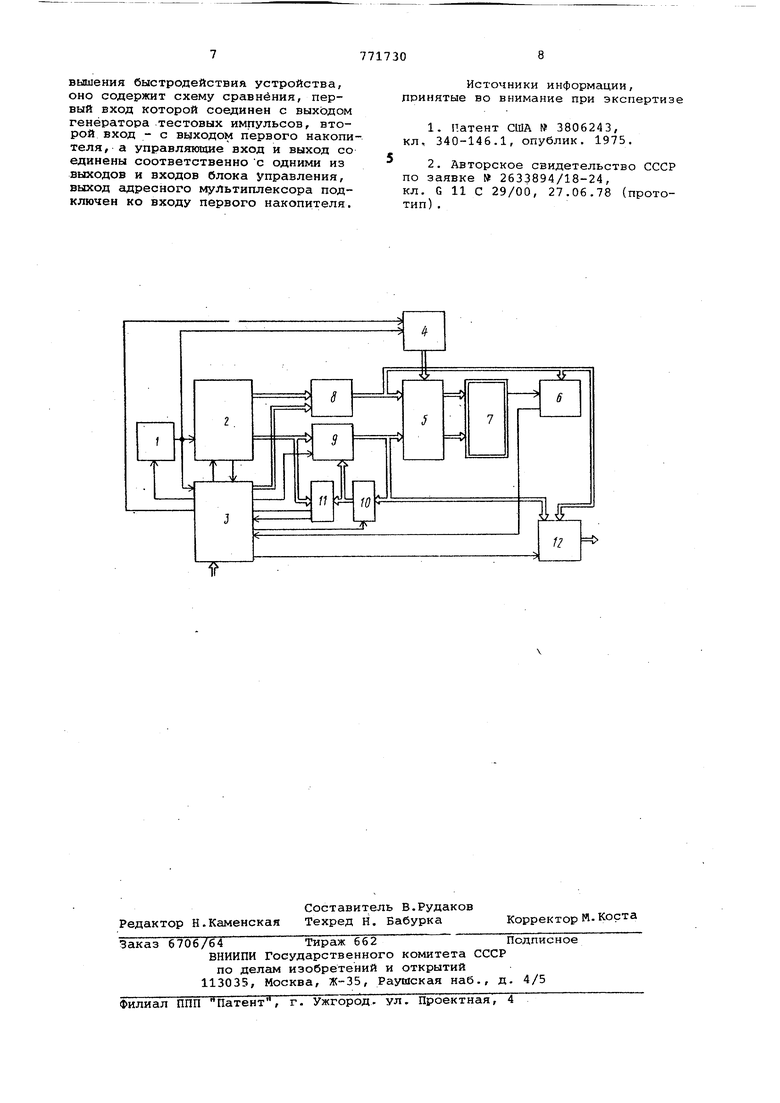

На чертеже изображена схема устройства для контроля полупроводниковой памяти.

Устройство содержит генератор 1 тактовых импульсов, генератор 2 тестовых импульсов, блок 3 управления, блок 4 формирования временной диаграммы, формирователь 5 сигналов контроля памяти, компаратор 6. К выходам формирователя 5 подключаются входы контролируемого блока 7 полупроводниковой пгиля.ти. Устройство также содержит блок 8 преобразования сигналов, адресный мультиплексор 9, пе:рвый накопитель 10, схему сравнения 11 и второй накопитель 12. При этом первый и второй входы схемы сравнения 11 соединены соответственно с выходом генератора 2 и накопителя 10, а управляющий вход и выход - соответственно с одними из выходов и входов блока 3, выход адресного мультиплексора 9 подключе ко входу накопителя 10.

Устройство работает следующим образом.

в начале испытания с блока 3 поступает сигнал установки генератора 2 в исходное состояние. Затем запускается генератор 1, под действием которого генератор 2 начинает вырабатывать последовательност воздействий из исходной тестовой последовательности (ТП), которые состоят из сигналов управления и сигнёшов адресации. Сигналы управления, без преобразования передаются через блок 8 на звходы формирователя 5, Сигналы адресации передаются на формирователь 5 через адресный мультиплексор 9. Блок 5 в соответствии с сигналами временной развертки, формируемыми блokc 1 4 под действием тактовых импульсов от генератора 1, передает сигнгилы управления на входы блока 7.

Компаратор б, если действуввдее на блок 7 тестовое воздействие является операцией считывания, сравнивает значение реакции импытуемого блока 7 с требуемой реакцией, В случае обнаружения несоответствия компаратор 6 формирует сигнал, поступающий на вход блока 3, который запрещает работу генератора 1 и формирует сигнал записи в накопител 10, в который записывается адрес сбойной, ячейки пасмяти (ЯП) , который поступает на входы накопите.ля 10с выходов адресного мультиплексора 9, Одновременно блок 3 формирует цикл восстановления состояния сбойной ЯП При этом блок 8 под действием сигИсшов с блока 3 преобразует сигналы управления, которые в этот момент представляют операцию считывания, в сигналы, соответствующие операции записи О или 1 в зависимости от того, какуютребуемую реакцию формирует в данный момент блок 8. Блок 4 под действием импульса от блока 3 формирует очередной цикл временной развертки, в соответствии с, которой формирователь 5 передает на входы испытуемого блока 7 новое значение управлякдцих сигналов. СигНс1лы сщресации не изменяются. После этого блок.3 разрешает передачу сигналов управления через блок 8 на входы формирователя 5 без изменения При этом формируется цикл считывания из сбойной ЯП, В случае обнаружения несоответствия компаратором 6 блок 3 формирует импульс записи в накопитель 12 значение действующего тестового воздействия, а затем, восстановив на выходах блока 8 значения восстанавливаняцего тестового воздействия, формирует импульс записи в накопитель 12. После этого продолжается испытание на исходную ТП, для чего возобновляется работа генератора 1, Если несоответствия при анализе состояния сбойной ЯП после его восстановления обнаружено не было, начинается диагностический этап, который начинаетс с возврата по ТП до первого оператора обращения к сбойной ЯП, адрес которой зафиксирован в накопителе 10;. Для & того блок 3 переключает генератор 2 на реверс и запускает генератор 1, При этом генератор 2 начинает вырабатывать последовательность тестовых воздействий в обратром направлении. Блок 8 под действием сигналов с блока 3 начинает инвертиррв ать значение записываемой в ЯП информации и на входа испытуемого блока 7 черезформирЪватель 5 подаётся последовательность тестовых воздействий из исходной ТП в обратнсял порядке, причем операция записи 1 заменяется на операцию записи О и наоборот. Значение операции считывания не изменяется. Анализ выходной реакции компаратором б не производится. При обратном ходе ТП схема 11 сравнивает адрес, формируемый генератором 2, с адресом, зафиксированным в накопителе Юр и при их совпадении блок 3 оста навливает работу генераторов 1 и 2, переводит генератор 2 в режим прямого хода ТП и вводит цикл восстановления состояния сбойной ЯП. При этом блок 8 преобразует сигналы управления в сигналы, соответствующие операции записи 1, если требуемая реакция равна 1, и записи О, если требуемая реакция равна О, После окончания возврата блок 3 переводит устройство в режим расширения отрезка ТП, н который был о существлен возврат,- относительно сбойной ЯП, адрес которой зафиксирован в накопителе 10. Режим испытания на расширенную ТП отличается от режима испытания на исходную ТП тем, что блок 3 уста навливает генератор 2 на режим работы, при котором он формирует очередное тестовое воздействие по каждому нечетному тактовому импульсу, начиная с третьего. Испытание на от резок расширенной ТП начинается с запуска генератора 1. Формируемое генератором 2 тестовое воздействие без изменения передается на входы испытуемого блока 7. второму так товому импульсу под действием сигна лов с блока 3 блок 8 преобразует сигналы управления в сигналы, соответствующие операции считывания, а адресный мультиплексор 9 начинает передавать на выход значение адреса с выходов накопителя 10, то есть происходит считывание из сбойной ЯП Если компаратор б обнаружил соответ ствие требуемой реакции, генератор 2 формирует очередное тестовое воздействие, после которого вводится цикл считывания из сбойной ЯП. При обнаружении несоответствия блок 3 запрещает работу генератора 1, формирует импульс записи в накопителе 12, и в него записывается зн ч-энйе тестового воздействия, которое в да ный момент подавалось на испытуемый блок 7. Затем блок 8 и адресный мультиплексор 9 под действием сигна ла с блока 3 начинает пёредавг.ть на свои выходы значение тестового воздействия, формируемого генератором 2, которое под действием импульса от блока 3 записывается в накопител 12. После этого блок 3 формирует Ци росстановления состояния сбойной ЯП, после чего разретпает работу генератора 1. Схема 11 сравнения на этапе расширения ТП сравнивает значени адреса, формируемого генератором 2, с адресом зафиксированным в накопителе 10, и, в случае совпадения, на блок 3 поступает импульс совпащения Процесс расширения ТП при этом прекращается и блок 3 переводит устройство в режим продолжения испытания на исходную ТП, и в случае обнаружения несоответствия изложенный выше процесс повторяется. Испытание заканчивается при окончании исходной ТП. При этом в накопителе 12 зафиксированы тестовые воздействия, по которым можно идентифицировать неисправности. Использование описанного устройства позволяет осуществлять с высокой точностью и достоверностью локализацию неисправностей контролируемого блока памяти, использовать для цели диагностики простые проверяющие тестовые последовательности, а также позволяет существено сократить время диагностики неисправностей. Формула изобретения Устройство для контроля полупроводниковой памяти, содержащее генератор тактовых импульсов, генератор тестовых импульсов, блок формирования временной диаграммы, формирователь сигналов контроля памяти, компаратор, блок преобразования сигналов, адресный мультиплексор, первый и второй накопители и блок управления, причем выход генератора тактовых импульсов соединен со входом генератора тестовых импульсов и входом блока формирования временной диаграммы, выход которого подключен к первому входу формирователя сигналов контроля памяти, Выходы генератора тестовых импульсов соединены с первым входом адресного мультиплексора и входом блока преобразования сигналов, выход которого соединен со вторым входом формирователя сигналов контроля памяти, первым входом компаратора, второй вход которого подключен ко входу устройства, а также с одним из входов в то-, рого накопителя, выход адресного мультиплексора соединен с третьим входом формирователя сигналов кон-, троля памяти и другим входом второго .накопителя, выход первого накопителя соединен со вторым входом адресного мультиплексора, управляющие входы генератора тактовых импульсов, генератора тестовых импульсов, блока формирования временной диаграммы, блока преобразования сигналов, адресного мультиплексе а, накопителей подключены к одним из выходов блока управления, одни из входов которого соединены с выходе генератора тактовых импульсов, генератора тестовых импульсов и компаратора, о т л и ч ай ш е е с я тем, что, с целью повышения быстродействия устройства, оно содержит схему сравнения, первый вход которой соединен с выходом генератора тестовых импульсов, второй вход - с выходом первого накопителя, а управляющие вход и выход со единены соответственно с одними из выходов и входов блока управления, выход адресного мультиплексора подключен ко входу первого накопителя.

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3806243, кл, 340-146.1, опублик. 1975.

2.Авторское свидетельство СССР по заявке № 2633894/18-24,

кл. G 11 С 29/00, 27.06.78 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоковпОлупРОВОдНиКОВОй пАМяТи | 1979 |

|

SU799021A1 |

| Устройство для контроля блоков полупроводниковой памяти | 1979 |

|

SU875469A2 |

| Устройство для контроля полупроводниковой памяти | 1978 |

|

SU749887A1 |

| Устройство для ввода информации | 1985 |

|

SU1282107A1 |

| Устройство для контроля блоков памяти | 1981 |

|

SU951408A1 |

| Устройство для контроля цифровых объектов | 1983 |

|

SU1160373A1 |

| Устройство для контроля блоков памяти | 1985 |

|

SU1283859A1 |

| Устройство для контроля оперативной памяти | 1985 |

|

SU1302325A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для обучения | 1987 |

|

SU1559366A1 |

Авторы

Даты

1980-10-15—Публикация

1978-07-03—Подача