(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПОЛУПРОВОДНИКОВОЙ ПАМЯТИ Изобретение относится к запоминаю щим устройствам и может быть использовано в устройствах тестового диагноза полупроводниковых Зсшоминающих устройств с произвольной выборкой. По основному авт. св. № 799021 известно устройство для контроле бло ков полупроводниковой памяти, сбдер жащее генератор тактовых импульсов, генератор тестовых импульсов, блок, управления, формирователь временной диаграммы, блок сопряжения, первый и второй накопители, первый и второй мультиплексоры, компаратор, преобразователь кодов, счетчик, первый, вто рой и третий регистры, первый, второй и третий элементы ИЛИ и сумматор Выход генератора тактовых импульсов подключен ко входам генератора тесто вых импульсов и формирователя времен ной Диаграммы, выходы которого подключены к первым входам блока сопряжения, выходы генератора тестовых иМ пульсов подключены соответственно ко входу преобразователя кодов и первому входу первого мультиплексорА вто рой вход которого подключен к выходу счетчика, выходы преобразователя кодов С9единены со вторыми входами бло ка сопряжения, управляющими входами компаратора и входами второго накопителя, выходы первого мультиплексора подключены к адресным входам первого и второго накопителей и к третьим входам блока сопряжения, выхохсы которого соединены с выходами устройства, входы компаратора подключены ко входам устройства, а его выходы - ко входам первого и второго регистров, выходы первого регистра соединены со входами первого элемента ИЛИ, входами второго накопителя и первыми входами второго мультиплексора, выходы второго регистра соединены со входами второго элемента ИЛИ и первым входами сумматора, вторые входы которого соединены с выходами третьего регистра, выходы сумматора соединены со входами третьего элемента ИЛИ и вто{ЯзЗми входами второго мультиплексора, выходы второго мультиплексора подключены ко входам первого накопителя, выходы которого соединены со входами третьего регистра, управляющие входы генератора т,актовых импульсов генератора тестовых импульсов формирователя временной диаграммы, преобразователя,первого и второго муьтиплексоров, счетчнка, первого и втоого накопителей,второго регистра подключены к одним из выходов блока упг равления,одни rfa входов которого подключены к выходам генератора тактовых импульсов,генератора тестовых импульсов и элементов ИЛИ /.ОНедостаток этого устройства заключается в том, что он не обеспечивает расшифровки диагностической информации, что снижает надежность устройства.

Цель изобретения - повышение надежности устройства путем обеспечения возможности расшифровки диагностической информации в процессе проведения диагностических испытаний.Поставленная цель достигается тем, что в известное устройство введены Четвертый и пятый регистры, группа элементов ИЛИ, третий, четвертый и пятый накопители, причем входы четвертого и пятого регистров и третьего накопителя подключены к выходам второго регистра, выходы четвертого регистра подключены к первым входам элементов ИЛИ группы и входам четвертого накопителя, а вьаходы пятого регистра - ко вторым входам элементов ИЛИ группы и входам пятого накопителя, выходы элементов ИЛИ группы подключены к одним из входов -второго регистра, адресные входы третьего, четвертого и пятого накопителей подключены к выходам первого мультиплексора, выходы третьего регистра подключены к одним из входов компаратора, выходы счетчика соединены с одними из входов генератора тестовых импульсов, одни из выходов блока управления подключены к управляющим входам третьего четвертого и пятого регистров, а также третьего, четвертого и пятого накопителей.

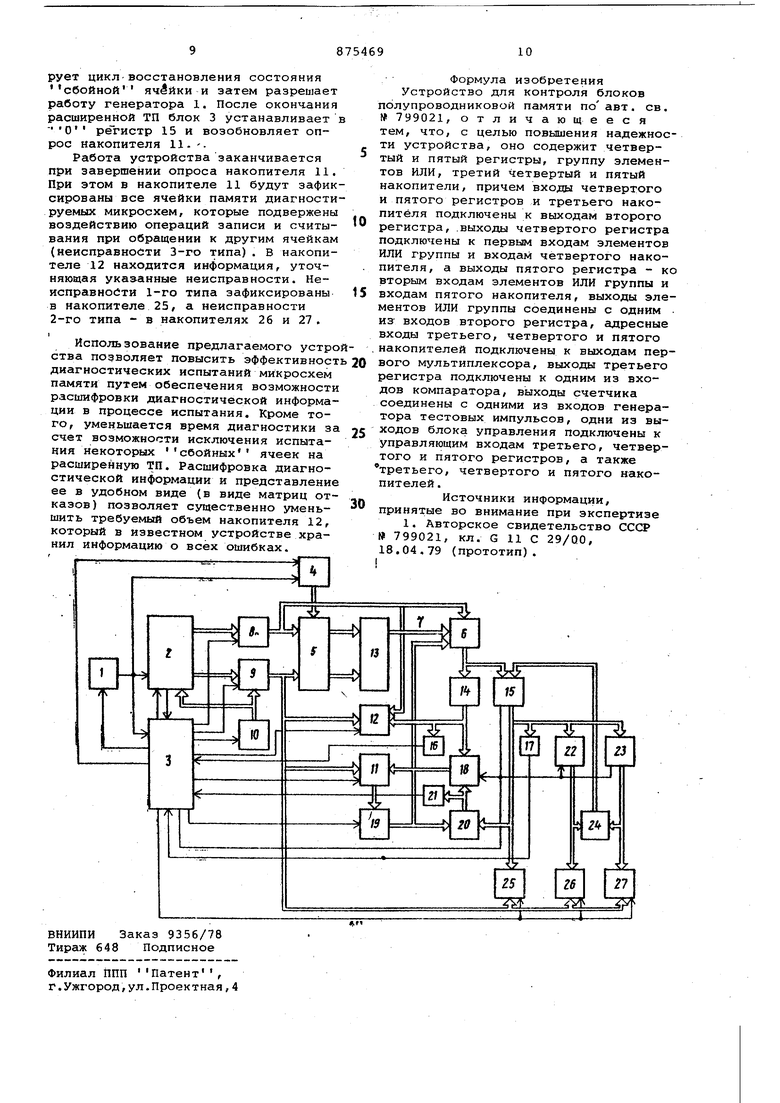

На чертеже изображена функциональная схема предложенного устройства.

Устройство содержит генератор 1 тактовых импульсов, генератор 2 тестовых импульсов, блок 3 управления, формирователь 4 временной диаграммы, блок 5 сопряжения, компаратор б имеющий вход 7, преобразователь 8 кодов, первый мультиплексор 9, счетчик 10, первый 11 и второй 12 накопители. Уст ройство подключается к блоку 13 полупроводниковой памяти, устройство также содержит первый 14, второй. 15 регистры, первый 16, второй 17 элементы ИЛИ, второй мультиплексотор 18, третий регистр 19, сумматор 20, третий лемент ИЛИ 21, четвертый 22 и пятый 23 регистры, группу 24 элементов шШ, третий 25, четвертый 26 и пятый 27 накопители.

В качестве блока 13 могут быть использованы диагностируемые микросхемы памяти. Вход генератора 1 подключен ко входам генератора 2 и формирователя 4, выходы которого подключены к первым входам блока 5 сопряжения. Выходы генератора 2 подключены соот-.

ветственно ко входу преобразователя 8 кодов и первому входу мультиплексора 9, второй вход которого подключен к выходу счетчика 10. Выходы преобразователя 8 кодов соединены со вторыми входами блока 5, управляющими входами компаратора б и входами накопителя 12. Выходы мультиплексора 9 подключены к адресным входам накопителей 11, 12, 25, 26 и 27 и к третьим входам блока 5, выходы которого подключены к выходам устройства Входы 7 компаратора 6 подключены к одному из входов устройства, а его выходы-- ко входам регистров 14 и 15 Выходы регистра 14 соединены со входами элемента ИЛИ 16, входами накопителя 12 и первыми входами мультиплексора 18. Вьлходы регистра 15 соединены со входами элемента ИЛИ 17, регисров 22 и 23, накопителя 25 Vi первыми входами сумматора 20. Выходы регистра 19 подключены к одним из входов компаратора 6 и вторым входам сумматора 20, выходы которого подключены ко входам элемента ИЛИ 21 и вторым входом мультиплексора 18. Выходы мультиплексора 18 подключены ко входам накопителя 11, выходы которого Соединены со входами регистра 19. Выходы регистра 22 подключены к первым входам элементов ИЛИ 24 и входам накопителя 26. Выходы регистра 23 подключены ко вторым входам элементов ИЛИ 24 и входам накопителя 27. Выходы элементов Ш1И 24 подключены к одним из входов регистра 15. Выходы счетчика 10 соединены с одним из вхо дов генератора 2. Управляющие входы генераторов 1 и 2, блока 4, преобразователя 8 кодов, мультиплексоров 9 и 18, счетчика 10j накопителей 11, 1 25, 26 и 27, регистров Г5, 19, 22 и 23 подключены к одним из входов блогка 3 управления, одни из входов которого подключены к выходам генераторов 1 и 2 и элементов ИЛИ 16, 17 и 21.

Работа устройства делится на два основных этапа: проверяющий этап и диагностический этап. Устройство осуществляет диагностику неисправностей .одновременно для Нескольких микросхем памяти.

На проверяющем этапе осуществляется функциональная проверка микросхем памяти и фи;ксация для каждой микросбойных

ячеек, т.е.

схемы адресов

ячеек, при считывании из которых по крайней мере один раз было обнаружено несоответствие требуемой реакции. Он начинается с установки генератора 2 в исходное состояние, мультиплексоров 18 и 9 на передачу сигналов соответственно с регистра 14 и генератора 2. в нулевое состояние устанавливаются счетчик 10, накопитель 11 и регистр 15. Все разряды регистра 19 устанавливаются в единичное состояние. Затем запускается генератор 1, и генератор 2, тактируемый генератор 1, начинает вырабатывать последовательность тестовых воздействий (ТВ) из исходной проверяющей тестовой последовательности (ТП). Каждое ТВ состоит из сигналов управления и сигналов адресащ1и, которые соответственно че рез блоки 8 и 9 передаются на входы блока 5, и в соответствии с сигналами временной развертки, формируемыми блоком 4, поступает на входы блока 1 (диагностируемых микросхем памяти). Если формируемое ТВ является операцией считывания, компаратор 6 срав нив aet значение реакций на выходах блока 13 с требуемой реакцией, посту пающей с генератора 2 через блок 8. Формируемый на выходах блока б векто несоответствий, в котором указывает на несовпадение реакций соответ.ствуюгявй Микросхемы с требуемой peaKip ja, а писывается в регистры 14 и 15. в регистре 15 происходи накапдв а1 « векторов несоответствий путем вуммнрования по ИЛИ очередного значения вектора с содержимым регист ра 15. В случае наличия хотя бы одной в регистре 14 (это фикси рует ИЛИ 16), блок 3 управле ния прфвмеает работу генератора 1, обеспечивает формирования цикла воестановления состояния сбойной ячейки и варабатывает сигнал записи в те разряды накопителя 11, ко торые соответствуют i на его вхо дах, соединенных через мультиплексор 18с выходами регистра 14 . Код адреса, по которому производится запись, поступает на адресные,входы на копителя 11с выходов генератора 2 f через мультиплексор 9. Таким образом адрес сбойной ячейки для всех рд новрёменяо диагностируемых микросхем памятификсируется путем записи 1 в соответствующие разряды накопителя 11. После этого блок 3 разрешает работу генератора 1 и генератор 2 начинает вырабатывать очередные ТВ из исходной ТП. Процесс повторяется до окончания ТП. При этом в регистре 15 .будут зафиксированы все неисправные микросхемы (об этом говорит наличие в соответствующих разрядах регистра) ; на выходе элемента ИЛИ 17 свидетельствует об исправности всех испытываемых микросхем. В этом случае их испытания заканчивается. При обнаружении хотя бы одной неисправной микросхемы устройство переходит на диагностический этап, на котором осуществляется локализациянеисправностей. Диагностический этап включает три этапа: 1-ый - локализация неисправностей, эквивалентных неработоспособности одной или несколь ких ячеек памяти (неисправности 1-го типа); 2-й - локализация неисправностей, приводящих к. одновременной выборке ДВУХ или более ячеек памяти (неисправности 2-го типа); 3-й локализация неисправностей, характеризуемых взаимным влиянием ячеек памяти в режимах записи и считывания (неисправности 3-го типа). Диагностический этап начинается с установки регистра 15 в нулевое состояние , После этого начинается опрос накопителя 11 путем последовательного изменения состояния счетчика 10, выходы которого через мультиплексор 9 подключены к адресным входам накопителя 11. Информация, считываемая с накопителя 11, передается в регистр 19. Вследствие присутствия нулевого кода на вторых входах сумматора 20, которые соединены с выходами регистра 15, сигналы с выхода регистра 19 без изменения передаются на входы элемента ИЛИ 21. Если на выходе ИЛИ 21 О опрос продолжается. В противном случае опрос прерывается. Счетчик 10 фиксирует адрес сбойной ячейки, а в регистре 19 указывает на микросхеки неисправные относбойнойячейки. сительно В процессе проведения диагностического этапа выходы компаратора 6, соответствующие исправным относительсбойныхячеек микросхемам. маскируются сигналами с выхода регистра 19. Затем начинается 1-ьЕй этап локализации неисправностей, при котором на блок 13 поступает последовательность из пяти операций запись О ) , за 1 , запись считывание при обращении считывание по алрёсу сбойной ячейки. Во время действия операции считывания к содер кимся« у регистра 15 суммируется по ИЛИ значения вектора несоответствий, поступающего с выхода компаратора б. Таким образом i« « в регистре 15 указывают на те неисправные микросхемы/ для которых проверяемая сбойная ячейка .является неработоспособной. После этого в накопитель 25, в котором фиксируются неисправности 1-го типа, по адресу, установленному на счетчике 10, переписывается информация из регистра 15. В накопитель 11 по тому же адресу записывается информация с выхода сумматора 20, который суммирует по модулю два содержимое регистров 15 и 19. Затем блок 3 проверяет состояние выхода элемента ИЛИ 21. Если на этом выходе О, блок 3 сбрасывает регистр 15 и возобновляет опрос накопителя. Если - (это свидетельствует о том, что не для всех неисправных микросхем соответст-: вующая сбойная ячейка является неработоспособной), то в регистр 19 переписывается информация, записанная в накопителе 11 по адресу сбойноА ячейки г и устррйство переходит на вт рой этап локализации неисправностей. Второй этап начинается с установки в нулевое состояние регистров 22 и 23/ а всех разрядов регистра 15 в единичное состояние. Генератор 2 начинает вырабатывать специальную ТП предназначенную для локализации неисправностей 2-го типа. На втором этапе генератор 2 йырабатывает периодически повторяющуюся последовательность управляющих сигналов: запись , запись , считывание О ... Во время действия операций запись О и считывание 0 мультиплексор 9. под действиём сигнала с блока 3 передает на входы блока 5 адрес сбойной. ячей ки с выхода счетчика. 10, а во время действия операции запись i генератор 2 в соответствии с адресом, по ступающим с выхода счетчика 10, вырабатывает адрес, соответствующий ад ресу ячейки, расположенной на той же стороне, что и проверяемая сбойная ячейка. В результате формируется последовательностьJ запись О в сбойную ячейку, запись в ячейку той же строки, считывание О из сбойной ячейки... Это повторяется для всех ячеек данной строки (за исключением проверяемой сбойной ячейки) при неизменном адресе сбойной ячейки. При кажсбойнойячейки дом считывании из в регистр 15 заносится вектор несоот ветствий, причем он постоянно сумми руется по И с предыдущим состоянием регистра. Состояние регистра 15 каж дый раз ансшизируется на элементом ИЛИ 17. При обнаружении О испытание с помощью указан юй после довательности прекращается. Если при испытании данной последовательностью элемент ИЛИ 17 ни ра зу не обнаружил нулевое состояние ре гистра 15, неисправность 2-го типа обнаружена и в регистре 22 передает ся содержимое регистра 15. После этого, а также при обнаруже нии нулевого сотояния регистра, уст ройство начинает генерировать ту же последовательность, но с инверсным значением записываемой информации. Если при исп з1тании на данную инверсную последовательность регистр 15 ни разу не переходил в нулевое состояние, к содержимому регистра 2 по ЮШ сумглируется информация, нахо в регистре 15. После этого все повторяется при обращении не к ячейкам строки, а к ячейкам столбца, на котором располо жена сбойная ячейка. При оконча НИИ как прямой, так и инверсной последовательностей информация из регистра 15 передается в регистр 23. Затем содержимое регистров 22 л 23 Переписывается соответственно в HELкопители 26 и 27, в которых Фиксируются неисправности 2-го типа. Запись осуществляется по адресу, поступающему на адресные входы накопителей через мультиплексор 9 с выходов- счетчика 10. Блок 24 осуществляет поразрядное суммирование по ИЛИ векторов, находящихся в регистрах 22 и 23. Результат суммирования передается в регистр 15. Затем сумматор 20 суммирует по модулю два содержимое регистров 15 и 19. Результат через мультиплексор 18 передается на входы накопителя 11, в который он записывается по адресу, установленному на счетчике 10. После этого анализируется состояние выхода элемента ИЛИ 21. Если обнаружен , блок 3 сбрасывает в О регистр 15 и возобновляет опрос накопителя 11. Если .на выходе ИЛИ 21 - , в регистр 19 переписывается информация, записанная в накопителе 11 по адресу сбойной ячейки, и устройство переходит на 3-й этап локсшизации неисправностей. Третий этап представляет собой испытание на расширенную ТП для сбойной ячейки, адрес которой зафиксирован счетчиком 10. Перед началом формирования расширенной ТП блок 3 управления обеспечивает запись в накопитель 12 значения адреса сбойной ячейки. Для формирования расширенной ТП блок 3 устанавливает генератор 2 на режим работы, при котором он формирует очередное ТВ по каждому нечетному тактовому импульсу, поступающему с генератора 1. Во время нечетного периода ТВ с выходов генератора 2 передается на входы диагностируемых микросхем памяти. Во время действия, четного периода адресная часть ТВ поступает через мультиплексор 9 с выходов счетчика 10, ас выходов преобразователя 8 снимается управляющая часть ТВ, соответствующая операции считывание . Требуемая реакция формируется генератором 2. Таким образом, расширенная ТП представляет собой последовательность j образованную из исходной ТП путем вставления после каждого ТВ операцки считывания из Iсбойной ячейки. После каждой дополнительной операции считывания блок 3 анализирует состояние выхода ИЛИ 16. Если обнаружен О , формирование расширенной ТП продолжается. Если на выходе ИЛИ 16 (обнаружена неисправность 3-го типа), блок 3 приостанавливает работу генератора 1, переключает мультиплексор 9 и преобразователь 8 на передачу сигналов с выхода генератора 2, и Формирует импульс зариси в накопитель 12 значения формируемого генератора 2 ТВ и вектора несоответствий, находящегося в регистре 14. После этого блок 3 форми

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоковпОлупРОВОдНиКОВОй пАМяТи | 1979 |

|

SU799021A1 |

| Устройство для контроля полупроводниковой памяти | 1978 |

|

SU749887A1 |

| Устройство для контроля полупроводниковой памяти | 1978 |

|

SU771730A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Оперативное запоминающее устрой-CTBO C САМОКОНТРОлЕМ | 1979 |

|

SU809402A1 |

| Устройство для контроля интегральных схем | 1980 |

|

SU966699A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

Авторы

Даты

1981-10-23—Публикация

1979-12-19—Подача