Из.обретение относится к вычислительной технике и может быть использовано в вычислительных системах для сопряжения, например, периферийного устройства с оперативной памятью ЭВМ.

Цель изобретения - повьппение достоверности передаваемой адресной информации за счет организации контроля сформированного очередного ад- реса.

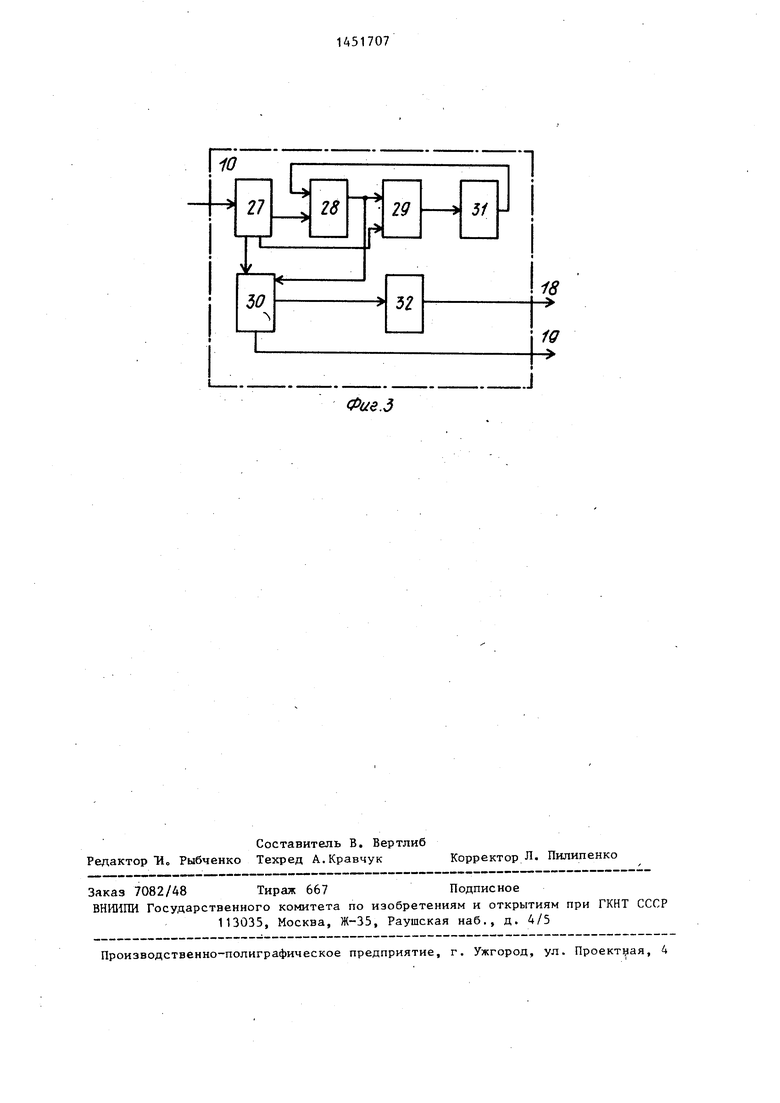

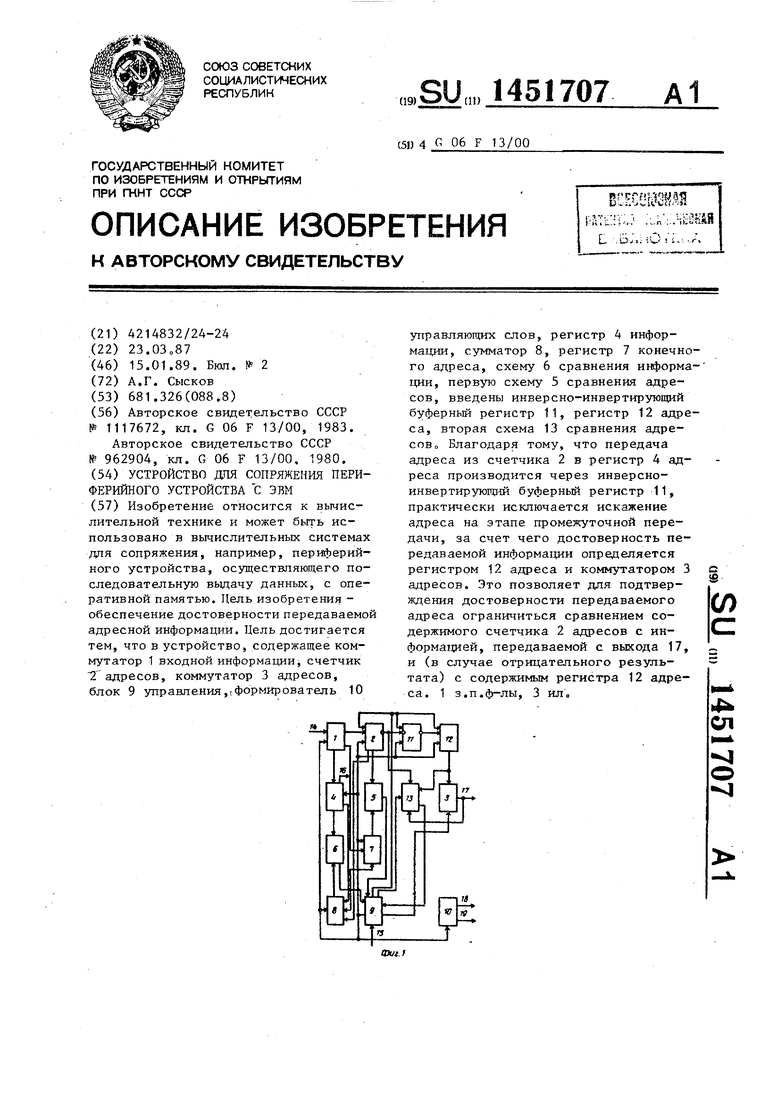

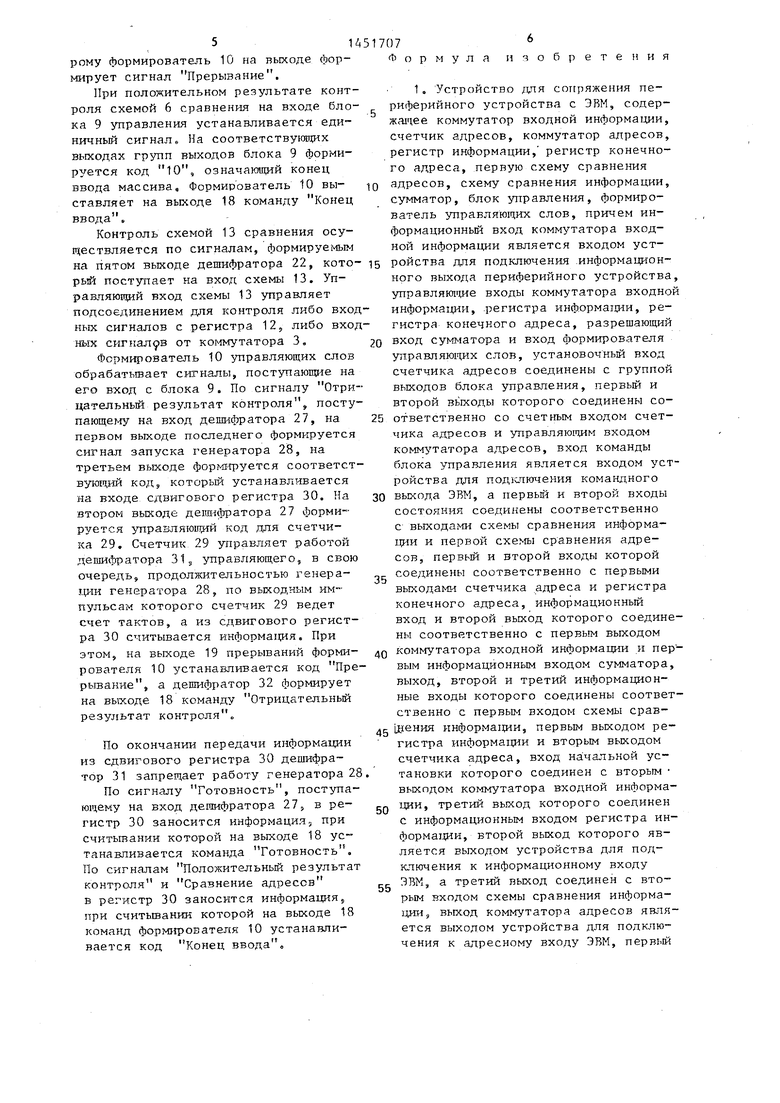

На фиг. 1 представлена блок-схема устройства; на фиг, 2 - функциональная схема блока управления; на фиГоЗ - 1 :хема формирователя управляющих слов.

Устройство содержит коммутатор 1 входной информации, счетчик 2 адресов, коммутатор 3 адресов, регистр 4 информации, первую схему 5 сравнения, схему 6 сравнения информации, регистр 7 конечного адреса, сумматор 8, блок 9 управления, формирователь 10 управляющих слов, буферный регистр 11, регистр 12 адреса, вторую схему 13 сравнения адресов, вхо- ды 14 и 15 и выходы 16-19 устройства

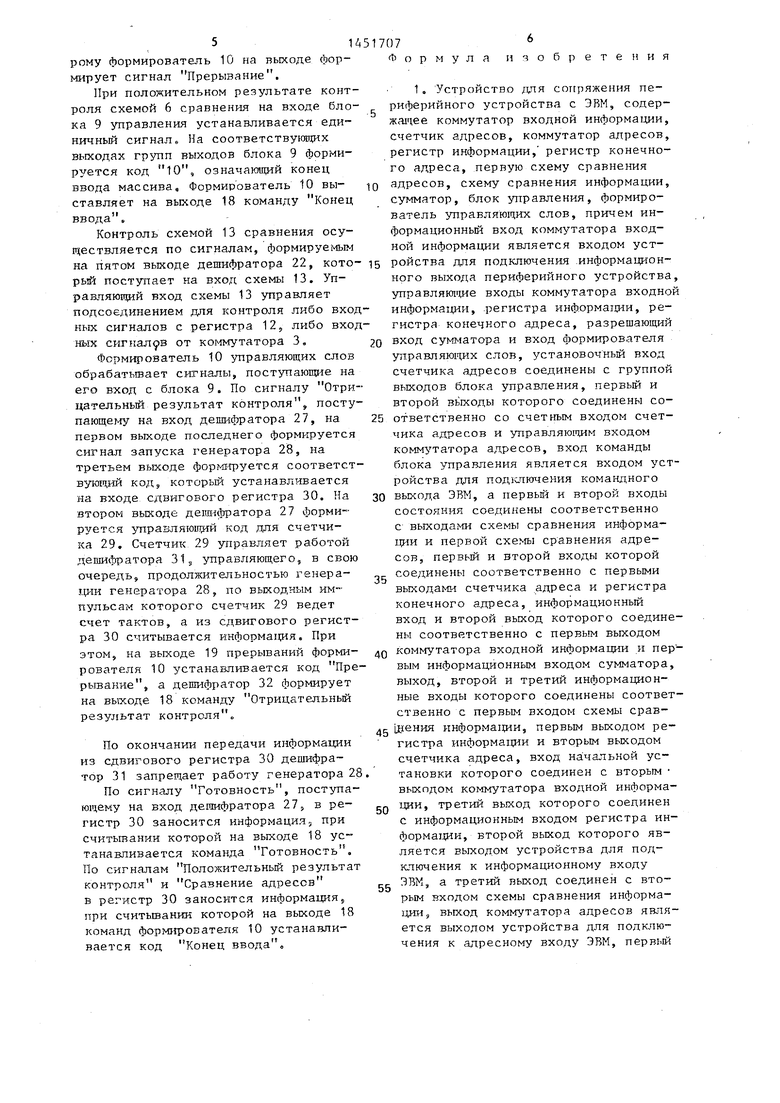

Блок 9 управления содержит генератор 20 меток, счетчик 21, дешифратор .22, элемент НЕ 23, второй и пео- вый элементы и 24, 25 и элемент ИЛИ 26.

Формирователь 10 управляющих слов содержит входной дешифратор 27, генератор 28 импульсов, счетчик 29 тактов, регистр 30 сдвига, дешифратор 31 числа тактов и дешифратор 32 ко- манды прерывания.

Устройство работает следующим образом.

На информационный вход 14 устройства поступает информационньм массив которьй состоит из паспорта (первые три слова) и тела массива, а также контрольной суммы паспорта и тела массива (последнее слово), Паспорт по порядку следования состоит из следующих слов; начальньй адрес, конечный адрес и контрольная сумма пер вых двух слов.

При поступлении на вход 15 команды Начать ввод блок 9 формирует сигналы установки в исходное состояние коммутатора 1, счетчика 2, регистров f1, 12, 4, 7, сумматора 8 По этому же сигналу формирователь 10 формирует на выходе 18 команду За-

(1

прос ,

в следующем такте работы блока 9 первое слово (начальный адрес), поступающее на информационный вход 14

через коммутатор 1, заносится в счетчик 2, с выхода которого поступает на вход сумматора 8 и складывается с его содержимым.

Во втором такте работы блока 9 второе слово (конечный адрес) поступает в регистр 7 и также, поступая с его выхода на вход сумматора 8, складьшается с содержимым последнего, В этом же такте содержимое счетчика 2 пересьиается в регистр 11, после чего сигналом с выхода блока 9 содержимое счетчика 2 увеличивается на единицу, В следующем такте третье слово поступает в регистр 4 информации. Содержимое регистра 11 пересылается в регистр 12, а содержимое счетчика 2 - в регистр 11.

Результаты суммирования поступают в схему 6 сравнения, где сравниваются с содержимым регистра 4. Блок 9 читает окончательный результат контроля паспорта и при положительном результате передает на вход формирователя 10 сигнал, по которому на выходе 18 формируется команда Готовность, При отрицательном результате по сигналу с блока 9 на выходе 18 формирователя 10 форьшруется код Отрицательный результат контроля, а на выходе 19 - сигнал Прерывание После выхода команды Готовность блок 9 организует следующий цикл работы.

Очередное слово с выхода коммутатора 1 поступает в регистр 4 и с его выхода - в сумматор 8, где складывается с содержимым сумматора 8„

В очередном такте блок 9 опрашивает схему 13 сравнения на входах которой присутствует информация, о содержимом счетчика 2 и регистра 12 и при наличии нулевого кода результата во всех разрядах, кроме первого, организует через выход 17 коммутатора 3 передачу содержимого регистра 12„ После этого блок 9 опрашивает схему 6 сравнения, увеличивает на единицу содержимое счетчика 2, и одновременно пересьшает содержимое регистра 11 с его инверсных выходов в регистр 12, после чего пересылает содержимое счетчика 2 в регистр 11, В следуклцем такте блок 9 опрашивает схему 5 сравнения адресов, на входе которой присутствует информа- гщя о содерткимом счетчика 2. При несовпадении содержимого счетчика 2

и регистра 7 по сигналу блока 9 на BfJxoAe 18 формирователя 10 устанавлвается команда Готовность для приема очередного слова, и работы повторяется. При совпадений содержимого счетчика 2 и регистра 7 в очередном такте работы блок 9 формируе сигнал блокировки приема сумматором 8 информации из регистра 4, Для формирователя 10 формируется управляющий сигнал, по которому на выходе

18формирователя устанавливается команда Готовность, После приема очередного слова регистром 7 блок 9 опрашивает схему 6 сравнения. В случае сравнения содержимого регистра 4 с содержимым сумматора 8 на выходе

19формирователя 10 устанавливается сигнал Прерывание, а на выходе 18 - код Конец ввода о В случае фиксации несравнения на выходе 19 формирователя 10 устанавливается сигнал Прерывание, а на выходе 18 - код Отрицательный результат- контроля,

В процессе передачи адресов и в паузах (за исключением момента квазитранзитного переноса: регистр 11 - регистр 12; счетчик 2 - регистр 12) достоверность передаваемых адресов непрерывно контролируется схемой 13 сравнения, которая в случае несравнения вырабатывает на своем выходе сигнал ошибки для блока 9. В этом случае блок 9 формирует сигнал управления формирователем 10, по которому на выходе 19 последнего формируется сигнал Прерьшание, а на выходе 18 - Отрицательный результат контроля.

Блок 9 работает следующим образом

Для организации обмена при поступлении на вход 15 команды Начать ввод, являющейся кодом начальной установки счетчика 21, последний начинает счет импульсов от генератора 20. При зток в соответствии с алгоритмом работы изменяется состояние выхода дешифратора 22. На втором выходе дешифратора 22 (группа выходов блока 9) формируется сигнал установки в исходное состояние коммутаторов 1, 3, регистров 4, 7, 11, 12 и счетчика 2 адреса. На шестом выходе дешифратора 22 формируется сигнал, по которому содержимое счетчика 2 увеличивается на единицу. На четвертом выходе дешифратора 22 форм1фуе1;ся сигнал управления работой коммутатора 3.

По единичному сигналу, формируемому на первом выходе депшфратора 22, блок 9 переходит в режим контроля. При контроле паспорта массива и входной информации на втором выходе дешифратора 22 формируется последоваQ тельность импульсов, которая инициирует в соответствующей временной поел ед овательности работу регистра 4 и сумматора 8, В результате на вход блока 9 приходит или единичный сиг5 нал, означакядий положительный результат контроля, или нулевой сигнал, означающий отрицательный результат контроля, и устанавливается на входе элемента НЕ 23 и первом входе элемен0 та И 25с, В случае организации контроля паспорта информа1 1онного массива на вторых входах элементов И 24 и 25 присутствует нулевой сигнал.. При положительном результате контро5 ля (содержимое сумматора 8 сравнилось с контрольной суммой первых двух слов) на входе блока 9 устанавливается единичный сигнал, по которому на выходах элементов ИЛ1 26, И 25 уста0 наашгвается код 00, по которому на выходе 18 формирователя 10 устанав- (ливается команда Готовность.

5

При текущем контроле входной инфор- ма1щи сигнал Готовность формируется при несовпадении содержимого сумматора 8 с содержимым регистра 4 (последнее слово массива). При этом на входах блока 9 устанавливаются нуле- Q вые сигналы, а на соответствующих выходах группы выходов блока 9 - код 00,

При контроле схемой 5 сравнения . совпадения содержимого счетчика 2 с конечным адресом, заложенным в регистр 7, на входе блока 9 устанавливается единичный сигнал. На втором выходе дешифратора 22 формируется последовательность импульсов, обеспечивающая контроль содержимого схемой 6 сравнения: вырабатьгоается сигнал блокировки приема информации сумматором 8 из регистра 4 и управляющие сигналы, обеспечиваюш ге сравнение содержимого сумматора 8 и регистра 4.

8случае несравнения на входе блока

9устанавливается нулевой сигнал,

а на соответствующих выходах группы выходов блока 9 - код 01, по кото-

0

5

рому формирователь 10 на выходе формирует сигнал Прерывание.

При положительном результате контроля схемой 6 сравнения на входе блока 9 управления устанавливается единичный сигнал. На соответствуютхих вькодах групп выходов блока 9 формируется код 10, означающий конец ввода массива. Формирователь 10 выставляет на выходе 18 команду Конец ввода.

Контроль схемой 13 сравнения осуществляется по сигналам, формируемым

10

Формула изобретения

1. Устройство ;1ля сотгряжения пе- ри(5)ерийного устройства с ЭВМ, содер- жшчее коммутатор входной информа1даи, счетчик адресов, коммутатор адресов, регистр информации, регистр конечного адреса, первую схему сравнения адресов, схему сравнения информации, сумматор, блок управления, формирователь управляющих слов, причем ин- формационньй вход коммутатора входной информации является входом устна пятом выходе дешифратора 22, кото- 45 ройства для подключения .информацион- рьй поступает на вход схемы 13. Уп-кого выхода периферийного устройства,

равляющий вход схемы 13 управляет подсоединением для контроля либо входных сигналов с регистра 12 либо вход- Hbjx сигнап9В от коммутатора 3,

Формирователь 10 управляющих слов обрабатьшает сигналы, поступаю1дие на его вход с блока 9. По сигналу Отрицательный результат контроля, посту- пающег-iy на вход дешифратора 27, на первом выходе последнего формируется сигнал запуска генератора 28, на третьем выходе форм-груется соответствующий код, который устанавливается на входе сдвигового регистра 30. На втором выходе депшфратора 27 формируется управляющий код для счетчика 29, Счетчик 29 управляет работой деиаифратора 31 j управляющего, в свою очередь, продолжительностью генера- 1ЩИ генератора 28, по выходным импульсам которого счетчик 29 ведет счет тактов, а из сдвигового регистра 30 считывается информация. При этом, на выходе 19 прерываний формирователя 10 устанавливается код Пре- рьшание, а депшфратор 32 формирует на выходе 18 команду Отрицательньй результат контроля.

По окончании передачи информации из сдвигового регистра 30 депшфратор 31 запрещает работу генератора 28,

По сигналу Готовность, поступающему на вход дешифратора 27, в регистр 30 заносится информация, при считывании которой на выходе 18 устанавливается команда Готовность . По сигналам Положительный результат контроля и Сравнение адресов в регистр 30 заносится информация, при считьтании которой на выходе 18 команд формирователя 10 устанавливается код Конец ввода.

20

25

30

управляЮ1 ще входы коммутатора входной информаи;ии, .регистра инф.ормации, регистра конечного адреса, разрешающий вход сумматора и вход формирователя управляющих слов, установочньй вход счетчика адресов соединены с группой выходов блока управления, первьм и второй вькоды которого соединены соответственно со счетным входом счетчика адресов и управляюЕДИм входом коммутатора адресов, вход команды блока управления является входом устройства для подютючения командного выхода ЭВМ, а первьм и второй входы состояния соединены соответственно с выходами схемы сравнения информации и первой схемы сравнения адресов, первый и второй входы которой соединены соответственно с первыми выходами счетчика адреса и регистра конечного адреса, информационный вход и второй выход которого соединены соответственно с первым выходом коммутатора входной информации и первым информационным входом сумматора, выход, второй и третий информационные входы которого соединены соответственно с первым входом схемы срав- g рения информации, первьш выходом регистра информации и вторым вькодом счетчика адреса, вход на:чальной установки которого соединен с вторым вькпдом коммутатора входной информации, третий которого соединен с информационным входом регистра ин- форма1Д 1и, второй выход которого является выходом устройства для подключения к информационному входу ЭВМ, а третий выход соединен с вторым входом схемы сравнения информа- lyra, выход коммутатора адресов является выходом устройства для подключения к адресному входу ЭВМ, первый

35

40

50

55

Формула изобретения

1. Устройство ;1ля сотгряжения пе- ри(5)ерийного устройства с ЭВМ, содер- жшчее коммутатор входной информа1даи, счетчик адресов, коммутатор адресов, регистр информации, регистр конечного адреса, первую схему сравнения адресов, схему сравнения информации, сумматор, блок управления, формирователь управляющих слов, причем ин- формационньй вход коммутатора входной информации является входом устройства для подключения .информацион- кого выхода периферийного устройства,

0

5

0

управляЮ1 ще входы коммутатора входной информаи;ии, .регистра инф.ормации, регистра конечного адреса, разрешающий вход сумматора и вход формирователя управляющих слов, установочньй вход счетчика адресов соединены с группой выходов блока управления, первьм и второй вькоды которого соединены соответственно со счетным входом счетчика адресов и управляюЕДИм входом коммутатора адресов, вход команды блока управления является входом устройства для подютючения командного выхода ЭВМ, а первьм и второй входы состояния соединены соответственно с выходами схемы сравнения информации и первой схемы сравнения адресов, первый и второй входы которой соединены соответственно с первыми выходами счетчика адреса и регистра конечного адреса, информационный вход и второй выход которого соединены соответственно с первым выходом коммутатора входной информации и первым информационным входом сумматора, выход, второй и третий информационные входы которого соединены соответственно с первым входом схемы срав- g рения информации, первьш выходом регистра информации и вторым вькодом счетчика адреса, вход на:чальной установки которого соединен с вторым вькпдом коммутатора входной информации, третий которого соединен с информационным входом регистра ин- форма1Д 1и, второй выход которого является выходом устройства для подключения к информационному входу ЭВМ, а третий выход соединен с вторым входом схемы сравнения информа- lyra, выход коммутатора адресов является выходом устройства для подключения к адресному входу ЭВМ, первый

5

0

50

55

и второй выходы формирователя командных слов являются соответственно выходами устройства для подключения входа команд и входа прерьта- ния ЭВМ, отличающееся тем, что, с целью повьйпения достоверности передаваемой адресной информации, в него введены буферный регистр, регистр адреса и вторая схема сравнения адресов, причем первьй - третий информационные входы и.выход второй схемы сравнения адресов соединены соответственно с. инверсным выходом счетчика адресов, с выходом регистра адресов, соединенным с информационным входом коммутатора адресов, с выходом комму- татора адресов, с третьим входом СОСТОЯНИЯ блока управления, третьим вькодом подключенного к управляющему входу второй схемы сравнения адресов, установочные и управляющие входы буферного регистра и регистра адресов соединены соответственно с группой выходов и первым выхо- дом блока управления, инверсный выход счетчика адресов соединен с инверсным информационным входом буферного регистра, инверс- ньй выход которого соединен с инфор ма19 онным входом регистра адресов.

А517078

2. Устройство по п. 1, о т л и- чающееся тем, что блок управления содержит генератор меток, счетчик, дешифратор, два элемента И, элемент ИЛИ и элемент НЕ, причем вход элемента НЕ соединен с первым входом первого элемента И и является первым входом состояния

Q блока управления, а выход соединен с первым входом второго элемента И, вторые входы первого и второго элементов И соединены с вторым входом блока управления, третьи входы единены с первым выходом дешифратора, а выходы первого элемента И, элемента ИЛИ и второй выход дешифратора образуют группу выходов блока управления, первьй вход элемента ИЛИ является третьим входом состояния блока управления, а второй вход соединен с выходом второго элемента И, вход начальной установки счетчика является входом команды блока управ25 ления, а счетный и установочный входы счетчика и выход соединены соответственно с выходом генератора меток третьим выходом и входом дешифратора, четвертьй, пятый и шестой

30 выходы которого являются соответственно вторым, третьим и первым выходами блока управления

20

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1980 |

|

SU962904A1 |

| Электронная вычислительная машина | 1988 |

|

SU1520533A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

| Устройство для имитации неисправностей | 1985 |

|

SU1283775A1 |

| Устройство таймеров | 1983 |

|

SU1163309A1 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Устройство для изучения языка | 1990 |

|

SU1785029A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1985 |

|

SU1437907A1 |

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах для сопряжения, например, периферийного устройства, осуществляющего последовательную выдачу данных, с оперативной памятью. Пель изобретения - обеспечение достоверности передаваемой адресной информации. Цель достигается тем, что в устройство, содержащее коммутатор 1 входной информации, счетчик 2 адресов, коммутатор 3 адресов, блок 9 управления,(формирователь 10 управляющих слов, регистр 4 информации, сумматор 8, регистр 7 конечного адреса, схему 6 сравнения информации, первую схему 5 сравнения адресов, введены инверсно-инвертирующий буферный регистр 11, регистр 12 адреса, вторая схема 13 сравнения адресов Благодаря тому, что передача адреса из счетчика 2 в регистр 4 адреса производится через инверсно- инвертируюррда буферный регистр 11, практически исключается искажение адреса на этапе промежуточной передачи, за счет чего достоверность передаваемой информахщи определяется регистром 12 адреса и коммутатором 3 адресов. Это позволяет для подтверждения достоверности передаваемого адреса ограничиться сравнением содержимого счетчика 2 адресов с информацией, передаваемой с выхода 17, и (в случае отрицательного результата) с содержимым регистра 12 адреса. 1 з.п.ф-лы, 3 ил о i О) ел о «ч

J

Фив. 2

Фие.д

| Устройство для тревожной сигнализации емкостного типа | 1983 |

|

SU1117672A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для сопряжения | 1980 |

|

SU962904A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-01-15—Публикация

1987-03-23—Подача