входам коммутатора, выход которого соединен с информационным входом сумматора по модулю два. Выход элемента задержки подключен к тактовому входу регистра сдвига.

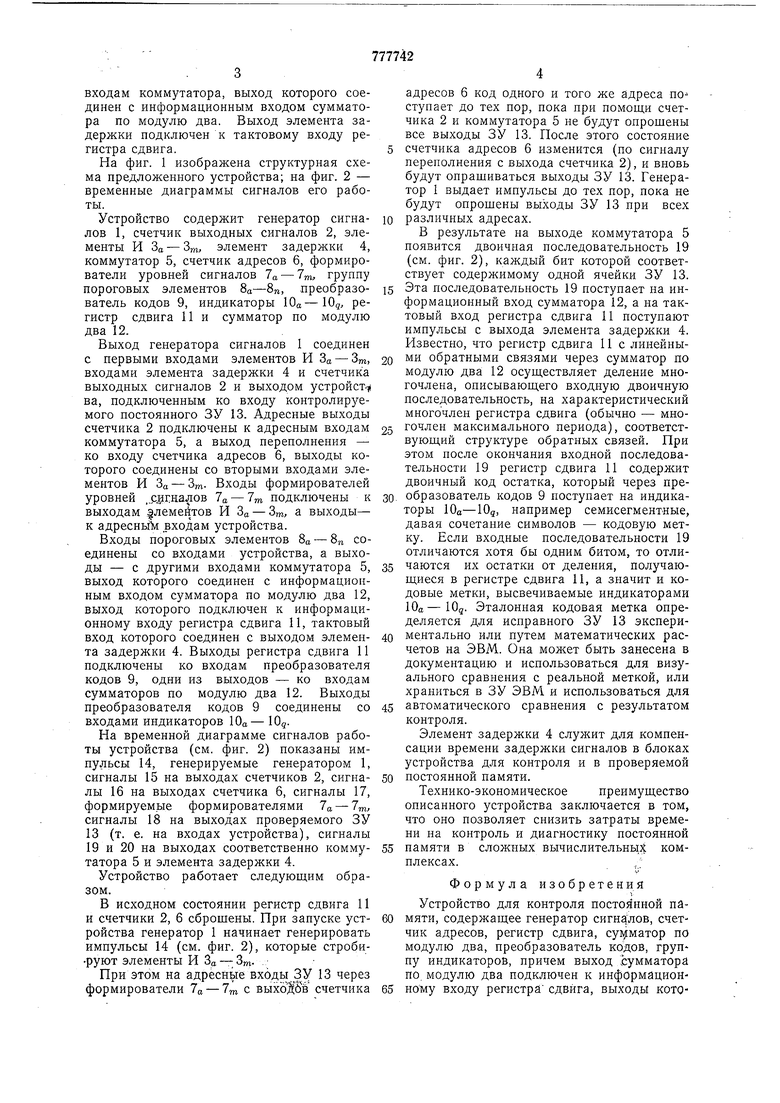

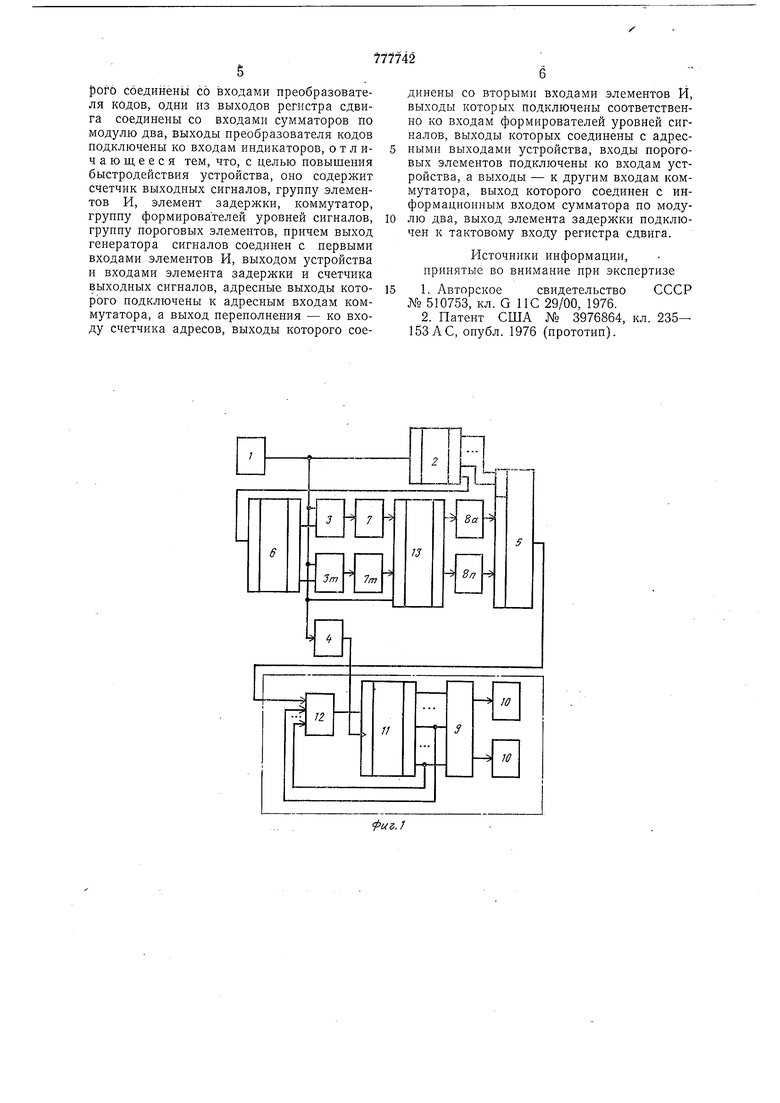

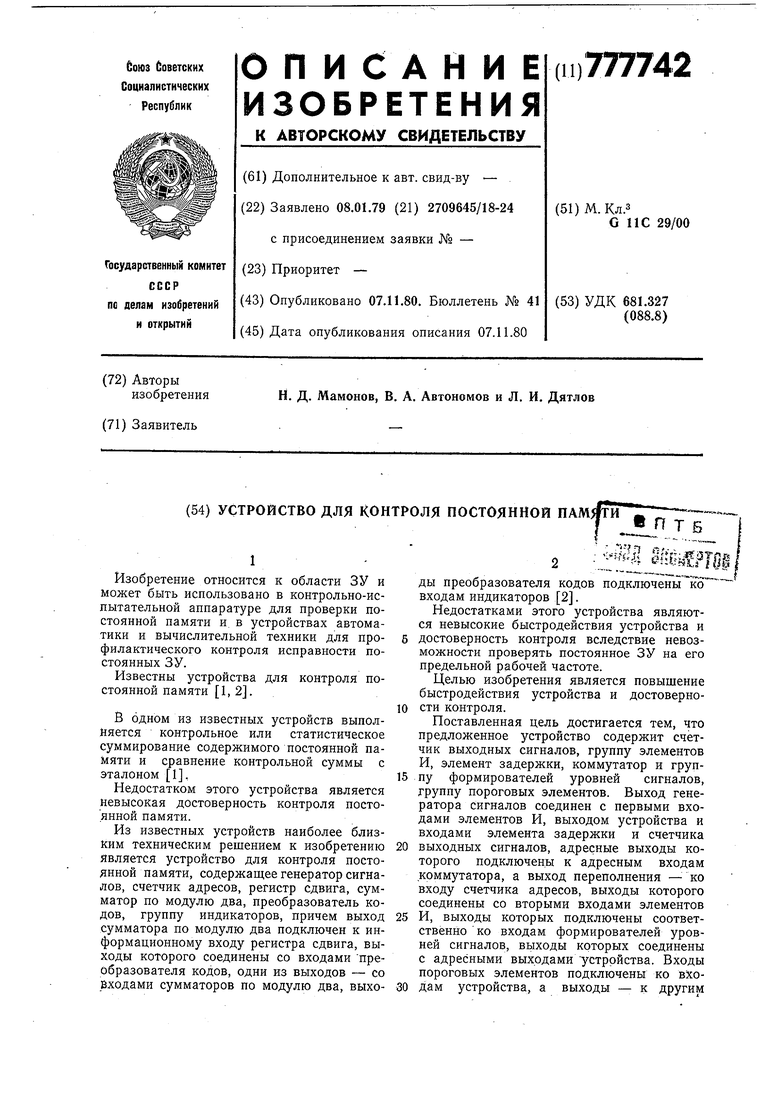

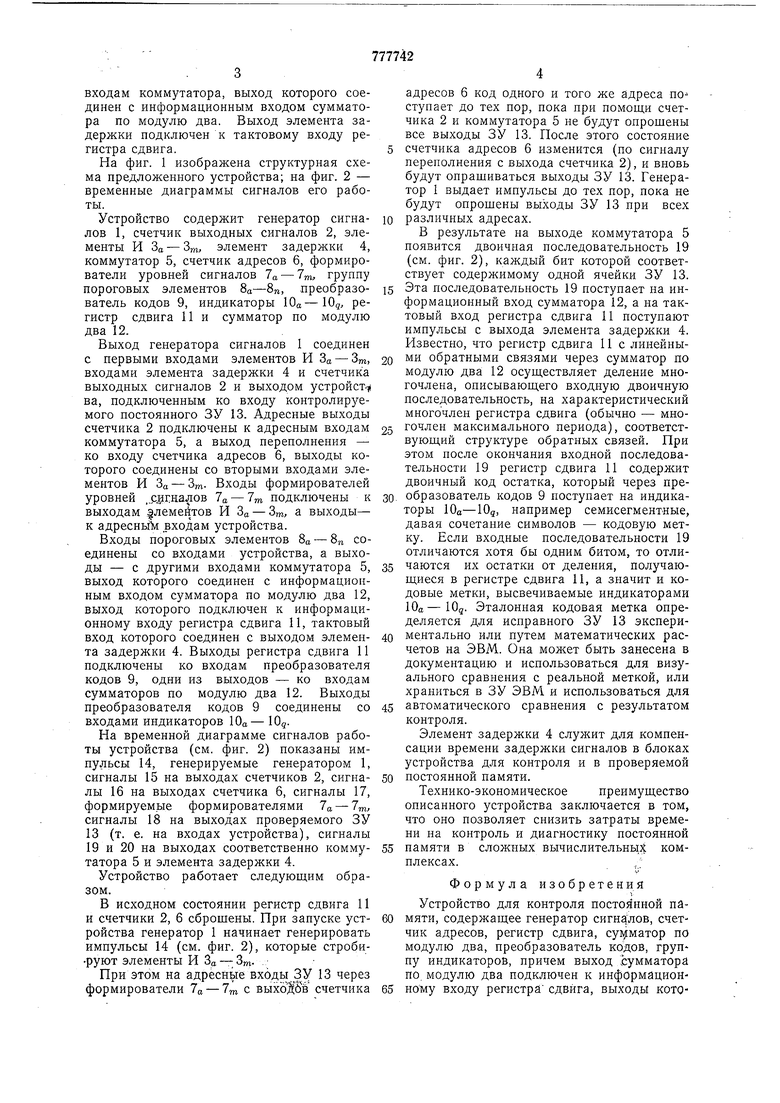

На фиг. 1 изображена структурная схема предложенного устройства; на фиг. 2 - временные диаграммы сигналов его работы.

Устройство содержит генератор сигналов 1, счетчик выходных сигналов 2, элементы И За - 3т, элемент задержки 4, коммутатор 5, счетчик адресов 6, формирователи уровней сигналов 7а - 1т, группу пороговых элементов 8а-8«, преобразователь кодов 9, индикаторы Юд-Юд, регистр сдвига 11 и сумматор по модулю два 12.

Выход генератора сигналов 1 соединен с первыми входами элементов И За - 3т, входами элемента задержки 4 и счетчика выходных сигналов 2 и выходом устройст-ii ва, подключенным ко входу контролируемого постоянного ЗУ 13. Адресные выходы счетчика 2 подключены к адресным входам коммутатора 5, а выход переполнения - ко входу счетчика адресов 6, выходы которого соединены со вторыми входами элементов И За - 3т. Входы формирователей уровней ..сигналов 7а - 1т подключены к выходам элементов И За - 3т, а выходы- к адресный входам устройства.

Входы пороговых элементов 8а - 8„ соединены со входами устройства, а выходы - с другими входами коммутатора 5, выход которого соединен с информационным входом сумматора по модулю два 12, выход которого подключен к информационному входу регистра сдвига 11, тактовый вход которого соединен с выходом элемента задержки 4. Выходы регистра сдвига 11 подключены ко входам преобразователя кодов 9, одни из выходов - ко входам сумматоров по модулю два 12. Выходы преобразователя кодов 9 соединены со входами индикаторов 10а- Юд.

На временной диаграмме сигналов работы устройства (см. фиг. 2) показаны импульсы 14, генерируемые генератором 1, сигналы 15 на выходах счетчиков 2, сигналы 16 на выходах счетчика 6, сигналы 17, формируемьге формирователями la, -1т, сигналы 18 на выходах проверяемого ЗУ 13 (т. е. на входах устройства), сигналы 19 и 20 на выходах соответственно коммутатора 5 и элемента задержки 4.

Устройство работает следующим образом.

В исходном состоянии регистр сдвига 11 и счетчики 2, 6 сброшены. При запуске устройства генератор 1 начинает генерировать импульсы 14 (см. фиг. 2), которые стробируют элементы И За -3т. .;

При этом на адресные входь ЗУ 13 через формирователи 7а - 7т с выхоЙбй счетчика

адресов 6 код одного и того же адреса поступает до тех пор, пока при помощи счетчика 2 и коммутатора 5 не будут опрошены все выходы ЗУ 13. После этого состояние счетчика адресов 6 изменится (по сигналу переполнения с выхода счетчика 2), и вновь будут опрашиваться выходы ЗУ 13. Генератор 1 выдает импульсы до тех пор, пока не будут опрошены выходы ЗУ 13 при всех

различных адресах.

В результате на выходе коммутатора 5 появится двоичная последовательность 19 (см. фиг. 2), каждый бит которой соответствует содержимому одной ячейки ЗУ 13.

Эта последовательность 19 поступает на информационный вход сумматора 12, а на тактовый вход регистра сдвига 11 поступают импульсы с выхода элемента задержки 4. Известно, что регистр сдвига 11 с линейными обратными связями через сумматор по модулю два 12 осуществляет деление многочлена, описывающего входную двоичную последовательность, на характеристический многочлен регистра сдвига (обычно - многочлен максимального периода), соответствующий структуре обратных связей. При этом после окончания входной последовательности 19 регистр сдвига 11 содержит двоичный код остатка, который через преобразователь кодов 9 поступает на индикаторы 10а-lOg, например семисегментные, давая сочетание символов - кодовую метку. Если входные последовательности 19 отличаются хотя бы одним битом, то отличаются их остатки от деления, получающиеся в регистре сдвига 11, а значит и кодовые метки, высвечиваемые индикаторами 10а-lOg. Эталонная кодовая метка определяется для исправного ЗУ 13 экспериментально или путем математических расчетов на ЭВМ. Она молсет быть занесена в документацию и использоваться для визуального сравнения с реальной меткой, или храниться в ЗУ ЭВМ и использоваться для

автоматического сравнения с результатом контроля.

Элемент задержки 4 служит для компенсации времени задержки сигналов в блоках устройства для контроля и в проверяемой

постоянной памяти.

Технико-экономическое преимущество описанного устройства заключается в том, что оно позволяет снизить затраты времени на контроль и диагностику постоянной

памяти в сложных вычислительных комплексах..;

Формула изобретения

Устройство для контроля постоянной памяти, содержащее генератор сигналов, счетчик адресов, регистр сдвига, су1 матор по модулю два, преобразователь кодов, груп пу индикаторов, причем выход Ьумматора по, модулю два подключен к информационному входу регистра сдвига, выходы котоpofo соединены со входами преобразователя кодов, одни из выходов регистра сдвига соединены со входами сумматоров по модулю два, выходы преобразователя кодов подключены ко входам индикаторов, отличающееся тем, что, с целью повышения быстродействия устройства, оно содержит счетчик выходных сигналов, группу элементов И, элемент задержки, коммутатор, группу формирователей уровней сигналов, группу пороговых элементов, причем выход генератора сигналов соединен с первыми входами элементов И, выходом устройства и входами элемента задержки и счетчика выходных сигналов, адресные выходы которого подключены к адресным входам коммутатора, а выход переполнения - ко входу счетчика адресов, выходы которого соединены со вторыми входами элементов И, выходы которых подключены соответственно ко входам формирователей уровней сигналов, выходы которых соединены с адресными выходами устройства, входы пороговых элементов подключены ко входам устройства, а выходы - к другим входам коммутатора, выход которого соединен с информационным входом сумматора по модулю два, выход элемента задержки подключен к тактовому входу регистра сдвига.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 510753, кл. G ПС 29/00, 1976.

2.Патент США № 3976864, кл. 235- 153 А С, опубл. 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1184014A1 |

| Устройство для коррекции ошибок в блоках памяти | 1985 |

|

SU1257708A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

| Устройство для измерения параметров газовых сред | 1980 |

|

SU894527A1 |

| Устройство для контроля постоянной памяти | 1984 |

|

SU1195392A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| Функциональный преобразователь многих перемнных | 1981 |

|

SU1115068A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

....ji.ja.,.n п.,

..J n

. --L

..,x

/7

.U.,.

-JuTLfn J J -J....-™-™

J- 4 L-JlJrLr.JrL

; fjl I it-i I I ft-j I iti

Jj U,L,J, . г h-LinJUTJ-lJTr Jl

Фи.2

Авторы

Даты

1980-11-07—Публикация

1979-01-08—Подача