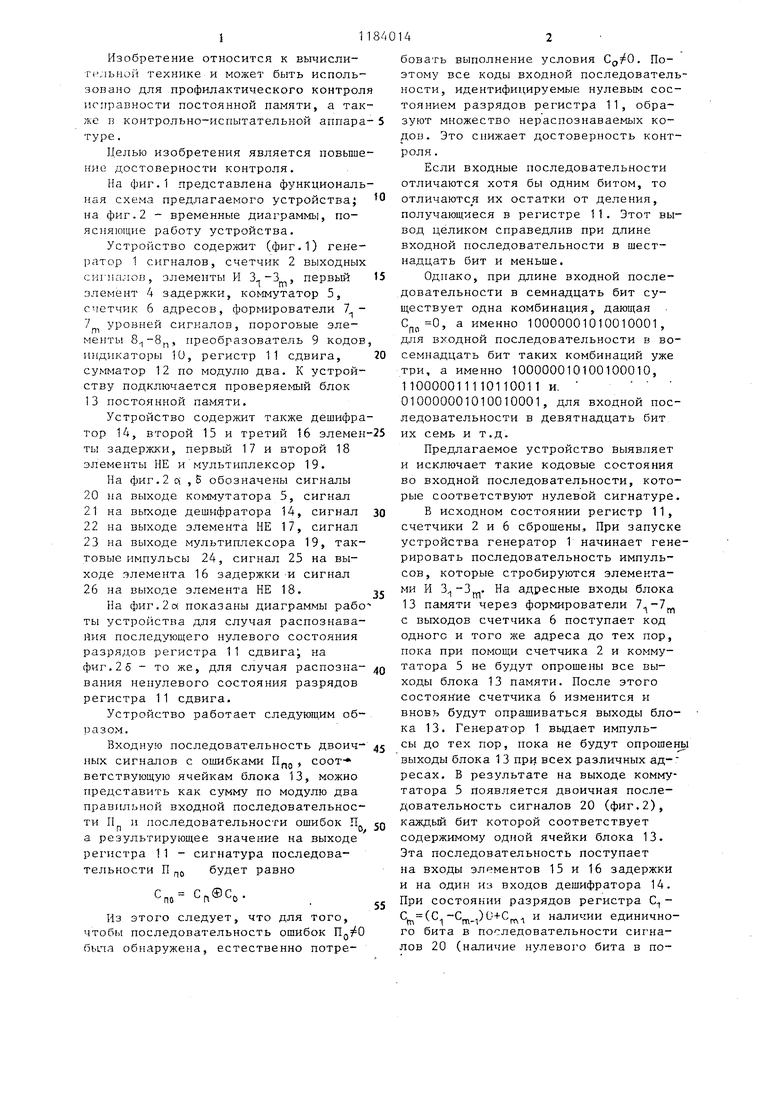

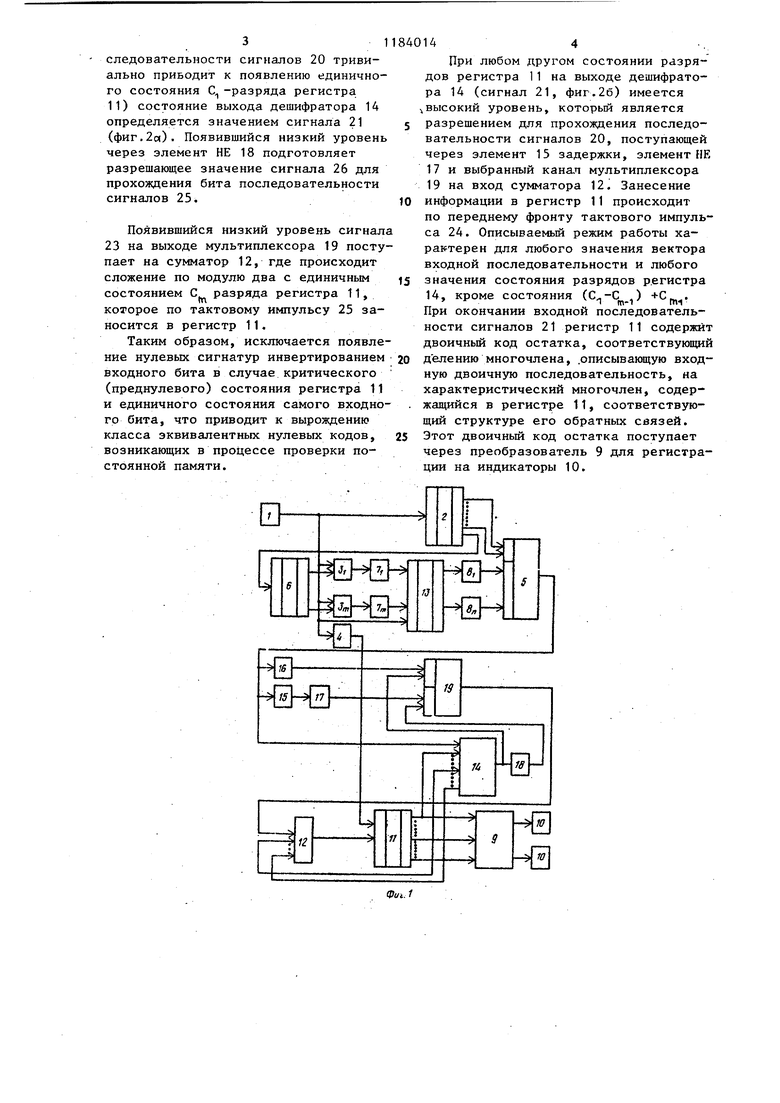

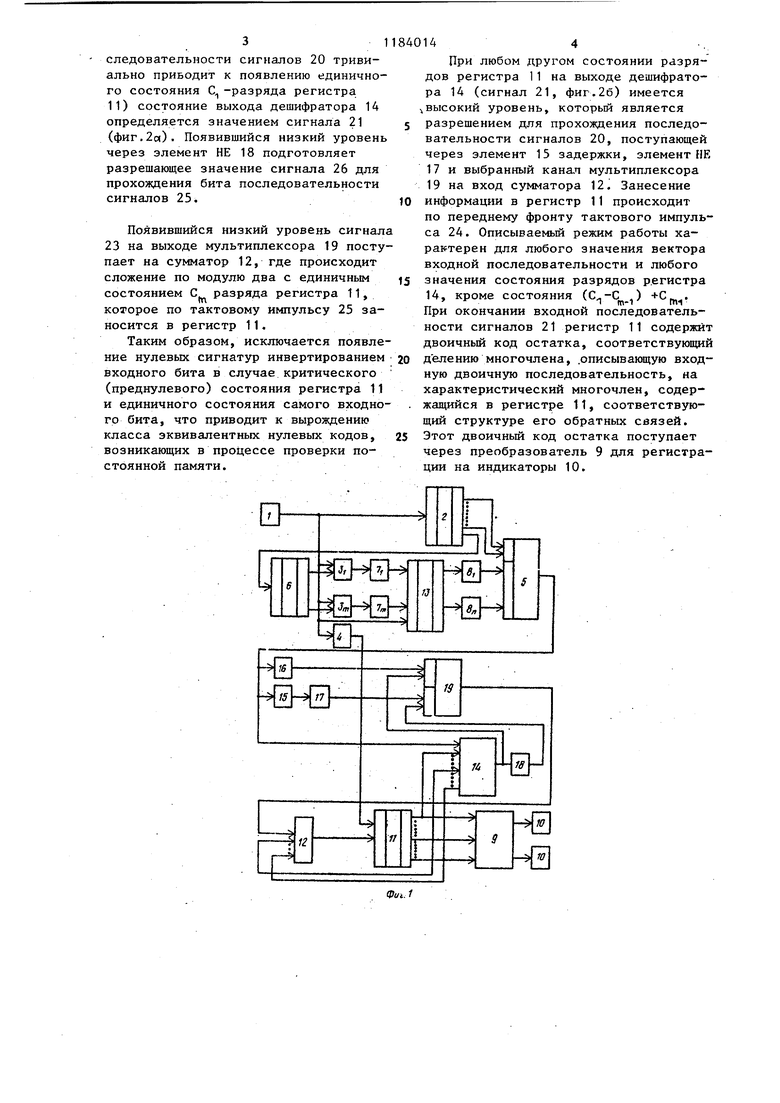

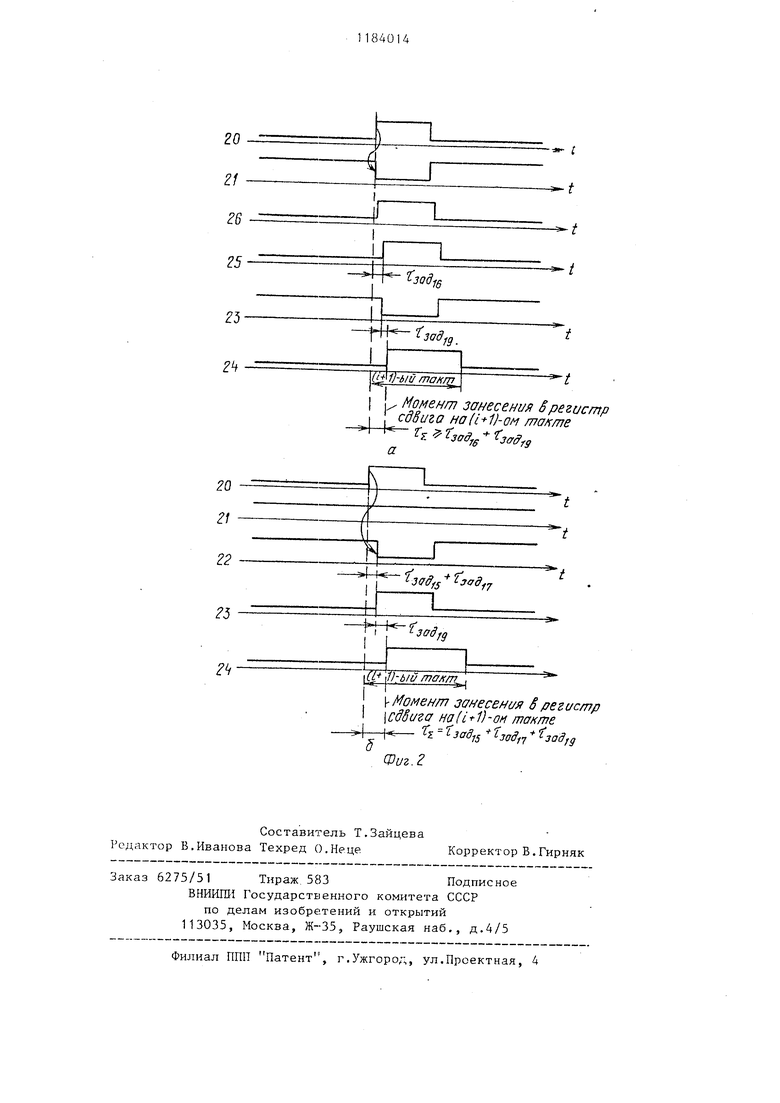

Изобретение относится к вычислигслыюн технике и может быть использовано для профилактического контрол исправности постоянной памяти, а так же п контрольно-испытательной аппара туре. Целью изобретения является повыше ние достоверности контроля. На фиг.1 представлена функциональ ная схема предлагаемого устройства; на фиг.2 - временные диаграммы, поясняющие работу устройства. Устройство содержит (фиг.1) генератор 1 сигналов, счетчик 2 выходных сигналов, элементы И , первый элемент 4 задержки, коммутатор 5, счетчик 6 адресов, формирователи , уровней сигналов, пороговые элементы , преобразователь 9 кодов индикаторы 10, регистр 11 сдвига, сумматор 12 по модулю два. К устройству подключается проверяемый блок 13 постоянной памяти. Устройство содержит также дешифра тор 14, второй 15 и третий 16 элемен ты задержки, первый 17 и второй 18 элементы НЕ и мультиплексор 19, На фиг.2 ft ,5 обозначены сигналы 20на выходе коммутатора 5, сигнал 21на выходе дешифратора 14, сигнал 22на выходе элемента НЕ 17, сигнал 23на выходе мультиплексора 19, тактовые импульсы 24, сигнал 25 на выходе элемента 16 задержки и сигнал 26 на выходе элемента НЕ 18, На фиг.2о( показаны диаграммы рабо ты устройства для случая распознавания последующего нулевого состояния разрядов регистра 1 1 сдвига;, на фиг,25 - то же, для случая распознавания ненулевого состояния разрядов регистра 11 сдвига. Устройство работает следующим образом. Входную последовательность двоичных сигналов с ошибками П,, , соот- ветствующую ячейкам блока 13, можно представить как сумму по модулю два правильной входной последовательноети II и последовательности ошибок П. П0 а результирующее значение на выходе регистра 11 - сигнатура последовательности П будет равно ,, Из этого следует, что для того, последовательность ошибок была обнаружена, естественно потребовать выполнение условия €,-,/0, Поэтому все коды входной последовательности, идентифицируемые нулевым состоянием разрядов регистра 11, образуют множество нераспознаваемых кодов. Это снижает достоверность контроля . Если входные последовательности отличаются хотя бы одним битом, то отличаются их остатки от деления, получающиеся в регистре 11. Этот вывод целиком справедлив при длине входной последовательности в шестнадцать бит и меньше. Однако, при длине входной последовательности в семнадцать бит существует одна комбинация, дающая ,0, а именно 10000001010010001, для входной последовательности в восемнадцать бит таких комбинаций уже три, а именно 100000010100100010, 110000011110110011 и. 010000001010010001, для входной последовательности в девятнадцать бит их семь и т.д. Предлагаемое устройство выявляет и исключает такие кодовые состояния во входной последовательности, которые соответствуют нулевой сигнатуре. В исходном состоянии регистр 11, счетчики 2 и 6 сброшены. При запуске устройства генератор 1 начинает генерировать последовательность импульсов, которые стробируются элементами И . На адресные входы блока 13 памяти через формирователи с выходов счетчика 6 поступает код одного и того же адреса до тех пор, пока при помощи счетчика 2 и коммутатора 5 не будут опрошены все выходы блока 13 памяти. После этого состояние счетчика 6 изменится и вновь будут опрашиваться выходы блока 13, Генератор 1 выдает импульсы до тех пор, пока не будут опрошень выходы блока 1 3 при всех различных адресах. В результате на выходе коммутатора 5 появляется двоичная последовательность сигналов 20 (фиг,2), каждьм бит которой соответствует содержимому одной ячейки блока 13. Эта последовательность поступает на входы элементов 15 и 16 задержки и на один из входов дешифратора 14. При состоянии разрядов регистра (.,)0+Cf и наличии единичного бита в последовательности сигналов 20 (наличие } улевого бита в последовательности сигналов 20 тривиально приводит к появлению единичного состояния С -разряда регистра 11) состояние выхода дешифратора 14 определяется значением сигнала 21 (фиг.2о(). Появившийся низкий уровень через элемент НЕ 18 подготовляет разрешающее значение сигнала 26 для прохождения бита последовательности сигналов 25.

Появившийся низкий уровень сигнала 23 на выходе мультиплексора 19 поступает на сумматор 12, где происходит сложение по модулю два с единичным состоянием С разряда регистра 11, которое по тактовому Импульсу 25 заносится в регистр 11.

Таким образом, исключается появление нулевых сигнатур инвертированием входного бита в случае критического (преднулевого) состояния регистра 11 и единичного состояния самого входного бита, что приводит к вырождению класса эквивалентных нулевых кодов, возникающих в процессе проверки постоянной памяти.

При любом другом состоянии разрядов регистра 11 на выходе дешифратора 14 (сигнал 21, фиг.2б) имеется высокий уровень, который является разрешением для прохояодения последовательности сигналов 20, поступающей через элемент 15 задержки, элемент НЕ 17 и выбранный канат мультиплексора 19 на вход сумматора 12. Занесение информации в регистр 11 происходит по переднему фронту тактового импульса 24. Описываемый режим работы характерен для любого значения вектора входной последовательности и любого значения состояния разрядов р.егистра 14, кроме состояния () С. При окончании входной последовательности сигналов 21 регистр 11 содержит двоичный код остатка, соответствующий делению многочлена, .описывающую входную двоичную последовательность, на характеристический многочлен, содержащийся в регистре 11, соответствующий структуре его обратных связей. Этот двоичный код остатка поступает через преобразователь 9 для регистрации на индикаторы 10.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU868843A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для преобразования форматов слов двоичной последовательности | 1988 |

|

SU1513436A1 |

| Устройство для контроля и диагностики цифровых блоков | 1983 |

|

SU1167610A1 |

| Устройство для контроля и диагностики цифровых блоков | 1982 |

|

SU1067506A1 |

| Микропрограммное устройство управления с контролем | 1989 |

|

SU1702370A1 |

| Устройство для контроля оперативных накопителей | 1989 |

|

SU1705874A1 |

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСТОЯННОЙ ПАМЯТИ, содержащее генератор сигналов, счетчик выходных сигналов, элементы И, первый элемент задержки, коммутатор, счетчик адресов, формирователи уровней сигналов, пороговые элементы, преобразователь кодов, индикаторы, регистр сдвига и сумматор по модулю . два, причем выход генератора сигналов соединен с первыми входами элементов И, входами первого элемента задержки и счетчика выходных сигналов, выходы которого подключены к одним из входов коммутатора, а выход переполнения соединен с входом счетчика адресов, выходы которого подключены к вторым входам элементов И, выходы которых соединены с входами формирователей уровней сигналов, выход первого элемента задержки подключен к тактовому входу регистра сдвига, информационный вход которого соединен с выходом сумматора по модулю два, а выходы подключены к входам преобразователя кодов, выходы которого соединены с входами индикаторов, одни из выходов регистра сдвига подключены к одним из входов сумматора по модулю два, другие входы коммутатора соединены с выходами пороговых элементов, входы которых являются входами устройства, адресными и тактовым выходами которого являются соответственно выходы формирователей уровней сигналов и выход генератора сигналов, отличающееся тем, что, с целью повышеi ния достоверности контроля, в него введены мультиплексор, дешифратор, (Л элементы НЕ, второй и третий элементы задержки, причем выход второго элемента задержки подключен к входу первого элемента НЕ, выход которого и выход третьего элемента задержки соединены с входами мультиплексора, вькод которого подключен к другому 00 входу сумматора по модулю два, выход i4 дешифратора соединен с первым управляющим входом мультиплексора и входом второго элемента НЕ, выход кото4 рого подключен к второму управляющему входу мультиплексора, один из входов дешифратора и входы второго и третьего элементов задержки соединены с выходом коммутатора, другие входы дешифратора подключены к выходам регистра сдвига.

| Устройство для контроля постоянных запоминающих блоков | 1974 |

|

SU510753A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля постоянной памяти | 1979 |

|

SU777742A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-10-07—Публикация

1984-05-22—Подача