(54) УСТ ГОЙСТВО ДЛЯ ОБМЕНА ДАННЫМИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для управления вводом-выводом | 1989 |

|

SU1735859A1 |

| Устройство для сопряжения цифровой вычислительной машины с периферийными устройствами | 1980 |

|

SU962899A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Пульт управления мультипроцессорной вычислительной машины | 1980 |

|

SU911527A1 |

| Устройство для сопряжения периферийной системы с электронной вычислительной машиной | 1975 |

|

SU554534A1 |

| Периферийный процессор для обработки сигналов | 1985 |

|

SU1368889A1 |

| Устройство для сопряжения | 1977 |

|

SU739511A1 |

| Устройство для сопряжения периферийного устройства с ЭВМ | 1988 |

|

SU1596339A1 |

| Устройство для сопряжения | 1978 |

|

SU736086A1 |

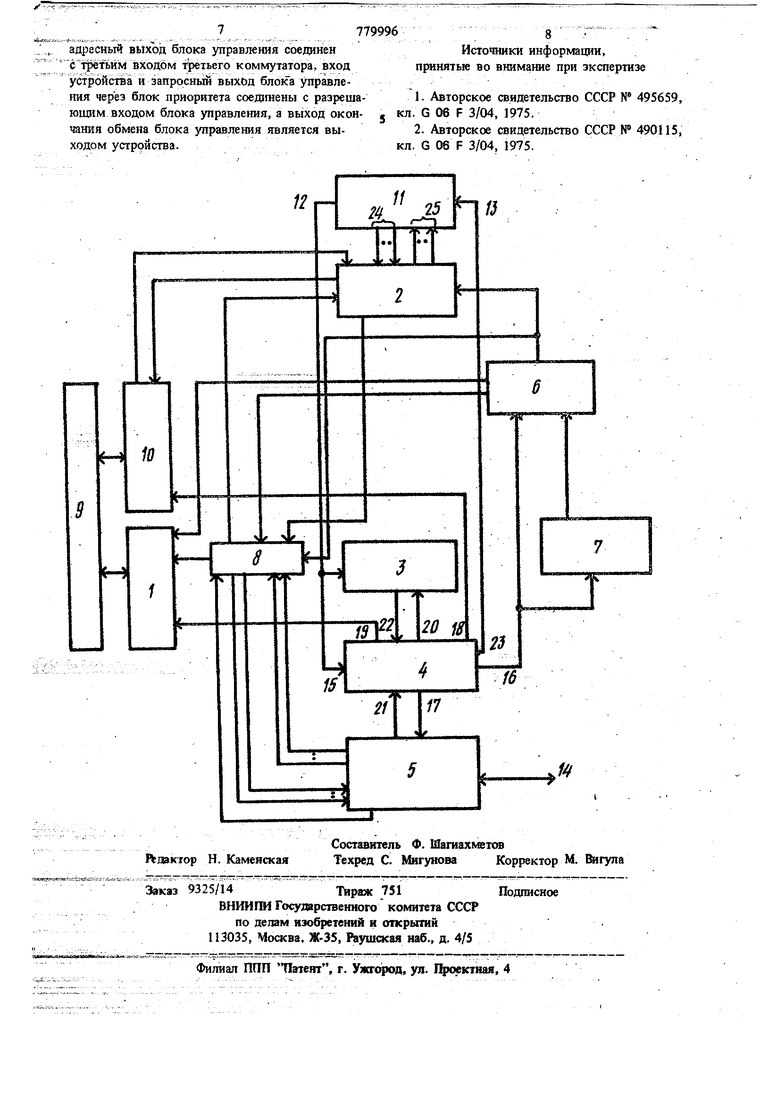

Изобретение относится к области вычислительной техники и может быть использовано в гаютемах сбора и обработки информации дпг обмена люжду прецессором вычислительной машины с периферийным устройством. Ижестио устрсйство для обмена данными, содержащее схему логических операций, два регистра команд, регистр связи с процессором, блок обработки инструкций, две схемы формирования адреса, две схемы модис икации, схему селекции, регистры датшх, запросов, маски запросов, разрешения реализации запроса, дешифраторы кода операций, адреса устройства ввода-вьшода, схему приоритета, ишфратор адреса, выходные схемы и схемы объединения 1 Недостаток этого устройства состоит в том; что оно требует больших затрат оборудования при его реализации. Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для обмена данными, содержащее первый регистр, первый выход которого соединен с первым входом второго регистра, блок управления, командный вход которого является входом уст йства, а первый запускающий выход соединен с первым входом первого коммутатора, блок сопряжения и блок П1жорнтета, причем первый выход первого коммутатора соединен со. вторым входом второго регистра, первый выход которого соединен с первым входом первого регистра, группа входов и группа выходов первого регистра являются соответственио группой входов н группой выходов устройства, вход - выход блока сопряжения является входом - выходом устройства, кроме того, выход блока сопряжения соединен со входом первого коммутатора и со входом блока приоритета 2}. Недостаток такого устройства состоит в том, что оно имеет незначительное быстродействие, поскольку скорость обмена ограничивается скоростью наиболее медленного из двух обменивающихся данными абонентов. Цель изобретеиия - повышение быстродействия. Поставленная цель достигается тем, что в устройство обмена данными, содержащее первый регистр, первый выход которого соединен с первым входом второго регистра, блок управления, командный вход которого является входом устройства, а первый запускающий выход соединен с первым входом первого коммутатора, блок сопряже1шя и блок приоритета, причем первый выход первого коммутатора йоедаиен со вторым входом второго регистра,первый выход которого соединен с первым входом первого регистра, группа ВХОДОВигруппа выходов первого регистра является соответственно группой входов и группой выходов устройства, вход-выход блока сопряжения является входом-выходом устройства введены блок памяти, второй и третий коммутаторы и синхронизатор, причем первый запускающий выход блока управления через синхро1тзалор соединен со вторым входом первого коммутатора, второй выход которого соединен со вторым входом первого регистра и с третьим входом второго регистра, второй выход которого соединен с первым входом третьего коммутатора, третий выход первого коммутатора соединен со вторым входом третьего коммутатора, вход-выход которого соединен с первым выходом-входом блока памяти, второй вход-выход блока памяти соединен с выходомвходом второго коммутатора, первый, второй входы и выход которого соединен соответствен . но с первым адресным выходом блока управле ния, со вторым выходом и третьим входом первого регистра, группа входов и группа выходов .блока сопряжёция соединены соответ-, ствённо с грутшои выходов ц группой входов второго регистра, первый вход, первый и второй выходы блока сопря;:)енйя с«эеДЙ1йнЬ соответственно со вторым запускающим , выходом и запросным входом блока управления и с чет вертым входом второго регистра, второй адресный выход блока- управления соединен с третьим входом третьего коммутатора, вход устройства и запросный выход блока управления через блок приоритета соединень с разреш ющим входом блока управления, а выход окончания обмена блока управления является выходом устройства. Структурная схема предлагаемого устройств представлена на чертеже. Устройство для обмена даннь1МИ соДёрзкит коммутатор 1, регистр 2, блок приоритета 3, блок управления 4, блок 5 сопряжеш я, коммутатор 6, синхронизатор 7, регистр 8, блок 9 памяти, коммутатор 10. Позицией-11 обозначен центральный процессор, позициями 12-14 вход устройства, выход устройства и вход-выход устройства. Входы и выходы блок управления обозначены следующим образом: 13- кошндньш вход, 16, 17 - первый и вто рой запускающие выходы, 18, 19 - первьгй и второй адресные выходы, 20 - запросный вы4. ход, 21 - запросный вход, 22 - разрешающий вход, 23 - выход окончания обмена. Группа входов и выходов устройства имеют обозначеия 24, 25 соответственно.. Устройство может работать в следующих режимах. 1.Ввод данных из центрального процессора в периферийное устройство (на чертеже не показано) . 2.Ввод данных из периферийного устройства в центральный процессор.: 3.Самостоятельная работа центрального процессора-и периферийного устройсгу. 4.Совместное решение задачи периферийным . устройством и центральным процессором. Описание режимов работы. 1.Центральный процессор II формирует команду, которая поступает в блок управления 4 и блок приоритета 3, последний на основании анализа команды, выдает сигнал, разрешающий блоку управления 4 произвести обмен. Получив сигнал, он вырабатывает комагщу, поступающую на коммутатор 6, синхронизатор 7. Коммутатор 6 отключает от регистра 8 и региС1ра 2 синхровизирующую последовательность блока сопряжения 5 и центрального процессора 11 соответственно. Данные из центрального процессора Г1 параллельным кодом переписьшаются в регистр 2. Блок управления 4 вырабатывает команду, которая поступает на коммутатор 6 и синхронизатор 7. По этой команде синхронизатор 7 вырабатывает синхронизирующую последовательность, а коммутатор 6 подключает эту последовательность к регистру 8 и .регистру 2, производит перезапись последовательным кодом из регистра 2 в регистр 8, из которого данные . параллельным кодом переписывают в блок сопряжения 5. 2.Из блока сопряжения 5 поступает команда на оЗмен в блок управления 4. На основании этого сигнала блок управления 4форми:рует команду, которйя поступает в блок приоритета .3. На основании этой команды блок приоритета 3 дает разрешение на обмен данными, или ставит в очередь на обслуживание. После получения разрешения на обмен блок управлевдя 4 вьфабатывает команду, поступающую на коммутатор 6 и синхронизатор 7, Коммутатор 6 отключает от регастра 8 и регистра 2 синхронизирующую последовательность блока сопряжения 5 и центрального процессора 11 соответстве1шо. Данные из блока сопряжения 5 поступают параллельньш кодом в регистр 8 по сигналу из блока управления 4. Этим же блоком вырабатывается команда, которая поступает на коммутатор 6 и синхронизатор 7. Па этой коман ср синхронизатор 7 вырабатывает синхронизирующую последовательность, а коммутатор 6 подключает эту последовательность. к регистру 8 и регистру 2, производит перезапись последовательным кодом из регистра 8 в регистр 2, из которого данные параллельным кодом переписьшаются в центральный процессор 11. Данные из регистра 8 по команде из блока управления 4 могут записьгеаться в блок памяти 9. В этом случае блок а1равления 4 вырабатьшает команду, которая поступает на синхронизатор 7, коммутатор 6 и коммутатор 1, последний на основании этой команды определяет зону блока памяти 9, в которую записьшаются данные периферийного устройств для последующего использования их центральным процессором 11. После окончания выдаш данных блок сопряжения 5 выдает команду окончания выдачи данных в блок управления который на основании этой команды прерывае работу синхронизатора 7, .коммутато1ра 6. Форм рует команду, которая выдается в .центральный процессор И, она извещает об окончании обме на и зоне памяти, в которой записаны данные 3.В этом режиме работают самостоятельно центральный процессор 11 и периферийное устройство. Центральный процессор 11 выдает команду блоку управления 4 и блоку приоритета 3 на самостоятельную работу периферийного устройства, в этой команде содержатся и адреса Зон блока памяти 9, с которыми будет работать периферийное устройство. По команде блок управления 4 формирует команду, которую посылает в блок сопряжения. 5, по этой же команде блок управления 4 посылает кома ду в синхронизатор 7, коммутатор 6 и комму татор 1. После прихода команды коммутатор 6 подключает синхронизирующ)то последовательность, вырабатываемую синхронизатором 7 к регистру 8, и коммутатору 1. .Данные из блока сопряжения 5 параллельным кодом переписьгоаются в регистр 8, откуда они последовательным кодом вводятся в коммутатор 1, для последующей записи в выделенную зону блока памяти 9. :Центральный процессор 11 ведет обмен данными с блоком памяти 9 через свой регист 2, куда данные загшсываются параллельным кодом, коммутатор 10, куда данные из регистра поступают в последовательном коде выделен ных зон блока памяти- 9. 4.В этом режиме центральный процессор 11 подключает оборудование устройства обмена данными и периферийного устройства для решения сложной задачи. Центральный процессор 11 вьщает команду в блок приоритета 3, который по этой команде прерывает работу периферийного устройства юрсз блок управления 4. ШнтральнЬгм процессором 11 вырабатывается команда для блока управления 4, содерх ащая информацию о ре66шаемой задаче и номера зон блока памяти 9, которые используются при этом. Дальнейшая работа проходит подобно режимам, 3,1. Таким образом, изобретение позволяет повысить быстродействие за счет совмещения работы обменивающихся данными абонентов. В связи с этим, увеличится число задач, решаемых системой, при уменьшении количества необходимых дая этого команд и сокращения времени. Все это позволяет гибко и быстро распределять ресурсы памяти и оборудования в зависимости от решаемой задачи обмена, подключать периферийное устройство к решению задач центрального процессора, дает непосредственный выход периферийному устройству к блоку памяти. Формула изобретения Устройство для обмена да1шыми, содержащее первый регистр, первый выход которого соединен с первым входом второго регистра, блок управления, командный вход которого является входом устройства, а первый запускающий выход соединен .с первым входом первого коммутатора, блок сопряжения и блок приоритета, причем первый выход первого коммутатора соединен со вторым входом второго регистра, первый выход которого соединен с первым входом первого регистра, группа входов и группа выходов первого регистра является соответственно группой входов и группой выходов устройства, а вход-выход блока сопряжения является входомвыходом устройства, отличающееся тем, что, с целью повышения быстродействия, оно содержит блок памяти, второй и третий коммутаторы и синхронизатор, причем первый запускающий выход блока управления через синхронизатор соединен со вторым входом первого коммутатора, второй выход которого соединен со вторым входом первого регистра и с третьим входом второго регастра, второй выход которого соединен с первым входом третьего коммутатора, трети: выход первого коммутатора соединен со вторым входом третьего коммутатора, вход-выход которого соединен с пер.вым выходом-входом блока памяти, второй вход-выход блока памяти соединен с выходомвходом второго коммутатора, первый, второй входы и выход которого соединены соответственно с первым адресным выходом блока управления, со вторым выходом и третьим входом первого регистра, группа входов и группа , выходов блока сопряжения соединены соответственно с группой выходов и грут1пой входов второго регистра, первый вход, первый и второй выходы блока сопряжения соединены соответственно со вторым запускающим выходом и запросным входом блока управления и с четвертым входом второго регистра, второй 7779996 адресный выход блока управления соединен С т ретьйм входим третьего коммутатора, вход устройства и запросный выход блока управлеггая через блок приоритета соед1гаены с разрешающим входом блока управления, а выход окончания обмена блока управления является выходом устройства. 5 кл кл ,-.,,,.. ..-.-.... .... Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР N 495659, . G 06 F 3/04, 1975. 2.Авторское свидетельство СССР № 490115, . G 06 F 3/04, 1975.

Авторы

Даты

1980-11-15—Публикация

1977-10-06—Подача