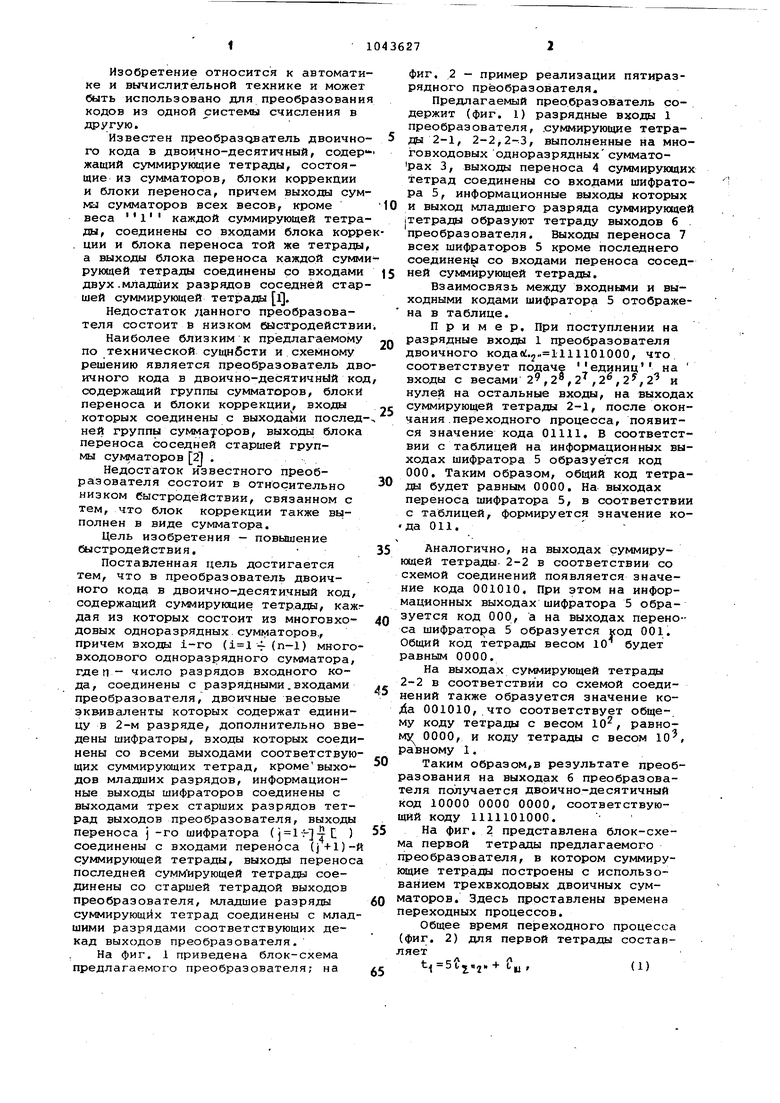

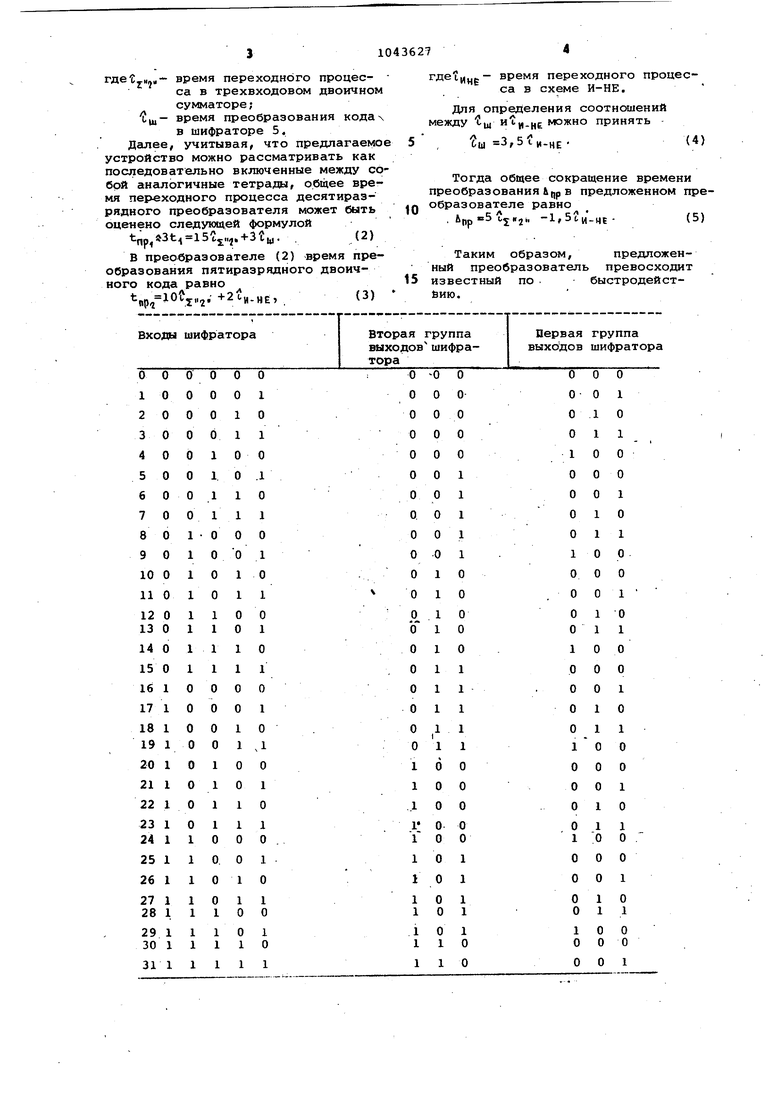

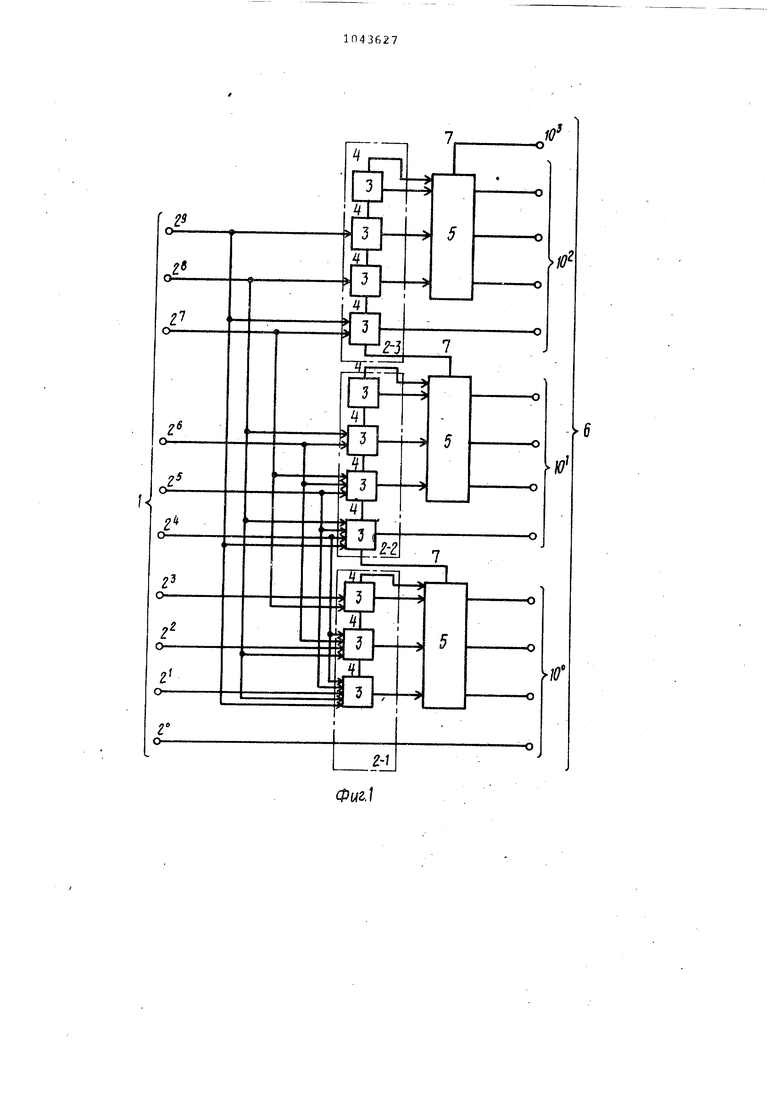

Изобретение относится к автоматике и вычислительной технике и может быть использовано для преобразовани кодов из одной истемы счисления в другую. Известен преобразователь двоичного кода в двоично-десятичный, содержащий суммирующие тетрады, состоящие из сумматоров, блоки коррекции и блоки переноса, причем выходы суммы сумматоров всех весов, кроме веса 1 каждой суммирующей тетрады, соединены со входами блока корре ции и блока переноса той же тетрады а выходы блока переноса каждой сумми рующей тетрады соединены со входами двух.младших разрядов соседней старшей суммирующей тетрады l. Недостаток данного преобразователя состоит в низком быстродействии Наиболее близким к предлагаемому по технической сущнбсти и схемному решению является преобразователь дво ичного кода в двоично-десятичнУй код содержащий группы сумматоров, блоки переноса и блоки коррекции, входы которых соединены с выходами последней группы сумматоров, выходы блока переноса соседней старшей групмы cyNwaTopoB 21 . Недостаток известного преобразователя состоит в относительно низком быстродействии, связанном с тем, что блок коррекции также выполнен в виде сумматора. Цель изобретения - повышение быстродействия.Поставленная цель достигается тем, что в преобразователь двоичного кода в двоично-десятичный код, содержащий суммирующие тетр.ады, кажг дан из которых состоит из многовходовых одноразрядных сумматоров., причем входы i-ro ( (п-1) многовходового одноразрядного сумматора, гдеп - число разрядов входного кода, соединены с разрядными.входами преобразователя, двоичные весовые эквиваленты которых содержат единицу в 2-м разряде, дополнительно введены шифраторы, входы которых соединены со всеми выходами соответствующих суммирующих тетрад, кромевыхо дов младших разрядов, информационные выходы шифраторов соединены с выходами трех старших разрядов тетрад выходов преобразователя, выходы переноса j -го шифратора ( ) соединены с входами переноса (+1)-й суммирующей тетрады, выходы переноса последней суммирующей тетрады соединены со старшей тетрадой выходов преобразователя, младшие разряды суммирующих тетрад соединены с младшими разрядами соответствующих декад выходов преобразователя. . На фиг. 1 приведена блок-схема предлагаемого преобразователя; на фиг, 2 - пример реализации пятиразрядного прёобразов1ателя. Предлагаемый преобразователь содержит (фиг. 1) разрядные входы 1 преобразователя, .суммирующие тетрады 2-1, 2-2,2-3, выполненные на многовходовых одноразрядныхсумматорах 3, выходы переноса 4 суммирующих тетрад соединены со входами шифратора 5, информационные выходы которых и выход младшего разряда суммирующей |Тетрады образуют тетраду выходов 6 преобразователя. Выходы переноса 7 всех шифраторов 5 кроме последнего соединены со входами переноса соседней суммирующей тетрады. Взаимосвязь между входными и выходными кодами шифратора 5 отображена в таблице. Пример. При поступлении на разрядные входы 1 преобразователя двоичного кодав.2,. 1111101000, что соответствует подаче единиц на входы с весами 29,2°,2,2,2,2 и нулей на остальные входы, на выходах суммирующей тетрады 2-1, после окончания .переходного процесса, появится значение кода 01111, В соответствии с таблицей на информационных выходах шифратора 5 образуется код 000. Таким образом, общий код тетрады будет равным 0000. На выходах переноса шифратора 5, в соответствии с таблицей, формируется значение кода 011. Аналогично, на выходах суммирующей тетрады- 2-2 в соответствии со схемой соединений появляется значение кода 001010, При этом на информационных выходах шифратора 5 образуется код 000, а на выходах переноса шифратора 5 образуется код 001. Общий код тетрады весом 10 будет равным 0000. На выходах суммирующей тетрады 2-2 в соответствии со схемой соединений также образуется значение ко4а 001010, что соответствует общему коду тетрады с весом 10, равному 0000, и коду тетрады с весом 10, равному 1, Таким образом,в результате преобразования на выходах б преобразователя получается двоично-десятичный код 10000 0000 0000, соответствующий коду 1111101000. На фиг, 2 представлена блок-схема первой тетрады предлагаемого преобразователя, в котором суммирующие тетрады построены с использованием трехвходовых двоичных сумматоров. Здесь проставлены времена переходных процессов. Общее время переходного процесса (фиг, 2) для первой тетрады составяет

время переходного процес- са в трехвходовом двоичном сумматоре; 2iu время преобразования кода

в шифраторе 5.

Далее, учитывая, что предлагаемое устройство можно рассматривать как последовательно включенные между собой аналогичные тетрады, общее время переходного процесса десятиразрядноцен t,

время переходного процесса в схеме И-НЕ.

Для определения соотношений между ц, и),.|, можно принять л 1 с

С-ы Jf- - и-нЕ

Тогда общее сокращение времени преобразованияi pв предложенном преобразователе равно

(5)

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU888104A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1501277A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1978 |

|

SU779999A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1988 |

|

SU1569993A1 |

| Преобразователь двоичных чисел в двоично-десятичные | 1987 |

|

SU1481897A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1283979A1 |

| Преобразователь двоичного кода в двоично-десятично-шестидесятиричный код | 1978 |

|

SU767749A1 |

| Преобразователь правильной двоично-десятичной дроби в двоичную дробь и целых двоичных чисел в двоично-десятичные | 1978 |

|

SU741260A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1205137A1 |

| Преобразователь правильной двоичной дроби в двоично-десятичную дробь и целых двоично-десятичных чисел в двоичные | 1978 |

|

SU734669A1 |

ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДВОИЧНО-ДЕСЯТИЧНЫЙ, содержащий суммирующие тетрады, каждая из которых состоит из многовходовых одноразрядных сумматоров, входы i-го ((n-l) многовходового одноразрядного сумматора, где п - число разрядов входного кода, соединены с разрядными входами преобразователя, двоичные весовые эквиваленты которых содержат единицу в 2-м разряде, отличающийся тем, что, с целью повышения быстродействия, в него введены шифраторы, входы которых соединены со всеми выходс1ми соответствующих суммирующих тетрад, кроме выходов младших разрядрв, информационные выходы шифраторов соединены с выходами трех старших разрядов тетрад выходов преобразователя, выходы переноса }-го шифратора (j 1тЗ ) соединены с входами переноса (j +1) суммирующей тетр ады, выходы переноса последней суммирующей тетрады соединены со старшей тетрадой выходов преобразователя,.младшие Л разряды суммирующих тетрад соединены с младшими разрядами соответствующих декад выходов преобразователя.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1973 |

|

SU476561A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Патент США №3614403, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

Авторы

Даты

1983-09-23—Публикация

1982-02-02—Подача