(54) ЯЧЕЙКА ПАМЯТИ ДЛЯ БУФЕРНбГО РЕГИСТРА

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти для буферного регистра | 1980 |

|

SU905860A1 |

| Ячейка памяти для буферногоРЕгиСТРА | 1979 |

|

SU799010A2 |

| Регистр сдвига | 1982 |

|

SU1084894A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1138834A1 |

| Асинхронный последовательный регистр | 1987 |

|

SU1481859A1 |

| Асинхронный регистр сдвига (его варианты) | 1982 |

|

SU1140173A1 |

| Асинхронный последовательный регистр на КМДП-транзисторах | 1987 |

|

SU1501168A1 |

| Асинхронный регистр сдвига | 1982 |

|

SU1119082A1 |

| Регистр | 1980 |

|

SU928418A1 |

| Асинхронный регистр сдвига | 1980 |

|

SU1015441A1 |

,. , .

Изобретение относится к вычислительной технике и может быть использовано для построения буферных запоминающих устройств.

По основному авт. св. N 799010 известна ячейка памяти для буферного регистра, содержащая основной и вспомогательный трехстабильнБте триггеры, каждый из которых вьшолнен на трех элементах И-ИЛИ-НЕ н десять входных шин, соединенньпс со входами этих триггеров, причем выходы всех трех элементов И-ИЛИ-НЕ основного триггера ячейки соединены со входами двух элементов И-ИЛИ-НЕ ее вспомогательного триггера,, выходы которых соединены со входами двух элемеягов И-ИЛИ НЕ основного триггера ячейки. В буферном регистре из таких ячеек обеспечивается не только сдвиг информации, но и ее параллельное считьгаание 1.

Однако, кроме ук анных двух операций, никакие другие операции в этом буферном регистре не осуц1;ествляются, что ограничивает его область применения.

Целью изобретения является расширение области применения ячейки памяти цля буферного регистра за счет обеспечения возможности осуществления одновременного реверсивного сдвига информации и параллельного ее считывания.

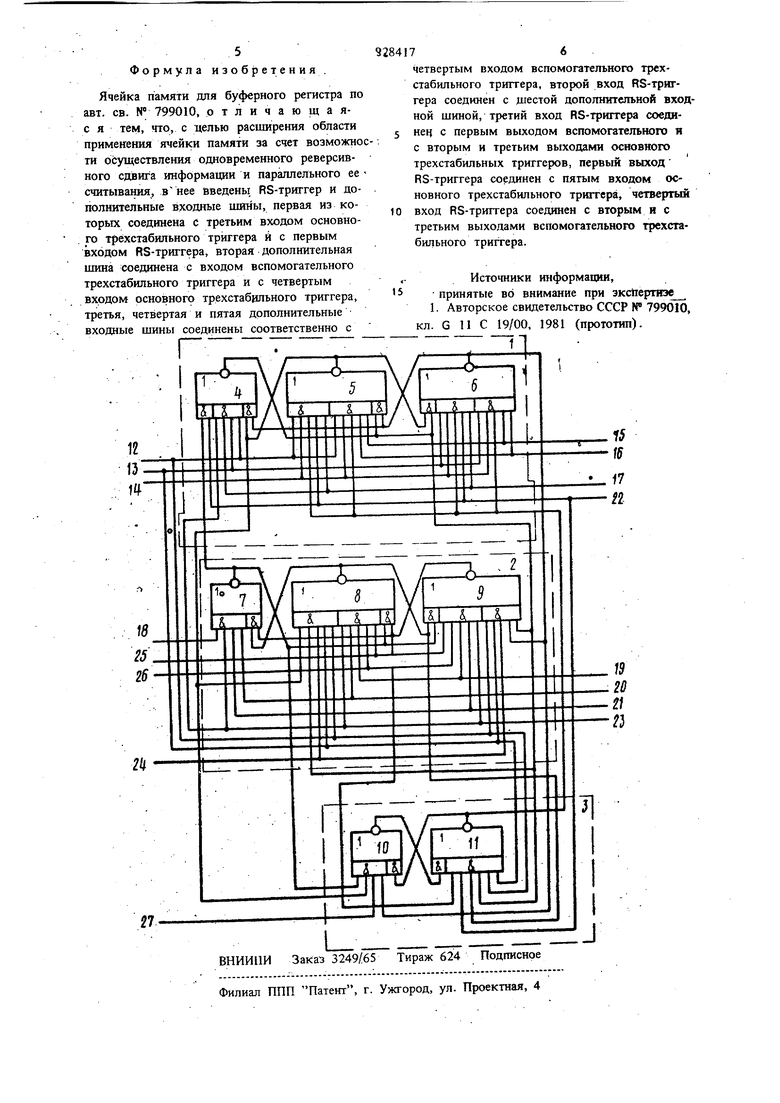

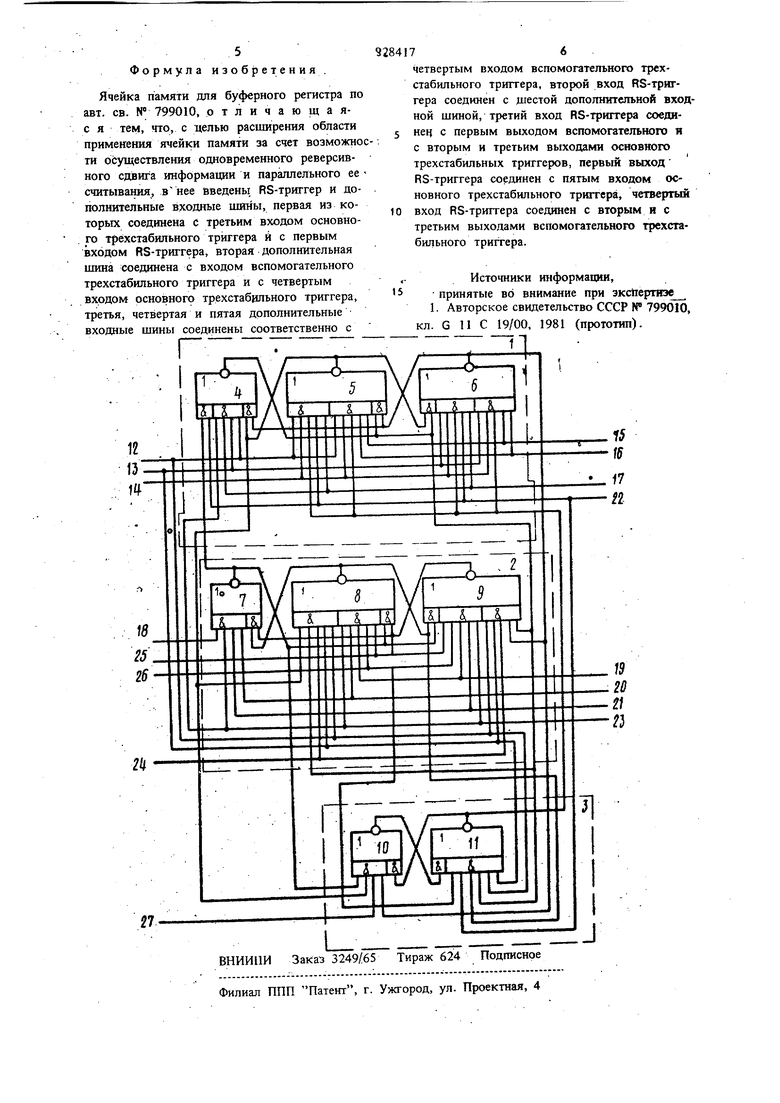

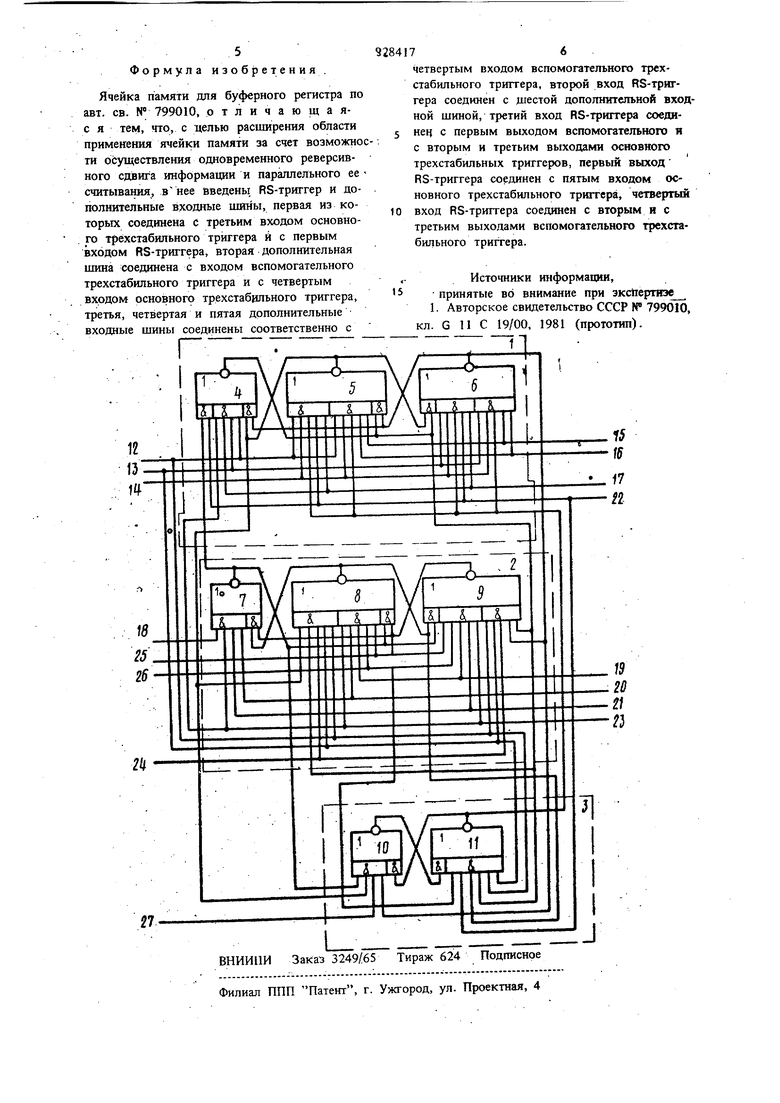

Поставленная цель достигается тем, что в ячейку памяти для буферного регистра введены RS-триггер и дополнительные вход ные шинь1, первая из которых соединена с третьим входом основного трехстабильного триггера и с первым входом RS-триггера, вторая дополнительная шина соединена с третьим входом вспомогательного трехстабильного триггера и с четвертым входом основного трехстабильного триггера, третья, ,четвертая и пятая дополнительные входные шины соединены соответственно с четвертым входом вспомогательного трехстабильного триггера; второй вход RS-триггера соединен с шестой дополнительной входной шиной, третий вход RS-триггера соединен с первым выходом вспомогательного и со вторым и третьим выходами основной) трехстабильно392841-7 .. 4.го триггеров, первый выход RS-трштера сое-памяти переводятся в coctOHirae 01. Уединен с пятым входом основного трехстабшть- ловием перехода дополнительного триггера ного триггера, четвертый вход RS-триггера соединен со вторым и с третьим выходами вспомогательного трехстабильного триггера. На чертеже изображена функЩюнальная схема предложенной ячейки памяти. Ячейка памяти содержит основной и вспо могательный трахстабильные триггеры 1 и 2 RS-триггер 3, элементы И-ИЛИ-НЕ 4-И, на которых выполнены соответственно триггеры 1, 2 и 3, основные входные шины 1221 и дополнительные входные шины 22-27. При построении буферного регистра шины 12, 13, 14, 18, 24, 25, 26 и 27 i-й ячей ки памяти соединяются .соответственно с выходами элементов 5, 6, 4, 7, 10, 8; 9 и И (|-)-й ячейки памяти, а шины 15, 16, 17, 19, 20, 21, 22, 23. i-й ячейки памяти с выходами элементов 5, 6, 4, 7, 8, 9,. 10, 11 (|+1)-й ячейки памяти. Ячейка памяти работает следующим образом. Основной и вспомогательный триггеры 1 2 имеют три устойчивых состояния (значения на выходах элементов И-ИЛИ-НЕ 4, 5 6 и 7, 8, 9 соответственно); 011 - информация в .триггера отсутствует, ПО - в триггере записана 1, 101 - в триггера записан О. Пока в триггере 3 сохраняется состояние 10 в основном и вспомогательном триггерах 1 и 2 ячейки памяти сдвиг информации происходит так же, как н в обычной в ячейке памяти буферного регистра, причем в основной триггер 11-й ячейки памяти информация принимается из основного тригге ра (i-1)-й ячейки памяти, а во вспомогательный триггер 2i-й ячейки информация, принимается из вспомогательного : триггера (i+l)-й ячейки памяти. Прн этом условием записи (стирания) информации в основном триггера li-й ячейки памяти является отсутствие (наличие) информации в основном триггера (i+l)-й ячейки памяти и наличие (отсутствие) информации в основном триггере (i-1)-и ячейки памяти. Для вспомогательного триггера 2 условия обратны приведенным. Сдвиг информации в основном и вспомогательном триггерах ячеек памяти буферного регистра приводит к тому, что основньте триггеры ячеек i, (i+1), ... оказываются за полнены Ю1формацией, а во всех вспомогательных триггерах этих ячеек памяти инфор лаияя отсутствует. По мере распространения такого состояния от п-й ячейки памяти бу ферного регистра к его первой ячейке памяти дополнительные триггеры этих ячеек 1-и ячейки памяти в состояние 01 является наличие такого состояния в дополнительном триггере (г+1)-й ячейки памяти, наличие информации в основном триггера i-й ячейки памяти и отсутствие информации в основном триггере (i-1)-й ячейки памяти и вспомогательном триггере 2 i-й ячейки. Состояние 01 триггера 3 i-й ячейки блокЛ рует запись информации в ее основной триггер 1 из основного триггера (i-1)-и ячейки. При этом, так же, как и в известном устройстве, в основном триггере г-й ячейки памяти оказывается записан i-й разряд сдвигаемого кода. После того, как в основных триггерах всех ячеек памяти буферного регистра записана информация, а в их дополнительных триггерах установится состояние 01 (при этом во всех вспомогательных триггерах информация отсутствует), происходит последовательная, начиная с первой ячейки памяти, перепись информации из основных триггеров ячеек памяти в их вспомогательные тригге Условием записи информации во вспомогательный триггер 2i-й ячейки из ее основного триггера 1 является отсутствие информации в основном триггере (i-1)-й ячейки и наличие состояние 01 -триггера (i-l)-й ячейки. После этого информация в основном триггере i-й ячейки памяти стирается. . . По мере заполнения информацией вспомогательных триггеров ячеек памяти буферного регистра их триггеры переходят в состояние 10. Условием перехода триггера (i-I)-й .ячейки памяти в состояние 10 является нали-. чие состояние 10 .триггера (i-1)-й ячейки памяти, наличие информации во вспомогательном триггере 2i-й ячейки и отсутствие информации в ее основном триггере 1. После того, как во вспомогательный триггер п-й ячейки памяти буферного регистра записана, информация из ее основного триггера, с выходов всех вспомогательных триггеров, так же, как и в известном устройстве, может быть параллельно считана информация. Как только триггер первой ячейки памяти буферного регистра окажется в состоянии 10, с выхода ее вспомогательного триггера может быть последовательно считана информация, ранее последовательно записанная в основные триггеры ячеек памяти буферного регистра. При-этом порядок следования разрядов поменяется на обратный, т.е. если код был записан в буферный регистр, начинал с п-разряда. то считывание произойдет, начиная с первого разряда. Одновременно с этим в буферный регистр может быть последовательно записан новый код.

Авторы

Даты

1982-05-15—Публикация

1980-06-24—Подача