. : Изобретение относится к вычиспвтельной технике и может быть использовано в вычислительных машинах для хранения информации. Известно запоминакшее устро{1ствО| содержащее блок переключения адрессю, накопитель, разделенный на группы, каждая из которых может независимо от Другой принимать; информацию об адресах 1J, Наиболее близким техническим реш6Ш ем к предлагаемому является запоминающее устройство, содержащее основные группы элементов И, накопитель, к адресным шсодам подключены выходы первого дешифрато(а, а к первым выходам - первые входы элементов И первой основной группы, управляющие входы первого деши атрра н регистра адреса под-, ключены к одним вз выходов блока управленвя, другие выходы которого соединены с вторыми вьаодами накопителя, третьи которого соединены (Г вторыми входами регистра адреса, первые входь1 которого являются входами запомннакшего устройства, выходы регистра адреса подключены к входам, первсго и второго ав011 фрато|} ю, выходы элементов И осно ври группы явжаются выходами запоминающего ycTpoecttta, и информшхионные шиныГ2 |. ИэвествЕое устройство позволяет формиp atb слова переменной длины только на выходе эапомвнакшего устройства, в то время как в ря{Ш устройств необходимо обеспечить возможность работы со словами aep iQBHoflдлины, поступающими на Ш{ф МШ1Вонные входы, что является недост т&ом, ограничива1сши(нд область, его всвот913О1аания. , Цель изобретения - расширение области применения за счет обеспечения вс можеюсти рабоНа {Устройства со словами перемешюй длвны. Поставленная . цель достигается тем, что В) ааломинакшиее устройство, содержащее основные группы элементов ,И, нако- питель, к адресным входам которого подключены выходы первого дешифратора, в

к первым выходам - первые входы элементов И первой основной группы, управляющие входы первого- дешифратора и регистра адреса подключены к одним из выходов блока управления, другие выходы которого соединены с вторыми выходами Нйкопитепя, третьи выходы которого соединены с вторыми входами регистра адреса, первые входы которого являются входами запоминающего устройства, выходы {зёгистра адреса подключены к входам первого и второго дешифраторов, выходы элементов И основной группы являются выходами запоминающего устройства и информационные шины введены дополнительные группы элементов И, коммутатор режима работы, входные и выходные буферные регистры, причем выходы элементов И дополнительньпс групп подключены к .инфорМ1ационным входам накопителя,

входы элементов И дополнительных групп, кроме первой, подключены через входные буферные регистры к одним вз информационных шнн, к другим информационным ши;нам подключены входы, элементов И первой дополнительной группы, входы выход (ных буферных регистров подключены к соответствующим входам элементов И первой основной группы, а выходы - к входам элементов И основной группы, кроме первой, одни ИЗ выходов коммутатора режима работы соединены с управляющими входами &пементов И основной группы и выходных буферных регистров, другие - с управля10й1йм:и входами элементов И дополнвтет ных групп и входных буферных . регистров,- входы коммутатора режима работы подключены к выходам второго деширатсра.

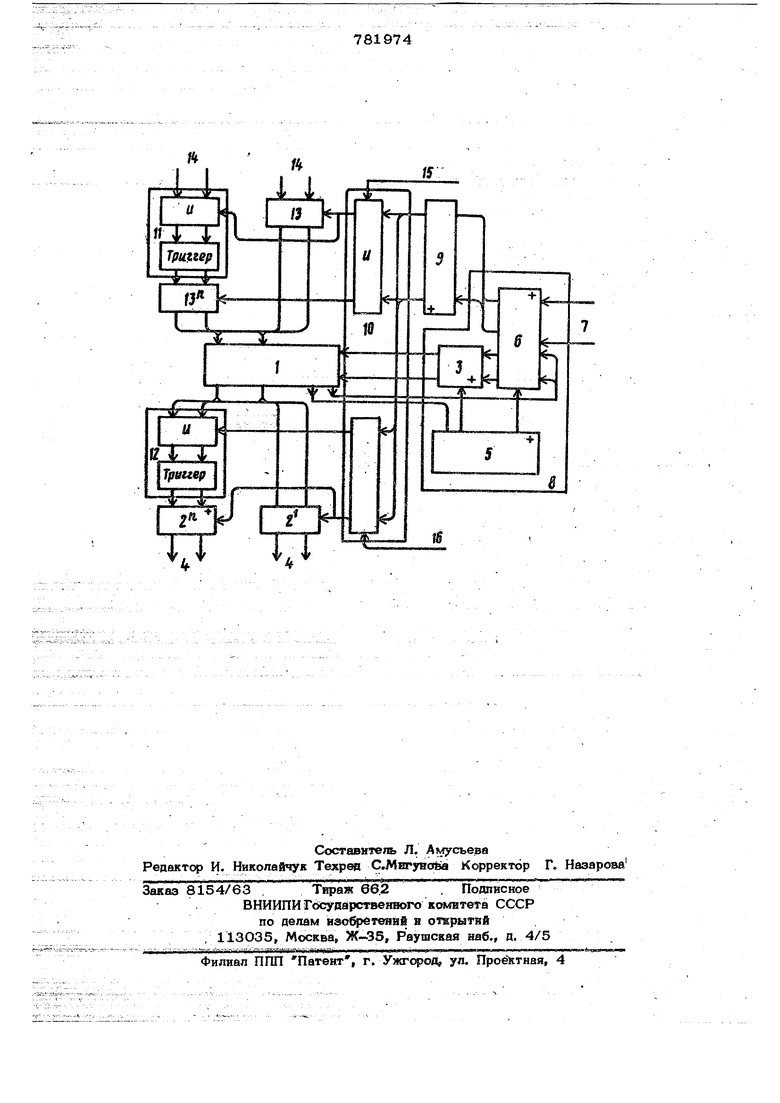

На чертеже представлена функаионапьная блбкг хема запоминающего устройства Запоминающее устройство Содержит накапитель 1, основную группу элементов И, первый дешифратор {дешифратор адреса) 3, выходы 4 элементов 2 -2и, являющиеся выходами устройства, блок 5 управления, регистр 6 адреса, входы 7 регистра адреса, являкяциеся входами устройства, формирователь 8 адреса, образованный блоком 5 управления, регистром 6 адреса и дешифратором 3, второй дешиф ратор (дешифратор коммутации) 9, коммутатор 1О режима работы, входные буферные регистры 11, выходные буферные рёгнстры 12, дополнительную группу элементов И, входы элементов 1313 И являются информационными шинами .14, шину 15 запись, шину 1б считывание.

Запоминающее устройство работает следующим образом.

Переа началом роботы устянавлквается режим работы запись путем подачи разрешающего сигнала на шину 15 или работы считывание путем подачи соответствухицего разрешающего сигнала на шину 16. Далее при считывании информации из накопителя 1 выбирается слово разрядносгтью равной разрядности одной группы в соотретствиии с адресом, поступающим с первых выходов регистра 6. Это слово записывается в любой выходной буферный регистр 12 с последующим считыванием его после формирования всего слова через соответствуюшие элементы 2 И основной группы или передается непосредственно через элементы 2 И основной группы в завершающем такте формированиязаданного формата слова. Последователъность подключения выходных буферных регистров 12 определяется кодом, формируемым на вторых выходах регистра 6 адреса. Код через дешифратор 9 и коммутатор 10 поступает в соответствующие цепи управления регистров 12 и элементов 2 И. Таким образом, разрядность выходного слова запоминающего устройства определяется суммой разрядов всех элементов И основной группы и формируется на выходах 4 запоминающего устройства.

При записи инфqpмaпии в накопитель 1 пр адресу, поступающему с первых выходов регистра 6, во входные -буферные регистры 11 записывается ( ff-l) групп входного слова, а информация первой группы, пройдя через элементы И дополнительной группы, записывается в накопитель 1 по адресу, сформированному на его адресных шинах. Затем информационное слово, записанное в {И -1) входных буферных регистрах И, последовательно по группам переписывается в накопитель 1 по аДресам, сформированным на первых выходах регистра 6 адреса. Последсжательность подключения регистров 11 определяется кодом, формируемым на вторых выходах регистра 6, которы1й через дешифратор 9 и коммутатор 10 поступает в соответствующие цепи управления регистров 11 и элементов 13 И. Таким образом, р зрядность входного слова запоминакшего устройства определяется суммой разрядов всех э;|ементов И дополнительных групп. Разряды записываются в накопитель 1 в виде fj тслов, разрядность каждого из которых определяется разрядностью элементов И одной дополнительной группы. В заломинаюпем устройстве обеспечит веется возможность работы со словами переменной длины, что достигается за счет преобразования К -р Гзряджя о входвого слова в ПК/л-разрядных слов (пколичество .групп во входной вля выходной цепи устройства) и запвсв юс в накопв тель по /Л. адресам, что обеспечивается благодаря введению входных буферных регистров и дополнительных групп алемантоа И, управление последовательностью подключения которых осуществляется коммутатором режима работы; формирования изЛ К / П Р зрядных слов, записаш1ых в накопитель, одного О -разрядного слова (р ) на выходе запоминакхпего устройства, что обеспечивается благодаря введению выходных буферных регистров и ряда новых связей, управление последовательностью подключения выходных буферных регистров и элементов И осйовной группы осуществляется коммутатором режима работй. Формула изобретевва Запоминакшее устройство, содержащее основные группы элементов И, .накопитель к адресным входам которого под лючевы выходы первого деигафратора, а к первым выходам - первые входы элементов И пер вой ОСЙОВНОЙ группы, управлякзяие ЁХОДЫ первого дешифратора и регистре адреса подключены к одним из выходов бпо&в ynравления, другие выходы которого соединены с вторыми выходами накопитепя, тре тьи выходы которого соединены с -вторым входами регистра адреса, первый входы которся о являются входами звпоминающег устройства, выходы регистра адреса подключены к входам первого и второго дещн4 аторов, выходы элементов И сх;новкой группы являются выходами запоминакацего устройства в информационные шины, о т личаюдцееся тем, что, с целью расширения области применения за счет обеспечения возможности работы устройства со словами переменной дпины, в него введены дополнительные группы эпементов И, кснймутатор режима работы, входные и выходные буферные регистры, причем выходы элементов И дополнительных групп подключены к информационным входам накопителя, входы элементов И дополнительных групя, первой, подключены через входные буферные регистры к одним из инфс мааионйых шин, к другим информационным шинам подключены входы эле ментов И первой дополнительной группы, входы выходных буферных регистров подключены к соответствующим входам эпементов И первой основной группы, а выходы к входам элемейтрв И основной группы, кроме первой, , вз выходов коммутатора, рвжтлй работы соединены с управляtcoiHMK входами элементов И основной группы в выходных буфергалх регистров, йиггне - с у1фвв11яю1цвмв вход.ами элемеч гов И допопввтельных, групп и ъходных буферный регистр«№, входы коммутатора режима работы подключены квыходам второго деши1 ат ра. Источнике-информации, принятые во внимавие при экспертизе 1.Патент Японии N 47-26218, кл, 97(7) С О2, кд. 97(7)1)0,15.07,72. 2.Авторское свидетельство -СССР № 49Ol78i кл. Q 11 С 11/ОО, 21.12.73 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1980 |

|

SU1080214A1 |

| Запоминающее устройство | 1978 |

|

SU743035A1 |

| Запоминающее устройство с коррекцией ошибок | 1987 |

|

SU1444898A1 |

| Ассоциативный параллельный процессор | 1980 |

|

SU955078A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Постоянное запоминающее устройство | 1978 |

|

SU805413A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1056274A1 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Оперативное запоминающее устройство | 1980 |

|

SU938317A1 |

| Устройство для сопряжения ЦВМ с аналоговыми объектами | 1983 |

|

SU1130856A1 |

Авторы

Даты

1980-11-23—Публикация

1978-12-07—Подача