(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОМАТИЧЕСКИМ ВОССТАНОВЛЕНИЕМ РАБОТОСПОСОБНОСТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автоматическим восстановлением работоспособности | 1976 |

|

SU591966A1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1981 |

|

SU972599A1 |

| Запоминающее устройство с автоматичес-КиМ ВОССТАНОВлЕНиЕМ РАбОТОСпОСОбНОСТи | 1979 |

|

SU834770A1 |

| Запоминающее устройство с самоконтролем | 1981 |

|

SU970476A1 |

| Система коммутации | 1986 |

|

SU1359783A1 |

| Трехканальная резервированная микропроцессорная система | 1985 |

|

SU1378287A1 |

| Запоминающее устройство | 1983 |

|

SU1203596A1 |

| САМООРГАНИЗУЮЩАЯСЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2011 |

|

RU2473113C1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Запоминающее устройство | 1978 |

|

SU781973A1 |

Изобретение относится к области запоминающих устройств. Известно запоминающее устройство с автоматическим восстановлением работоспособности по авт.св. 591966 которое содержит блок выборки адресов, основные одноразрядные блоки памяти, шины записи и шины управлени (по числу разрядов хранимой информации) , резервный одноразрядный блок памяти,элементы НЕ,три группы элементов И и элемент ИЛИ,причем адресные входы основных и резервного одноразрядного блоков памяти подключены к выходам блока выборки адресов соответствующие шины записи соединен со входами 3апись основных одноразрядных блоков памяти и с первыкм входами элементов И первой группы, вторые входы которых соединены с соответствующими шинами управления, со входами элементов НЕ и с первыми входами соответствующих элементов И второй группы, а выходы элементов И первой группы через элемент ИЛИ со входами Запись резервного одноразрядного блока памяти, вторые входы элементов И второй группы соединены с выходом резервного однора рядного блока памяти, первые входы элементов И третьей группы соединены с выходами основных одноразрядных блоков 11амяти, вторые входы - с выходами элементов НЕ, а выходы соответствующих элементов И второй и третьей групп соединены с соответствующими входами элементов ИЛИ. tlJ. Недостатком этого устройства является то, что при отказе двух и более основных блоков памяти происходит наложение информации в резервном блоке памяти, что приводит в конечном итоге к потере информации и снижению надежности устройства. изобретения является повышение надежности устройства за счет исключения возможности наложения информации при отказе двух и более основных блоков памяти. Поставленная цель достигается тем, что в запоминающее устройство с автоматическим восстановлением работоспособности по авт. св. I 591966 введен логический блок, входы которого являютря входами устройства, первый, второй и третий выходы логического блока подключены соответственно к первым входам элементов И первой группы, ко входам элементов НЕ и к первым входам элементов И второй

783857

группы, а четвертый выход логического блока является выходом устройства При этом логический блок целесоо.браэно выполнить в виде блока, содержащего элементы ИЛИ-НЕ, И-ИЛИ и И и триггеры, причем выходы элементов ИЛИ-НЕ подключены к первым входам элементов И, выходы которых соединены с пёр BJJNJH входами триггеров,входи элементов ИЛИ-НЕ и И-ИЛИ и вторые входы элементов И и триггеров подключены к соответствующим входам логического блока, выходы которого соединены с выходами триггеров и элемента И-ИЛИ.

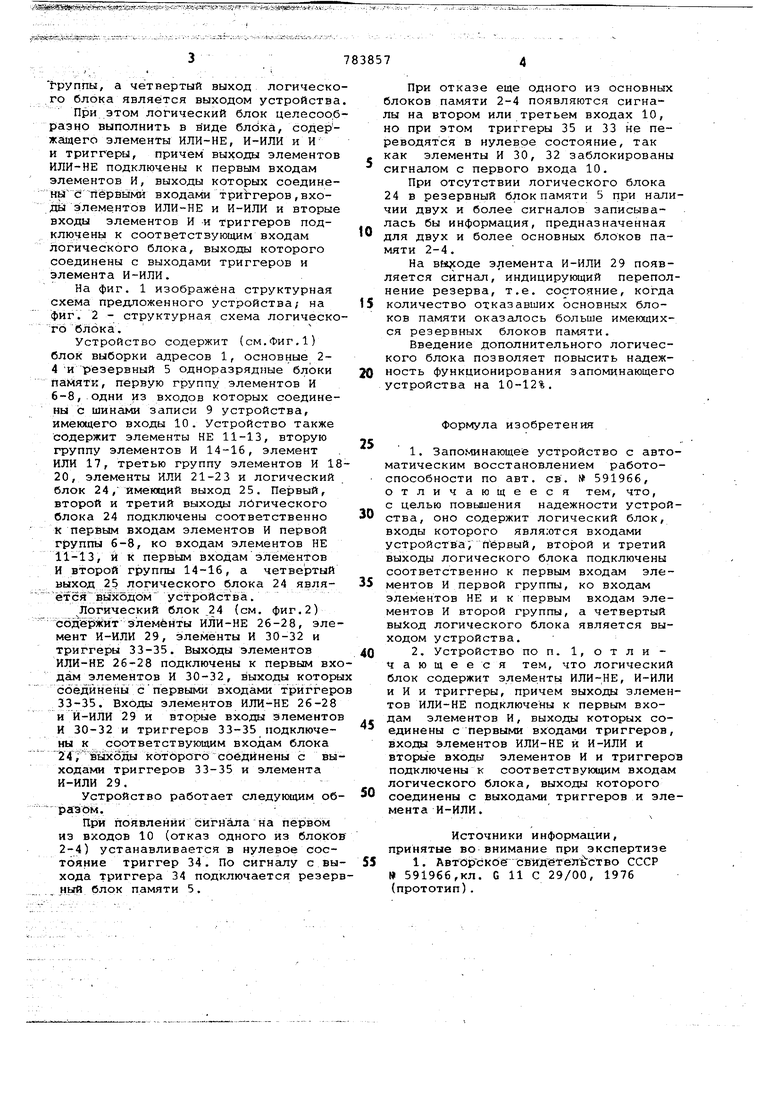

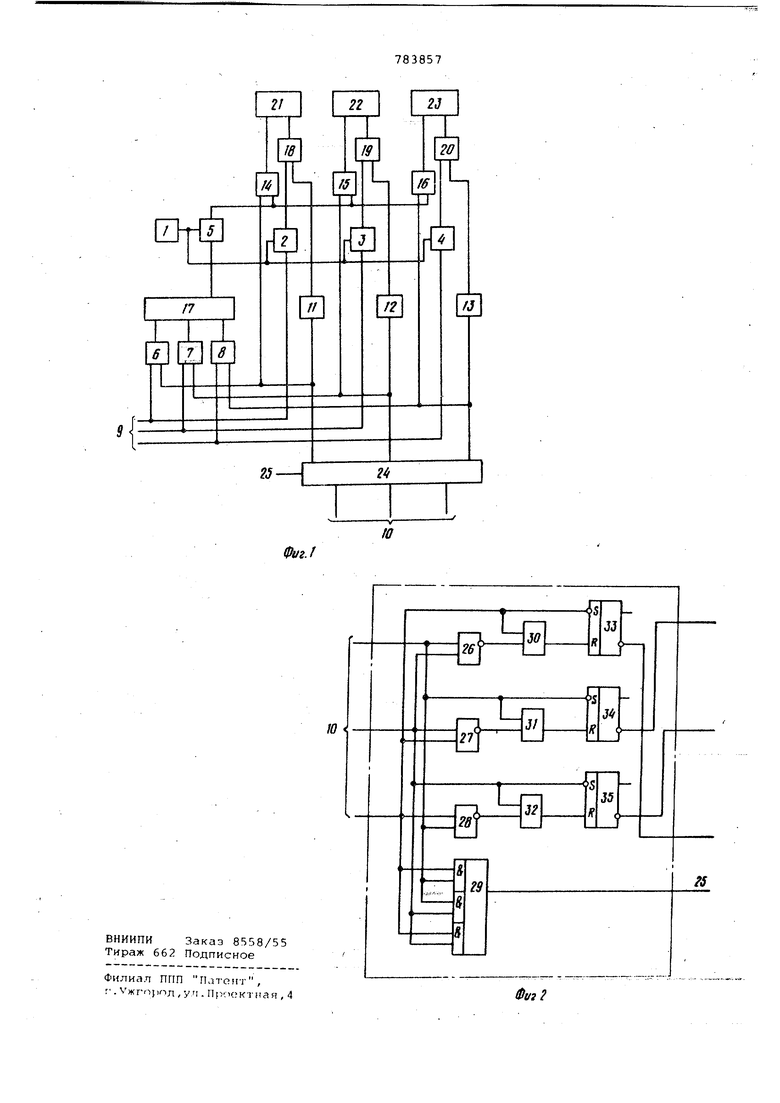

На фиг. 1 изображена структурная схема предложенного устройства/ на фиг. 2 - структурная схема логическотб блока.

Устройство содержит (см.Фиг.1) блок выборки адресов 1, основные 24 И резервный 5 одноразрядные блоки памяти, первую группу элементов И 6-8, одни из входов которых соединены с шинами записи 9 устройства, имеющего входы 10. Устройство также содержит элементы НЕ 11-13, вторую группу элементов И 14-16, элемент ИЛИ 17, третью группу элементов И 1820, элементы ИЛИ 21-23 и логический блок 24, имеющий выход 25. Первый, второй и третий выходы логического блока 24 подключены соответственно К первым входам элементов И первой группы 6-8, ко входам элементов НЕ 11-13, и к первым входам элементов И второй группы 14-16, а четвертый выход 25 логического е5лока 24 является выходом устройства.

Логический блок 24 (см. фиг. 2) СОДёрШт элементы ИЛИ-НЕ 26-28, элемент И-ИЛИ 29, 31лементы И 30-32 и триггеры 33-35. Выходы элементов ИЛИ-НЕ 26-28 подключены к первым входам элементов И 30-32, выходы которы соединены спервыми входами триггеро 33-35. Входы элементов ИЛИ-НЕ 26-28 и И-ИЛИ 29 и вторые входы элементов И 30-32 и триггеров 33-35 подключены к соответствующим входам блока 24 7 выходы которого соединены с выходами триггеров 33-35 и элемента И-ИЛИ 29.

Устройство работает следующим об раэом.

При появлений сигнала на первом из входов 10 (отказ одного иэ блоков 2-4) устанавливается в нулевое состояние триггер 34. По сигналу с выхода триггера 34 подключается резервнъгЛ блок памяти 5.

При отказе еще одного из основных блоков памяти 2-4 появляются сигналы на втором или третьем входах 10, но при этом триггеры 35 и 33 не переводятся в нулевое состояние, так как элементы И 30, 32 заблокированы сигналом с первого входа 10.

При отсутствии логического блока 24 в резервный блок памяти 5 при наличии двух и более сигналов записывалась бы информация, предназначенная для двух и более основных блоков памяти 2-4.

На вбрсоде элемента И-ИЛИ 29 появляется сигнал, индицирующий переполнение резерва, т.е. состояние, когда количество отказавших основных блоков памяти оказалось больше имеющихся резервных блоков памяти.

Введение дополнительного логического блока позволяет повысить надежность функционирования запоминающего устройства на 10-12%.

Формула изобретения

с целью повышения надежности устройства, оно содержит логический блок, входы которого явля;отся входами устройства; Пёрвый, второй и третий выходы логического блока подключены соответственно к первым входам элементов И первой группы, ко входам элементов НЕ и к первым входам элементов И второй группы, а четвертый выход логического блока является выходом устройства.

, .,

Источники информации, принятые во внимание при экспертизе

30

26

Авторы

Даты

1980-11-30—Публикация

1979-04-18—Подача