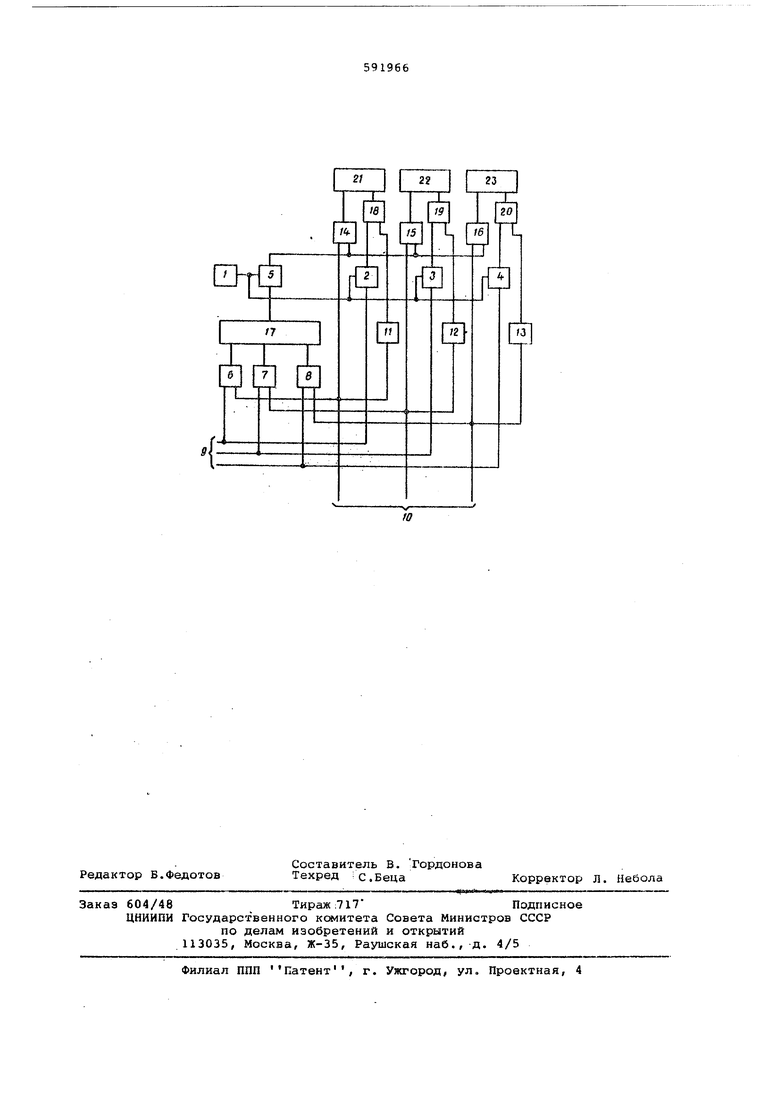

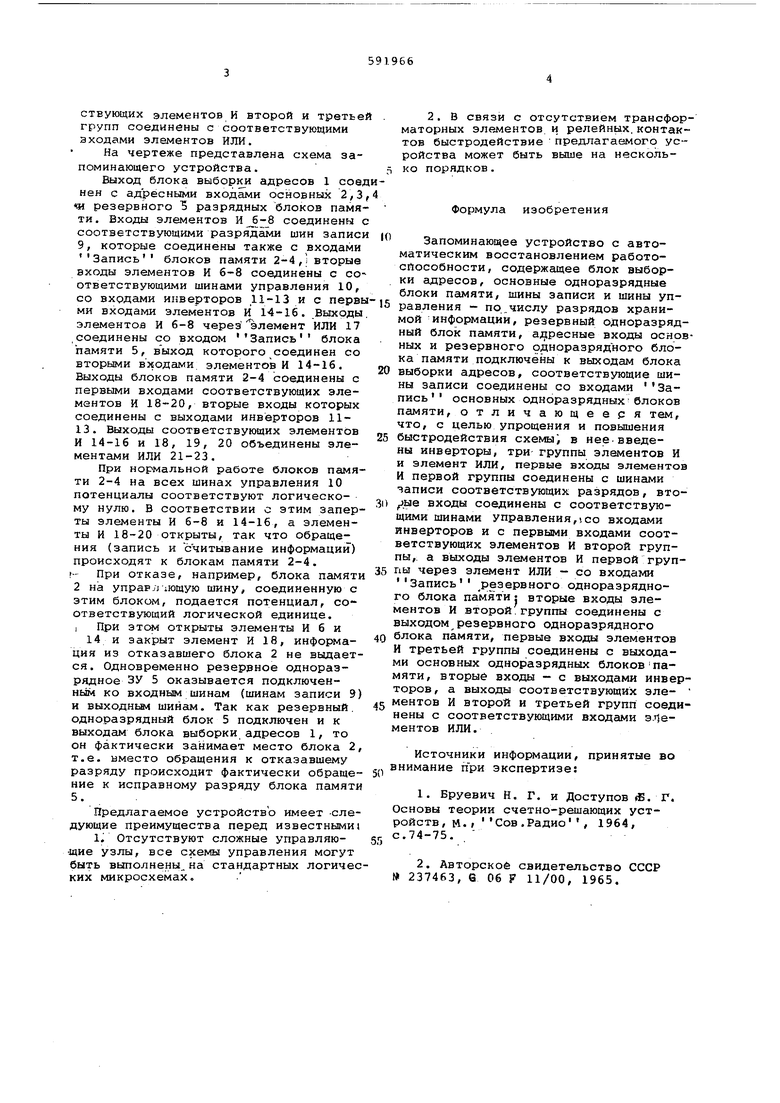

(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С АВТОМАТИЧЕСКИМ ВОССТАНОВЛЕНИЕМ РАБОТОСПОСОБНОСТИ ствующих элементов и второй и третье групп соединены с соответствующими входами элементов ИЛИ. На чертеже представлена схема запоминающего устройства. Выход блока выборки адресов 1 соед нен с адресными входами основных 2,3 1И резервного разрядных блоков памяти. Входы элементов соединены с соответствующими разрядами шин записи 9, которые соединены также с входами Запись блоков памяти 2-4,; вторые входы элементов И 6-8 соединены с со ответствующими шинаили управления 10, со входами инверторов 11-13 и с первы ми входами элементов И 14-16, Выходы элементов И 6-8 черезЭлемент ИЛИ 17 .соединены со входом Запись блока памяти 5, выход которого соединен со вторыми входами элементов И 14-16. Выходы блоков памяти 2-4 соединены с первыми входами соответствующих элементов И 18-20, вторые входы которых соединены с выходами инверторов 1113. Выходы соответствующих элементов И 14-16 и 18, 19, 20 объединены элементами ИЛИ 21-23. При нормальной работе блоков памяти 2-4 на всех шинах управления 10 потенциалы соответствуют логическому нулю. В соответствии с этим заперты элементы И 6-8 и 14-16, а элементы И 18-20 открыты, так что обращения (запись и считывание информации) происходят к блокам памяти 2-4. При отказе, например, блока памяти 2 на управляющую шину, соединенную с этим блоком, подается потенциал, соответствующий логической единице. I При этом открыты элементы И 6 и 14 и закрыт элемент И 18, информация из отказавшего блока 2 не выдается. Одновременно резеррное одноразрядное ЗУ 5 оказывается подключенHfcJM ко входным шинам (шинам записи 9) и выходнь м шинсм. Так как резервный. одноразрядный блок 5 подключен и к выходам блока выборки адресов 1, то он фактически занимает место блока 2, т.е. иместо обращения к отказавшему разряду происходит фактически обращение к исправному разряду блока памяти 5. Предлагаемое устройство имеет -следующие преимущества перед известными) 1. Отсутствуют сложные управляющие узлы, все схемы управления могут быть выполнены, на стандартных логичес ких микросхемах. 2. В связи с отсутствием трансформаторных элементов, и релейных, контактов быстродействие предлагаемого усройства может быть выше на несколько порядков. Формула изобретения Запоминающее устройство с автоматическим восстановлением работоспособности, содержащее блок выборки адресов, основные одноразрядные блоки памяти, шины записи и шины управления - по..числу разрядов хранимой информации, резервный одноразрядный блок памяти, а;(ресные входы основных и резервного одноразрядного блока памяти подключены к выходам блока выборки адресов, соответствующие шины записи соединены со входами Запись основных одноразрядныхблоков Пс1мяти, отличающееся тем, что, с целью упрощения и повышения быстродействия схемы в нее.введены инверторы, три группы элементов И и элемент ИЛИ, первые входы элементов И первой группы соединены с шинами записи соответствующих разрядов, вторые входы соединены с соответствующими шинами управления,со входами инверторов и с первыми входами соответствующих элементов И второй группы,, а выходы элементов И первой группы через элемент ИЛИ - со входами Запись резервного одноразрядного блока памяти вторые входы элементов И второй.группы соединены с выходом резервного одноразрядного блока памяти, первые входы элементов И третьей группы соединены с выходами основных одноразрядных блоковпамяти, вторые входы - с выходами инверторов, а выходы соответствующих элементов И второй и третьей групп соединены с соответствующими входами э.П& ментов ИЛИ. Источники информации, принятые во нимание при экспертизе: 1.Бруевич Н. Г. и Доступов «Б. Г. Основы теории счетно-решающих устройств, м. Сов .Радио , 1964, с.74-75. 2.Авторское свидетельство СССР I 237463, 6 06 F 11/00, 1965.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автоматичес-КиМ ВОССТАНОВлЕНиЕМ РАбОТОСпОСОбНОСТи | 1979 |

|

SU834770A1 |

| Запоминающее устройство с автоматическим восстановлением работоспособности | 1979 |

|

SU783857A2 |

| Запоминающее устройство с коррекцией однократных ошибок | 1982 |

|

SU1073799A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| Запоминающее устройство с блокировкой неисправных ячеек | 1981 |

|

SU972599A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ВЫСОКОЙ СТЕПЕНЬЮ ОТКАЗОУСТОЙЧИВОСТИ | 2005 |

|

RU2327236C2 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| Запоминающее устройство | 1983 |

|

SU1112412A1 |

| Логическое запоминающее устройство | 1977 |

|

SU674101A2 |

Авторы

Даты

1978-02-05—Публикация

1976-10-18—Подача