(54) УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ИЗБЫТОЧНЫХ КОДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема телесигналов | 1981 |

|

SU1003127A1 |

| Устройство для приема команд телеуправления | 1981 |

|

SU991473A1 |

| Устройство для приема телесигналов | 1976 |

|

SU610152A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство для приема команд телеуправления | 1977 |

|

SU643948A1 |

| Устройство для приема трехкратноповторенных команд телеуправления | 1977 |

|

SU720775A1 |

| Устройство цикловой синхронизации (его варианты) | 1980 |

|

SU951738A2 |

| Декодер сверточного кода | 1988 |

|

SU1520669A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство для приема дискретной информации, закодированной корректирующим кодом | 1988 |

|

SU1596464A1 |

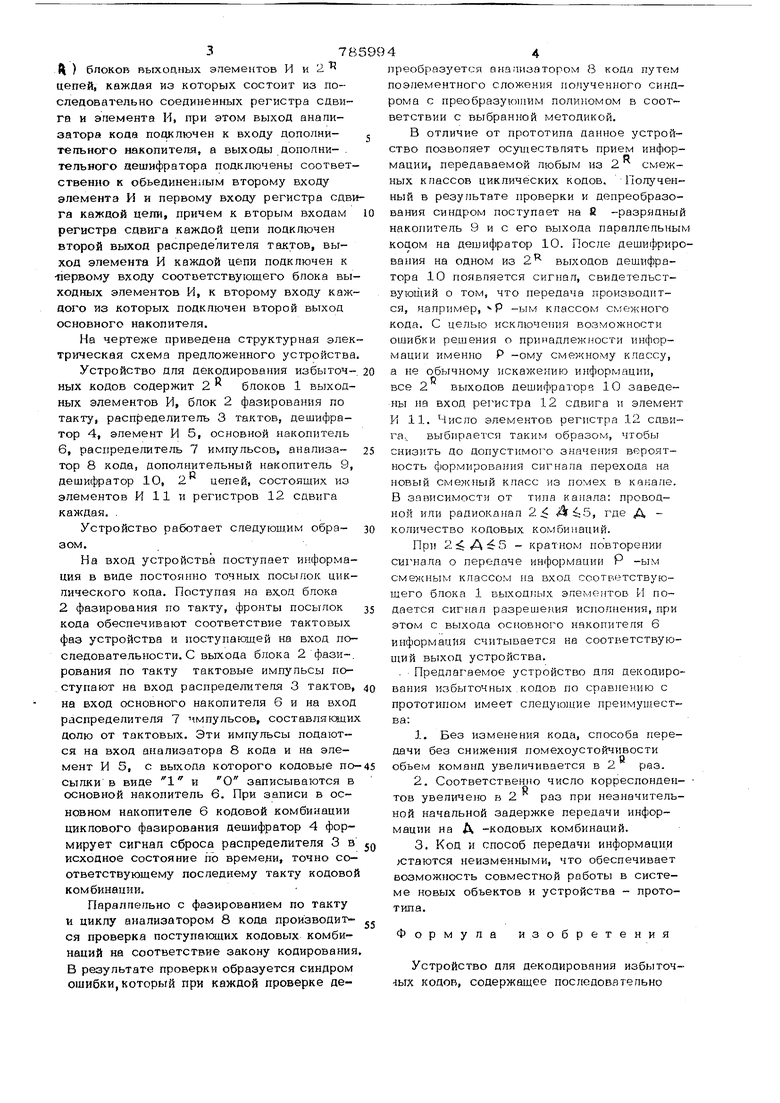

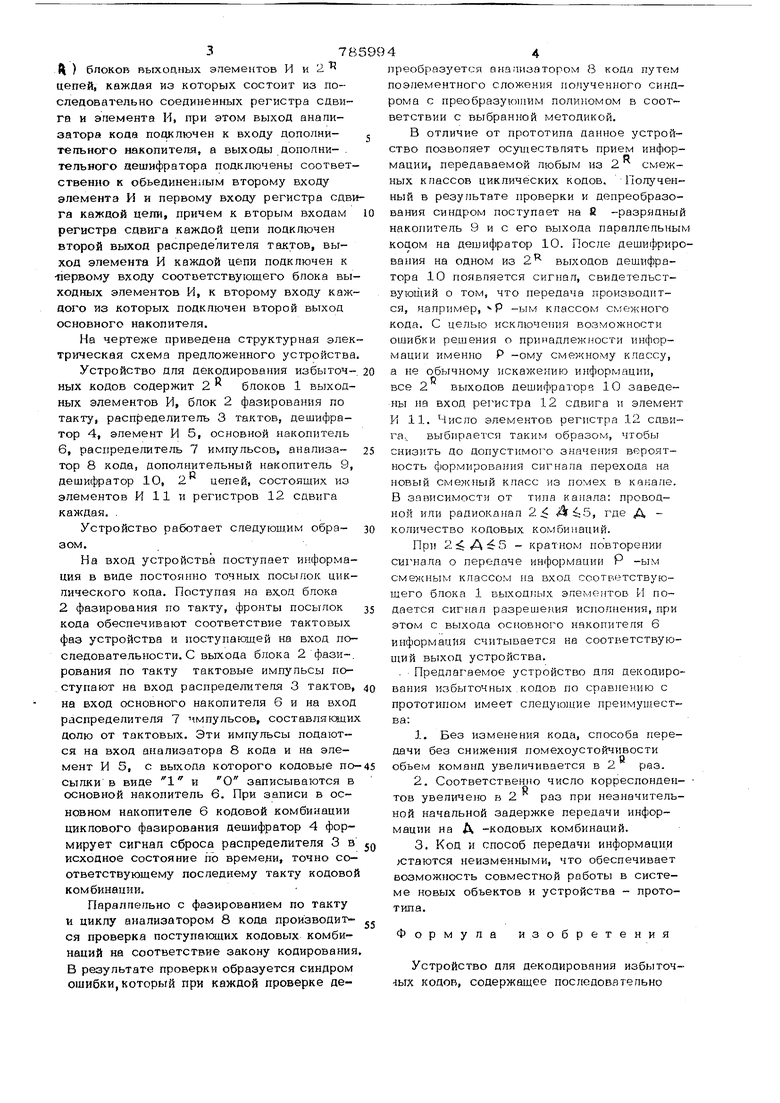

Изобретение относится к эпектросвязи и может использоваться для приема информации, передаваемой по каналам связи избыточными коаами Известно устройство для декодирования избыточных кодов, содержащее последовательно соединенные блок фазирования по такту, распределитель тактов и анализатор кода, а также последовательно соединенные распределитель импульсов, элемент И, основной накопитель и дешифрато выход которого подключен к второму входу, распределителя тактов, при этом второй выход блока фазирования по такту под ключен через распределитель импульсов к второму входу анализатора кода, к третьему входу которого подключен второй выход основного накопителя, к второму входу ко торого подключен первый выход блока фа1 зирования по такту, вход которого обьеди . иен с вторым входом элемента И l. Однако известное устройство имеет ограниченный объем принимаемой инфор мации и недостаточную точность декодирования. Пепь изобретения - повышение точности декодирования. ипя этого в устройство для декодирования избыточных кодов, содержащее последовательно соединенные бпок фазирования по такту, распределитель тактов и анализатор кода, а также последовательно соединенные распределитель импульсов, элемент И, основной накопитель и деши(})ратор, выход которого подключен к второму пходу распределителя тактов, при этом второй выход блока фазирования по такту подключен через распределитель импульсов к второму входу анализатора кода, к третьему входу которого подключен второй выход основного накопителя, к второму входу которого подключен первый выход блока фазирования по такту, вход которого объединен со вторым входом элемента И введены последовательно соединенные дополнительные накопитель и дешифратор, а также 2 (где , 2, ..., { ) блоков выходных эпементов И и цепей, каждая из которых состоит из последовательно соединенных регистра сдвига и эпемента И, при этом выход анализатора кода по 1ключен к входу дополнитегаьного накопителя, а выходы дополни- . тельного дешифратора подключены соответ ственно к объединенным второму входу эпемента И и первому входу регистра сдв га каждой uemi, причем к вторым входам регистра сдвига каждой цепи подключен второй выход распределителя тактов, выход эпемента И каждой цепи подключен к первому входу соответствующего блока вы ходных элементов И, к второму входу каж дого из которых подключен второй выход основного накопителя. На чертеже приведена структурная элек трическая схема предложенного устройства Устройство для декодирования избыточных кодов содержит 2 блоков 1 выходных элементов И, блок 2 фазирования по такту, распределитель 3 тактов, дешифратор 4, элемент И 5, основной накопитель 6, распределитель 7 импульсов, анализатор 8 кода, дополнительный накопитель 9, дешифратор 10, 2 цепей, состоящих из элементов И 11 и регистров 12 сдвига каждая. . Устройство работает следующим образом. На вход устройства поступает информация в виде постоянно точных посылок циклического кода. Поступая на вход блока 2 фазирования по такту, фронты посылок кода обеспечивают соответствие тактовых фаз устройства и поступающей на вход последовательности. С вьпсода блока 2 фази рования по такту тактовые импульсы по, ступают на вход распределителя 3 тактов, на вход основного накопителя 6 и на вход распределителя 7 импульсов, составляющи долю от тактовых. Эти импульсы подаются на вход анализатора 8 кода и на элемент И 5, с выхода которого кодовые по сылки в виде 1 и О записываются в основной накопитель 6. При записи в основном накопителе 6 кодовой комбинации циклового фазирования дешифратор 4 формирует сигнал сброса распределителя 3 в исходное состояние по времени, точно соответствующему последнему такту кодово комбинации. Паралпельно с фазированием по такту и циклу анализатором 8 кода производится проверка поступающих кодовых комбинаций на соответствие закону кодирования В результате проверки образуется синдром ошибки, который при каждой проверке депреобразуется анапнзатором 8 кода путем поэлементного сложения полученного синдрома с преобразующим поли} омом в соответствии с выбранной методикой. В отличие от прототипа данное устройство позволяет осуществлять прием информации, передаваемой любым из 2 смежных классов циклических кодов. Полученный в результате проверки и депреобразования синдром поступает на и -разрядный накопитель 9 и с его выхода параллельным кодом на дешифратор 10. После дещифрировапия на одном из 2 выходов дешифратора 10 появляется сигнал, свидетельствующий о том, что передача производится, например, p -Ь1М классом смежного кода. С целью исключения возможности ощибки решения о принадлежности информации именно Р -ому смежному классу, а не обычному искажению информации, все 2 выходов дешифратора 10 заведены на вход регистра 12 сдвига и элемент И 11. Число элементов регистра 12 сдвига,, выбирается таким образом, чтобы снизить до допустимого значения вероятность формирования сигна па перехода на новый смежный класс из помех в канапе. В зависимости от типа канала: проводной или радиоканал 2. , где Д количество кодовых комбинаций. При 2 А 5 - кратном повторении сигнала о передаче информации Р -ым смежным классом па вход соответствующего блока 1 выходных эпементов И подается сигнал разрешения исполнения, при этом с выхода основного накопителя 6 информация считывается на соответствующий выход устройства. . Предлагаемое устройство для декодирования избыточных .кодов по сравнению с прототипом имеет следующие преимущества:1.Без изменения кода, способа передачи без снижения помехоустойчивости объем команд увеличивается в 2 раз. 2.Соответственно число корреспонден- тов увеличе1ю в 2 раз при незначительной начальной задержке передачи информации на Д -кодовых комбинаций. 3.Код и способ передачи информаци.и стаются неизменными, что обеспечивает возможность совместной работы в системе новых объектов и устройства - прототипа. Формула изобретения Устройство для декодирования избыточ ых кодов, содержащее последоватепьно

соединенные бпок (шзированкя по такту распредепитель тактов и анализатор кода, а также последовательно соединенные распредепитель импупьсов, элемент И, основной накопитель и дешифратор, выход которого подключен к второму входу распределителя тактов, при этом второй выход блока фазирования по такту подключен через распределитель импульсов к второму входу анализатора кода, к третьему входу которого подключен второй выход основного накопителя, к второму входу которого подключен первый выход блока фазирования по такту, вход которого объединен с вторым входом элемента И, о т л к чающееся тем, что, с целью повышения точности декодирования, введены последовательно соединенные дополнительные накопитель и дешифратор, а также

2 (где ,2, ..

R ) блоков выходных элементов И и

цепей, каждая из

которых состоит из последовательно соединенных регистра сдвига и элемента И, при этом выход аиппизатора кода подключен к входу дополнительного накопителя, а выходы дополнительного дешифратора подключены соответственно к объединенным второму входу элемента И и первому входу регистра сдвига каждой цепи, причем к вторым входам регистра сдвига каждой цепи подключен второй выход распределителя тактов, выход элемента И каждой цепи подключен к первому входу соответствующего блока выходтиых элементов И, к второму входу каждого из которых подключен второй выход основного накопителя.

Источники информпиии. принятые во внимание при экспертизе

Авторы

Даты

1980-12-07—Публикация

1978-11-29—Подача