1

Изобретение относится к передаче данных и может быть использовано для обеспечения циклового фазирования синхронных систем связи.

По основному авт.св. № известно устройство цикловой синхронизации, содержащее объединенные по входу кодовый преобразователь, блок выделения тактовой частоты jg и регистр сдвига, выходы которого через соответствующий дешифратор подключены к первым входам первого и второго элементов И, к вторым входам которых, а также к первому 15 входу первого элемента НЕ подключен первый выход распределителя импульсов а выходы первого и второго элементов И подключены к первому и второму входам блока проверки чередования. 20 кодов, выход которого подключен к .первым входам первого элемента ИЛИ, первого и второго накопителей и второму входу первого элемента НЕТ,

выход которого подключен к вторым входам первого и второго накопителей, при-этом первый выход первого накопителя подключен к третьему входу второго накопителя, выход которого подключен к второму входу.кодового преобразователя и третьему входу первого накопителя, второй выход которого подключен к третьему входу кодового преобразователя и второму входу первого элемента ИЛИ, а выход первбго элемента ИЛИ подключен к первому входу распределителя импульсов, к второму входу которого подключен выход блока выделения тактовой частоты, а остальные выходы распределителя импульсов подключены к соответствующим входам кодового преобразователя.

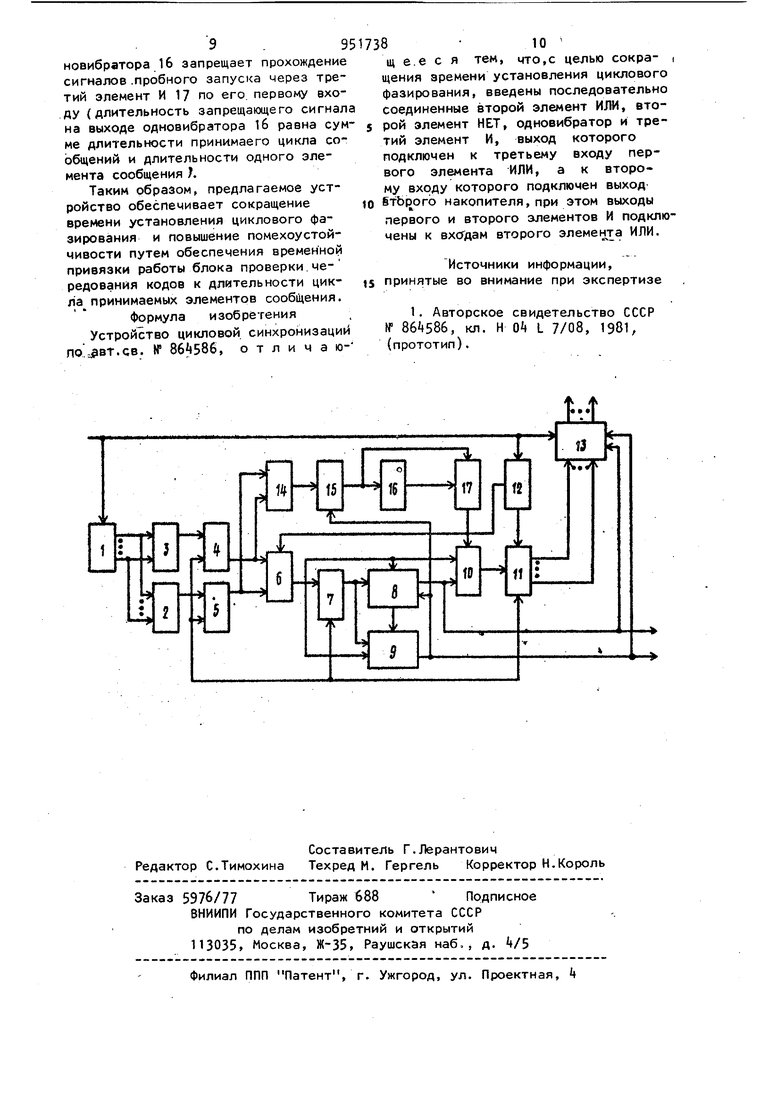

Кроме того, возможен второй вариант устройства цикловой синхронизации, в котором дополнительный выход блока выделения тактовой частоты подключен к третьему входу блока пр верки чередования кодов 1. Однако известное устройство обла дает большим временем установления циклового фазирования. Цель изобретения - уменьшение времени установления циклового фази рования. Для достижения этой цели в устро ство цикловой синхрон|;1зации введены последовательно соединенные второй элемент ИЛИ, второй элемент НЕТ, одновибратор и третий элемент И, вы ход которого подключен к третьему входу первого элемента ИЛИ, а к второму входу третьего элемента И подключен выход второго элемента НЕ к второму входу которого подключен выход второго накопителя, при этом выходы первого и второго элементов И подключены ко входам второго элемента ИЛИ. На чертеже приведена структурная электрическая схема предлагаемого устройства. Устройство цикловой синхронизации содержит регистр 1 сдвига, первый и второй дешифраторы 2,3, первы и второй элементы И ,5, блок 6 про верки чередования кодов, первый эле мент НЕТ 7 первый накопитель 8, второй накопитель 9, первый элемент ИЛИ 10, распределитель 11 импульсов, блок 12 выделения так товой частоты, кодовый преобразователь 13, второй элемент ИЛИ И, вто рой элемент НЕТ 15, одновибратор 1б третий элемент И 17Устройство работает следующим образ Групповой цифровой сигнал (непре рывная последовательность бинарных единиц и нулей) поступает на вход регистра 1 сдвига, кодового преоб1разователя 13 и блока 12 выделения |тактовой частоты, который осущест(вляет выделение из группового сигна ;па тактовой частоты (частоты телеграфирования), которая необходима для работы распределителя 11 импульсов. Поступающий групповой сигнал продвигается по разрядам регистра 1 сдвига. С выхода регистра 1 сдвига комбинации принимаемых элементов сообщения (посылок в параллельном коде поступают на входы первого и второго дешифратора 2 и 3. Каждая комбинация сигналов на входах перво го и второго дешифраторов 2 и 3, ан логичная одной из фазирующих комбинаций, вызывает формирование сигнала на выходе соответствующего дешифратора 2 или 3. Если устройство находится в состоянии синхронизма, то отдельные сигналы с выходов первого и второго дешифраторов 2 и 3 совпадают по времени с тактовым сигналом распределителя П импульсов, поступающим один раз за цикл с первого выхода распределителя 11 импульсов. При этом на выходах соответствующих элементов И 4,5 попеременно (через один цикл) появляются сигналы, соответствующие по времени моменту опознавания фазирующих комбинаций. Блок 6 проверки чередования кодов осуществляет проверку чередования поступающих на его входы сигналов. Сигнал на выходе блока 6 проверки чередования кодов появляется только при чередовании сигналов на его входах . При наличии сигналов в каждом цикле на выходе блока 6 проверки чередования кодов сигналы на выходе перво,го элемента НЕТ 7 отсутствуют. Поэтому первый накопитель 8 не заряжен и сигнал на его втором выходе отсутствует. Так как в случае синфазной работы сигналы на выходе блока б проверки чередования кодов присутствуют в каждом цикле, а сигналы на выходе первого элемента НЕТ 7 отсутствуют, то второй накопитель 9 заряжен и на его выходе имеется сигнал синфазной работы. Этот сигнал разрешает декодирование информации, поступающей на первый вход кодового преобразователя 13, и ее выдачу на выход устройства, разрешает работу первого накопителя 8 { переводит его в режим готовности к поддержанию синфазной работы, т.е. разрешает заряд пераого накопителя 8; и запрещает прохождение сигналов с выхода второго элемента ИЛИ 14 на вход одновибратора 16. Кроме того, сигналы с выхода блока 6 проверки чередования кодов поступают на первый вход первого элемента ИЛИ 10. Выходные сигналы с выхода первого элемента ИЛИ 10 осуществляют запуск распределителя 11 импульсов, который управляет записью и декодированием информации в кодовом преобразователе 13- Таким образом, запуск распределителя 11 импульсов осуществляется один раз в начале цикла,принимаемого на вход группового сигнала в одни и те же моменты времени, т.е. устройство находится в состоянии синфазной работы. Ложные синхрогруппы, аналогичные фазирующим комбинациям и выделенные первым и вторым дешифраторами из группового сигнала, вследствие случайного сочетания нулей и единиц информации в групповом сигнале не совпадают, естественно, по времени с сигналом, формируемым на первом выходе распределителя 11 импульсов один раз за цикл, а, следовательно, не проходят через первые и вторые элементы И и 5 не участвуют в про цессе работы блока 6 проверки чередования кодов. При кратковременных искажениях фазирующих комбинаций (например, из-за воздействия помех или при сбо синхронизации в системах более высо кого порядка ) сигнал на выходе блок 6 проверки чередования кодов времен но отсутствует. В этом случае первы элемент НЕТ 7 оказывается открытым и сигнал с первого выхода распределителя П импульсов, формируемый в конце цикла работы распределителя 11 импульсов Ч фактически при его остановке J, поступает через первый элемент НЕТ 7 на вторые входы первого и второго накопителей 8,9. Этот сигнал сбрасывает счетную схему вто го накопителя 9 в нулевое состояние но уровень сигнала синфазной работы на его выходе остается, так как его сброс осуществляется лишь при посту лении сигнала сброса с первого выхода первого накопителя 8. Так как на выходе второго накопителя 9 присутствует сигнал, разрешающий работу первого накопителя 8, то сигнал с выхода первого элемента НЕТ 7 проходит через первый накопитель В на автозапуск, одновременно зарядная первый накопитель-8 на одну единицу. Этот сигнал, проходя через первый элемент ИЛИ 10, запускает распределитель 11 импульсов на следующий цикл работы. Таким образом, запуск распределителя 11 импульсов происходит в тот же момент времени, что и при наличии фазирующих комбинаций, поэтому нарушение синхронизма не происходит и устройство продолжает работу уже в состоянии поддержания синхронизма. Кроме того,.сигнал автозапуска со второго выхода первого накопителя поступает на третий вход кодового преобразователя 13. В зависимости от режима работы кодового преобразователя 13 сигнал автозапуска либо не оказывает влияния на его работу, либо (в режиме повышенной достоверности) запрещает декодирование и выдачу информации на выход устройства. В случае отсутствия фазирующих комбинаций в следующих циклах работа продолжается аналогичным образом до тех пор, пока первый накопитель 8.не окажется заряженным. Появление до этого момента времени сигнала на выходе блока 6 проверки чередования кодов (т.е. обнаружение фазирующих комбинаций на прежних временных позицияхJ приводит к сбросу ранее заряженного первого накопителя 8 в нулевое состояние. Этот же сигнал через первый элемент ИЛИ 10 проходит- на первый вход распределителя 11 импульса, запуская его. Таким образом, устройство вновь переходит в режим синфазной работы. При отсутствии сигналов на выходе блока 6 проверки чередования кодов в б подряд следующих циклах где (fj - коэффициент накопления первого накопителя 8), т.е. при зарЯ де первого накопителя 8 на его . первом выходе формируется импульс сброса, который переводит второй накопитель 9 в нулевое состояние. В результате на выходе второго накопителя 9 появляется нулевой уровень, а, следовательно, кодовый преобразователь 13 прекращает декодирование информации и ее выдачу на выход устройства. Кроме того, отсутствие сигнала на выходе второго накопителя 9 выводит первый накопитель 8 из состояния готовности к поддержанию . синфазной работы и разрешает прохождение сигналов через второй элемент НЕТ 15. В режиме поиска синхронизма работа устройства осуществляется следующим образом. Вследствие остановки распределителя 11 импульсов на его первом выходе присутствует уровень напряжения, разрешающий прохождение сигналов через первый и второй элементы И f и 5. Прэтому при выделении дешифратором 2 или 3 из. состава принимаемых элемент тов сообщения одной из комбинаций, аналогичных фазирующим, на выходе второго элемента ИЛИ И формируется сигнал,.поступающий на первый вход второго элемента НЕТ 15. Вследствие отсутствия сигнала синфазной работы на выходе второго накопителя у второ элемент НЕТ 15 оказывается открытым и сигнал с его выхода поступает на второй вход третьего элемента И 17 и на вход одновибратора 16. ствие того, что одновибратор 1б, формирующий при его запуске сигнал напряжения логического нули, срабатывает с некоторой задержкой, сигнал с выхода второго элемента НЕТ 15 проходит через третий элемент И 17 на его выход и поступает на третий вход первого элемента ИЛИ 10. Вследствие этого происходит пробный запус распределителя 11 импульсов. Одновременно с этим сигнал об обнаружении комбинации,, аналогичной фазирующей, с выхода одного из элементов И k или 5 поступает на соответствующий вход блока 6 проверки чередовани кодов. Пробный запуск распределителя 11 импульсов приводит к тому, что сигнал на его первом выходе сменяется нулевым уровнем, который сохраняется до момента времени, соответствующего остановке распределителя 11 импульсов(т.е. в течение времени одного цикла работы ). Поэтому элементы И 4 и 5 оказываются закры тыми и .выделение дешифраторами 2 и 3 комбинаций, аналогичных фазирующим и расположенных.ВО времени внутри цикла работы кодового преобразователя ТЗ, не оказывает влияния на работу блока 6 проверки чередования кодов. Пусть, например, пробный запуск распределителя 11 импульсов производится сигналом с выхода второго дешифратора 3 ( через второй элемент И 5, второй элемент ИЛИ 1, второй эле мент НЕТ 15, третий элемент И 17, первый элемент ИЛИ 10). Спустя время равное длительности цикла принимаемы элемеутов сообщения, распределитель 11 импульсов возращается в исходное состояние и на его первом выходе появляется уровень напряжения, разреша ющий прохождение сигналов через первый и второй элементы И А,5. Если в этот момент времени комбинация, аналогичная фазирующей, выделяется 9 8 первым дешифратором 2 f т.е. происходит смена фазирующей комбинации срабатывает блок 6 проверки чередования кодов, вследствие чего на его выходе формируется сигнал, запускающий распределитель 11 импульсов для работы на прежних временных позициях и записывающий единицу во второй накопитель 9. В следующем цикле работы в момент формирования разрешающего сигнала на выходе распределителя 11 импульсов формируется сигнал на выходе второго дешифратора 3 { т.е. вновь происходит смена фазирующей комбинации), вновь срабатывает блок 6 проверки чередования кодов, вследствие чего запуск распределителя 11 импульсов осуществляется на прежних временных позициях, а во второй накопитель 9 записывается вторая единица. Далее процесс работы продолжается аналогично описанному вплоть до появления.сигнала на выходе второго накопителя, свидетельствующего о вхождении аппаратуры в синхронимз и закрывающего второй элемент НЕТ 15. В случае, если пробный запуск распределителя 11 импульсов осуществляется случайной комбинацией, аналогичной фазирующей, то в следующем цикле принимаемых элементов сообщения на прежних временных позициях располагается другая комбинация, отличная от фазирующей, вследствие чего вторичный пробный запуск распределителя 11 импульсов С через второй элемент ИЛИ I, второй элемент НЕТ 15, третий элемент И 17, первый элемент ИЛИ 10) на прежних временных позициях не происходит и устройство продолжает находиться в состоянии поиска комбинации, аналогичной фазирующей. В случае многократного циклического повторения одной и той же ин- формации в нескольких циклах подряд и при первоначальном пробном запуске распределителя от случайной комбинации, аналогичной фавирующей , эта же комбинация вновь выделяется тем же дешифратором ( например, вторым ) на прежних временных позициях спустя цикл работы распределителя 11 импульсов. Однако втбричный пробный запуск распределителя 11 импульсов на прежних времен-, ных позициях в этом случае н проис ходит, так как сигнал с выхода од9новибратора 16 запрещает прохождение сигналов .пробного запуска через третий элемент И 17 по его первому входу (длительность запрещающего сигнал на выходе одновибратора 1б равна сум Мб длительности принимаего цикла сообщений и длительности одного элемента сообщения J. Таким образом предлагаемое устройство обеспечивает сокращение времени установления циклового фазирования и повышение помехоустойчивости путем обеспечения временной привязки работы блока проверки.чередования кодов к длительности цикла принимаемых элементов сообщения. Формула изобретения Устройство цикловой синхронизации .св. № , отличаю8щ е.е с я тем, что,с целью сокра- i щения времени установления циклового фазирования, введены последовательно соединенные второй элемент ИЛИ, второй элемент НЕТ, одновибратор и третий элемент И, выход которого подключен к третьему входу первого элемента ИЛИ, а к второму входу которого подключен выход itbf)orb накопителя, при этом выходы первого и второго элементов И подключены к входам второго элеме1нта ИЛИ. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № , кл. Н Ok L 7/08, 1981, (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство цикловой синхронизации | 1980 |

|

SU1341727A2 |

| Устройство цикловой синхронизации | 1979 |

|

SU1259504A1 |

| Устройство цикловой синхронизации (его варианты) | 1979 |

|

SU864586A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| Устройство синхронизации | 1980 |

|

SU982205A1 |

| Устройство цикловой синхронизации | 1980 |

|

SU924892A1 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство синхронизации | 1983 |

|

SU1095435A1 |

| Приемник синхросигнала | 1981 |

|

SU1092745A1 |

М

Авторы

Даты

1982-08-15—Публикация

1980-11-12—Подача