синхронизации подключены к первому выходу блока контроля по четности, второй выход которого соединен с четвертым входом блока управления, пятый вход которого подключен к управляющему выходу формирователя управляющих сигнсшов, одни из адресных входов накопителя первого уровня соединены с выходами младших разрядов регистра гщреса, а другие адресные входы подключены к выходам элементов И первой группы, первые входы которых соединены с выходами старших разрядов регистра адреса и первыми входами регистров адреса группы, выходы которых подключены к вторым входам элементов И первой группы, вторые входы регистров адреса группы являются.другими адресными входами устройства, а третьи и четвертые входы соединены с другими выходами блока анализа обращений к памяти, первый и второй управляющие входы которого подключены соответственно к второму выходу блока управления и к второму выходу второго блока синхронизации, а третий управляющий вход является третьим входом записи устройства, четвертым входом записи и входами блокировки которого являются входы регистра меток неисправных страниц памяти, управляющий вход формирователя управляющих сигналов является установочным входом устройства, управляющими входами и выходом которого являются соответственно входы с шестого по девятый и шестой выход блока управления.

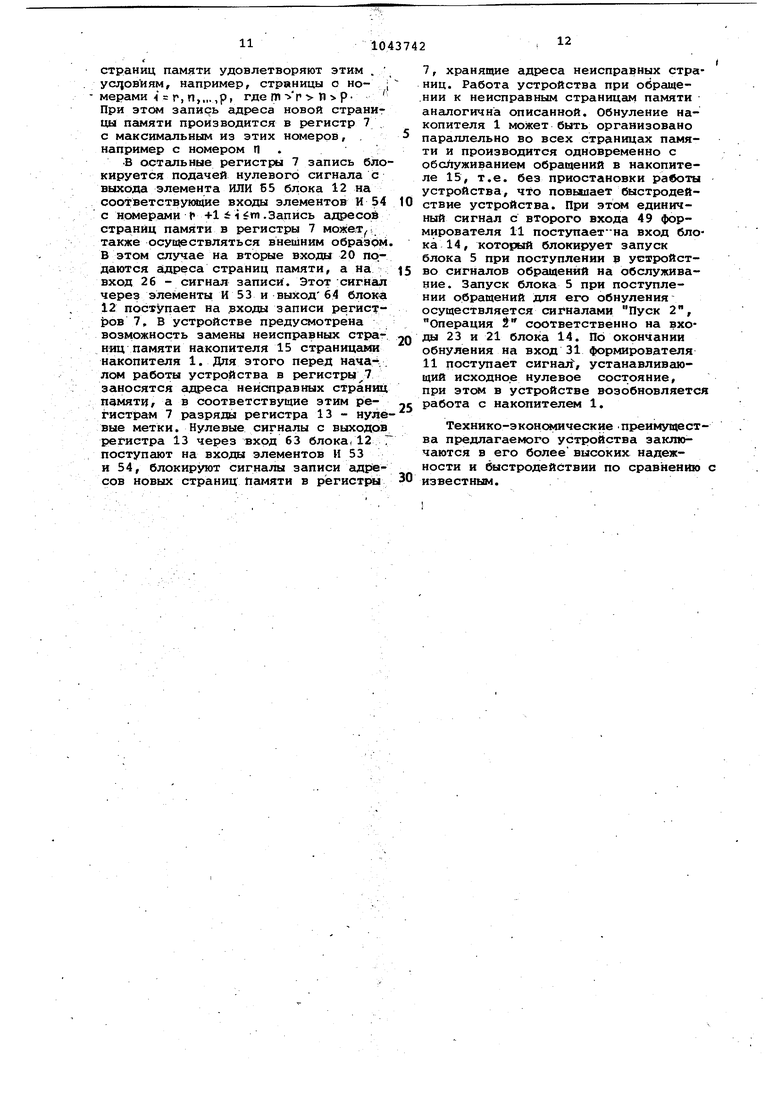

2. Устройство ПОП.1, отличающееся тем, что блок анализа обращений к памяти содержит счетчики сигналов, группы элементов И со второй по пятую, группы элементов ИЛИ, группу элементов НЕ, элементы И-НЕ, элемент ИЛИ и элемент НЕ, причем первые входы элементов И четвертой и пятой групп и вторые входы элементов И пятор группы являются одними из входов блока, другими входами которого являются вход элемента ИЛИ и первые входы элементов И третьей группы, первые входы элементов И втор9й группы и вторые входы элементов и третьей группы объединены и являются первым управляющим входом блока, вторым и третьим управляющими входами которого являются соответственно объединенные третьи входы элементов И пятой группы и объединенные вторые входы элементов И четвертой группы, выход элемента ИЛИ является управляющим выходом блока и подключен к входу элемента И-НЕ, выход которого соединен с вторыми входами элементов И второй группы, выход каждого из которых подключен К входу вычитания соответствующего счетчика сигналов, BXOJEI сложения которого соединен с выходом соответствующего из элементов И третьей группы, а выход - с входами соответствующих элемента ИЛИ первой группы и элемента И-НЕ группы, выход которого подключен к третьему входу соответствующего элемента И третьей группы, четвертый вход каждого из элементов И пятой группы соединен с выходом соответствующего элемента НЕ группы, вход которого подключен к выходу соответствующего элемента ИЛИ первой .группы и третьему входу соответствующего элемента И второй группы, выход первого из элемен-тов ИЛИ первой группы соединен с пятыми входами элементов И пятой группы, кроме первого, выход каждого М -го (гдеИ - число элементов ИЛИ в первой группе) последующего из элементов ИЛИ первой группы, 1{роме последнего, подключен к(и +4)-му входу П +.1}го элемента И пятой -группы, первые входы элементов И четвертой и пятой групп соответственно объединены, а выходы подключены соответственно к первому и к второму входам элементов ИЛИ второй группы, выходы которых соединены с входами установки в 1 соответствуквдих счетчиков сигналов, выходы последних из элементов И четвертой и пятой групп и выходы элементов ИЛИ второй группы являйтся выходами блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления обращением к общей памяти | 1987 |

|

SU1495804A1 |

| Запоминающее устройство | 1984 |

|

SU1243033A1 |

| Устройство для контроля памяти | 1979 |

|

SU809395A1 |

| Буферное запоминающее устройство | 1985 |

|

SU1261010A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2024969C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| Устройство адресации оперативной памяти | 1985 |

|

SU1262497A1 |

| Устройство адресации оперативной памяти | 1987 |

|

SU1417003A1 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

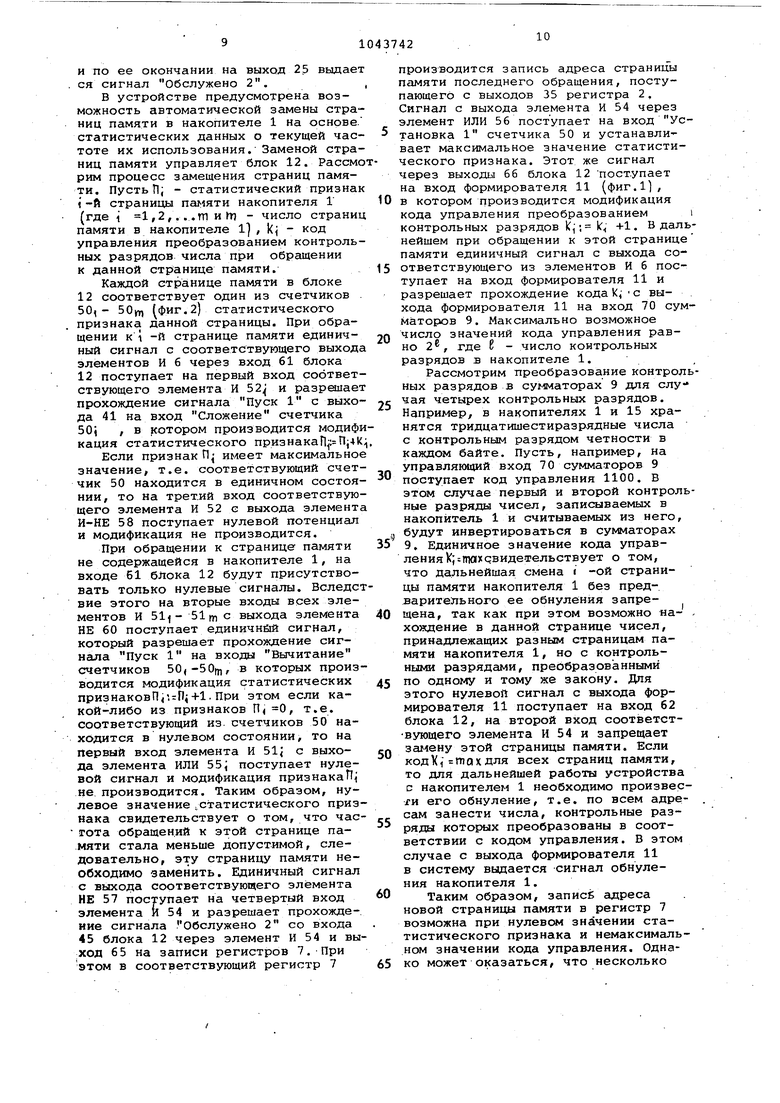

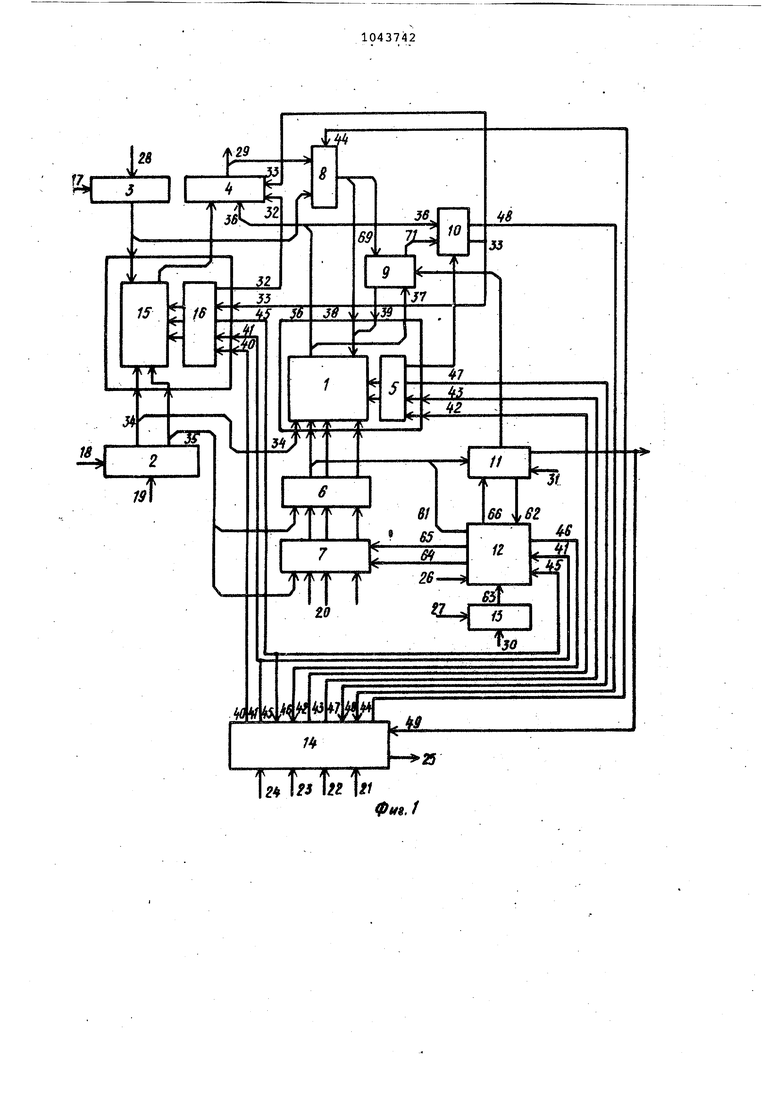

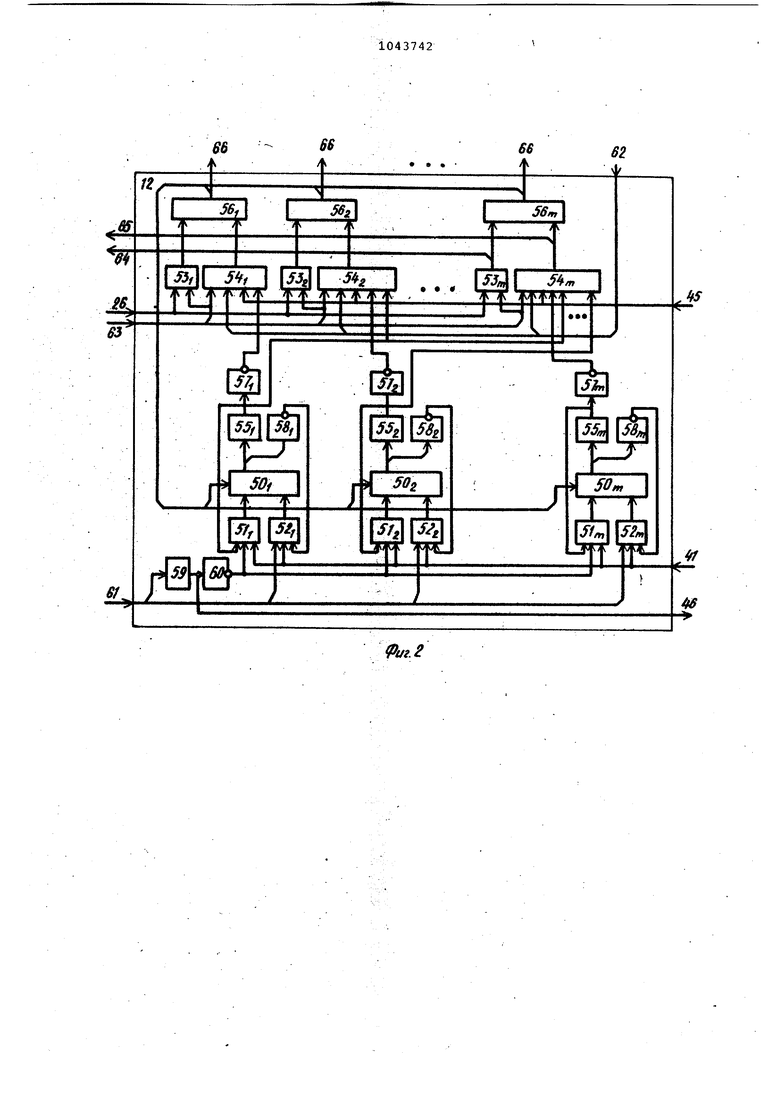

(.ДВУХУРОВНЕВОЕ ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее накопители первого и второго уровней, входы синхронизации КОТОЕЯЛХ подклю- чены к выходам первого и второго блоков синхрониза о(ии соответственно, регистр адреса, блок анализа обращений к памяти, группу регистров адреса, блок управления и первую группу элементов И, причем числовые входы и выходы йакопителя второго уровня соединены соответственно с выходами первого регистра числа и с одними из входов второго регистра числа, а адресные входы - с выходами регистра адреса, первый выход первого блока синхронизации подключен к первому . управляющему входу второго регистра числа, а второй выход, первый и второй входы соответственно соединены с первьм входом, о nepBwi и с вторым выходами блока управления, входы и управляющий вход первого регистра числа, управляющий вход и входы регистра адреса и выходы второго регистра числа являются соответственно информационными входами, первым и вторым входами записи, одними из адресных входов и информационными выходами устройства, отличающееся тем, что, с целью повышения надежности путем дублирования . страниц памяти в накопителях первого и второго уровней и повыиения быстродействия устройства, в него введены группы сумматоров по модулю два, ком мутатор , формирователь управляющих | сигналов, регистр меток неисправных страниц и блок контроля по. четности, . причем одни из входов коммутатора соединены соответственно-с выходами первого и второго регистров числа, числовые выходы подключены к числовым входам накопителя первого уровня, а выходы контрольных разрядов - к первым входам сумматоров по модулю два первой группы, выходы которых соединены с входами контрольных разрядов накопителя первого уровня, выходы сумматоров по модулю два второй группы подключены к одним из .входов блока контроля по четности, а первые входы - к выходам контрольных разрядов накопителя первого уровня, вторые(Л входы сумматорбв по модулю два групп соединены с одними из выходов формирователя управляющих си гнал о в, другие выходы которого и выходы регистра меток неисправных страниц подключены соответственно к одним из входов бло; ка внвлиза обращений к памяти,другие входы Которого соединены соответственно с выходами элементов И пер вой группы и одними из входов фор:о 1 мирователя управляющих сигналов, другие входы которого подключены к одним из выходов блока анализа обращений к памяти, первый управю ляющий выход которого подкл.ючен к второму входу блока управления, тре . тий и четрертый выходы и третий вход которого соединены соответственно с входами и с первым выходом первого блока синхронизации, а пятый выход подключен к другому входу кок утатора, другие входы блока контроля по четности соединены соответственно с вторым выходом первого блока синхронизации и с числовыми выходами накопителя первого уровня и другими входами второго регистра .числа, второй управляющий вход которого и третий вход второго блока

1

Изобретение относится к вычислительной технике и может быть использовано при построении оперативных запоминающих устройств вычислительных машин.

Известно двухуровневое оперативное запоминающее устройство, содержащее блоки памяти первого и второго уровня, блок дескрипторных регистров

описывающих соотнсиления между наборами ячеек (страниц) памяти первого и второго уровней, блок управления замещением страниц памяти первого уровня l .

Недостатками этого устройства являются низкие быстродействие и надежность. Наиболее близким по технической сущности к изобретению является двух уровневое оперативное запоминающее устройство, содержащее блоки памяти первого и второго уровня, регистр адреса, входной и выходной регистры числа, блок дескрипторны: регистров адресов страниц памяти,.блок схем совпа дения адресов страниц памяти,блок заме щения страниц памяти, блок управления устройством, числовые входы блока памяти второго уровня подключены к выходам входного регистра чис ла, числовые выходы - к первым входам выходного регистра числа, адресные входы - к выходам регистра адреса, первый управляющий выход - к пер вому входу записи выходного регистра чис;га, второй управлякидий выход, первый и второй управлягадие входы соответственно - к первому входу, первому и второму выходам блока управления устройством, числовые входы и вход записи входного регистра числа, числовой выход выходного регистра числа, адресные входы и -вход записи регистра адреса подключены к соответствующим входам и выходам устройства 21 . Недостатками известного устройства являются низкая надёжность вследствие того, что для коррекции ошибок в словах не используются возможности связанные с дублированием страниц па мяти в блоках памяти первого и второ го уровня, и снижение быстродействия из-за необходимости прерывания вычислительного процесса на время пере дачи страницы памяти в блок памяти первого уровня, так как при обраще-г НИИ к слову, не имеющемуся в блоке памяти первого уровня, производится перезапись всей страницы памяти, в которую входит данное слово, из блока памяти второго уровня в блок памяти первого уровня в соответствии с алгоритмом, расбчитанным на ситуаг цию, когда перезапись страниц происходит сравнительио редко. Целью изобретения является повыиение надежности устройства за счет дублирования страниц памяти в накопителях первого и второго уровней и повышеиие быстродействия устройства Поставленная цель достигается тем что в двухуровневое оперативное запоминающее устройство, содержащее накопители первого и второго уровней, входы синхронизации которых под ключены к выходам первого и второго блоков синхронизации соответственно, регистр адреса, блок анализа обргицений к памяти, группу регистров адреса, блок управления и первую rpyrtny элементов И, причем числовые входы и выходы накопителя второго уровня соединены соответственно с выходами первого регистра числа и с одними из вхЗДов второго регистра числа, а адресные входы - с выходями регистре адреса, первый выход первого блока синхронизации подключен к первому управляющему входу второго регистра числа, а второй выхой, первый и второй входы соответственно соединены с первым входом, с первым и с вторым выходами блока управления, входы и управляющий вход первого регистра числа, управляюший вход и входы регистра адреса и выходы второго регистра числа являются соответственно информационными входами, первым и вто- рым входами записи, одними из адресных входов и информационными выходами устройства, введены группы сумматоров по модулю два, коммутатор,.формирователь управляющих сигналов, регистр неисправных страниц и блок контроля по четности, причем одни из входов коммутатора соединены соответственно с выходами первого и второго регистров числа, числовые выходы подключены к числовым входам накопителя первого уровня, а выходы контрольных разрядов - к первым входам сумматоров по модулю два первой группы, выходы KoTopfcJx соединены со входами контрольных разрядов накопителя первого уровня, выходы сумматоров по модулю два второй группы подключены к одним из входов блока контроля по четности, а первые входа - к выходам контрольных разрядов накопителя первого уровня, вторые входы сумматоров по модулю два групп соединены с одними из выходов формирователя управляющих сигналов, другие выходы .которого и выходы-регистра; меток неисправных страниц подключены соответственно к одним из входов блока анализа обращений к памяти, другие входы которого соединены соответственно с выходами элементов И первой группы и одними из входов формирователя управляю- . щих сигналов, другие входы которого подключены к одним из выходов блока анализа обращений к памяти, первый управляющий выход которого подключен к второму входу блока управления, третий и четвертый выходы и третий вход которого соединены соответственно со входами и с первым выходом первого влока синхронизации, а пятый выход подключен к другому входу коммутатора, другие входы блока кйнтроля по четности соединены соответственно с вторым выходом первого блока синхронизации и с числовыми выходами накопителя первого уровня и другими входами второго регистра числа, второй управляющий вход которого и третий вход второго блока синхро низации подключены к первому выходу блока, контроля по четности, второйвыход которого соединен с четвертым входом блока управления, пятый вход которого подключен к управляющему выходу формирователя управляющих сигналов, одни из адресных входов накопителя первого уровня соединены с выходами младших разрядов регистра адреса, а другие адресные входы к выходам элементов И первой группы первые входы которых соединены с вы ходами старших разрядов регистра ад реса и первыми входами регистров сщреса группы, выходы которых подключены к вторым входам элементов И первой группы, вторые входы регистров адреса группы являются другигли адресными входами устройства, а третьи и четвертые входы соединены с другими выходами блока анализа обращений к памяти, первый и второй управляющие входы которого подключены соответственно к второму выходу блок управления и к второму выходу второг блока синхронизации, а третий управляющий вход является третьим входом записи устройства, четверТ1дм входом записи и входами блокировйИ которого являются входы регистра меток неисправных страниц памяти, управлякхний вход формирователя управляющих сигналов является установочным входом устройства, управляющими входсии1й и выходом которого являются; соответственно входы с шестого по девятый и шестой Выход блока управления. . При этом блок анализа обращений к памяти содержит счетчики сигналов, группы элементов И ей второй по пятую, группы элементов ИЛИ, груп пу элементов НЕ, элементы И-НЕ, элемент ИЛИ и элемент НЕ, причем первые вхрдаг элементов И четвёртой и пятой групп и вторые входы элементов И пятой группы являются одними из .входов блока, другими входами которого явля ются вход элемента ИЛИ и первые вход элементов И третьей, группы, первые входы элементов И второй группы и вторые входы элементов И третьей группы, объединены и являются первым управляющим входом блока, вторым и Третьим управляюшшлн входами которог ящлгскпся соответственно объединенные третьи ВХОЩ1 элемейтов И пятой группы и объединенные вторые входы элементов И четвертой группы, выход эле мента ИЛИ является управляющем выходом блока и подключен к входу элем0ята И-НЕ, выход которого соединен с вторыми входами элементов И второй группы, выход каждого из котсфых пЬ в хлю1чен к входу вычитания соответ стлуЮщего счетчика сигналов, вход сложения которого соединен с выходом соответствующего из элементов И тре-j тьей группы, а дыход - с входами соч отввтствующих элемента ИЛИ первой группы и элемента И-НЕ группы, выход которого подключен к третьему входу соответствующего элемента И третьей группы, четвертый вход .каждого из элементов и пятой группы соединен С выходом соответствующего элемента НЕ группы, вход которого подключен к выходу соответствующего элемента ИЛИ первой группы и третьему входу соответствующего элемента И второй группы, выход первого из элементов ИЛИ первой группы соединены с пятыми входами элементов И пятой группы, кроме первого, выход каждого И -го (где и - число элементов ИЛИ в первой группе) последующего из элементов ИЛИ первой группы, кроме последнего, подключен к ( и +4)-му входу(|1 1)--го элемен.та И пятой группы, первые входы элементов И четвертой и пятой грурп соответственно объединены, а выходы подключены соответственно к первойУ и к второму входам элементов ИЛИ второй группы, выходы которых среди нены с входами установки в единицу соответствующих счетчиков сигналов/ выходы последних из элементов И четвертой и пятой групп и выходы элементов ИЛИ второй группы являются выходами блока;. 1На фиг.1 изобр ажена функциональная схема предлагаемого устройства, на фиг. 2 -4 - соответственна функциональные схемы блока анализа обращений к пг1мяти, первой и .второй групп сумматоров по модулю два и . блока управления. Предлагаемое устройство содержит накопитель 1 пёрвЪго уровня, регистр 2адреса, периеый 3 и второй 4 регнст ры 4исла, первый блок 5 синяронизг1- I ции, первую ГРУППУ элементов И б группу 7 .регистров адреса, кокмутатор 8 первуюи вторую группы 9 сулиаторов по модулю два, бЛок 10 контроля по четности, фор1№рователь 11 уп равляющих сигналов, блок 12 анализа обращений К памя.ти, регистр 13 меток неисгтравных страниц, блок 14 управления, накопитель 15 второго уровня и второй блок 16 синхронизации На фиг.1 обозначены первый 17;и второй 18входы записи, адресные входов 19и 20 устррйстваг.УАравЛякхцие входы и выход 25 11УетИй 26 и четвертый 27 входы записи, информационные вход 28 и выход 29, вход 30 блокировки и установочньй ; вход 31 устройства, первый.32 и второй 33 управляшцие входы второго рё1Ч1стра числ; теяяжоды 34 Младших регистра адреса, определяющие адрес слова страницы памяти, выходы 35 старших разрядов регистра адреса, ойред ёлякпще странг-щу пгшяти, информационные выходы 36, ък-у ходы 37 контрольных разрядов, информационные входы 38 и Входы 39 KOHT- J рольных разрядов йакопитеЛя первого/ уровня, выходы с первого по пятый / . 40-44 и входы с первого по пятый 4549 блока управления. Блок аналиаа обращений к памяти содержит фиг.2) счетчики ) сигналов где ТЛ - число страниц памят в накопителе первого уровня, вторую 51,- 51, третью 52, четвертую. 53 -53гя и пятую 544 -54,11 группы элементов И, первую 554 -- 55(п, вторую Seii 5бm группы элементов ИЛИ, групп элементов НЕ 57 - 57|ц, элементы И-НЕ , элемент ИЛИ 59 и элемент НЕ 60. ,На фиг.1 и 2 обозначены входы ei-GS и выходы 64-66 блока анализа обра{яений к памяти. На фиг.Зпоказашл первая 67 и вторая 68 группы сумматоров по модул Два для случая, напршлер, четьфех контрольных разрядов в накопителе пе вого уровня. На фиг.1 и 3 обозначены первые 69 и вторые 70 входы суммато ров по модулю два первой группы и вы ходы 71 сумматоров по модулю два вто рой группы. Блок управления содержит (фиг.4 элементы ШИ 72/73, элегюнты И 74 я 75, триггеры 76 и .77, элементы 78 и 79 задержки, элементы НЕ 80 и 81 и элемент ЗИ-ИЛИ 82. Устройство работает следующим аб-( разом. При обращении к устройству на ды 24 и 21 (фиг.1) блока 14 поступают соответственно сигналы Пуск- -и Операция 1 (единичное значеМ1«е соо ветствует операции записи, нулевое ч считывания, в регистр 2 записывается адрес обращения, в регистр 3 в случае операций, записи) - записываемое число. Сигналы Пуск 1, i Операция; 1 через выходы 41 и 40 блока 14 поступают через блок 16 на входы синхронизации накопителя 16, производят запуск блока 16, формирующего сигналы управления накопителем 15 li Код старших разрядов ал реса, определяющих страницу памяти, с выходов 35 регистра 2 поступает на первые входы элементов И 6. В случае Обращения к странице памяти, продублированной в накопителе 1, на одном из выходов элементов И 6 возникает единичный сигнал совпадения с1Дреса данной страницы с одним из адресов, зафиксированных в регистрах 7. Единичный сигнгш с одного из выходов элементов И 6 поступает на соответствующий адресный вход накопнтеля 1, одни из входов формирователя 11 и входы 61,-блока 12, с выхода 41 которого проходит на второй вход блока 14, где он ра;зрешает прохождение сигнгша Пуск 1 на выход 42 блока 5,на выход 43 которого поступает сигнал Операция Производится запуск блока 5, формиpynutero сигналы управления накопителем 1. При выполнении опергщии считывания число с выходов 36 накопителя 1 поступает на входы регистра 4 и на выходы 36 блока 10, причем контрольные разряды числа прег образуются по определенному закону сумматорами 9. Сигнало1.с выхода блока 5 производится опрос блока 10. В случае отсутствия ошибок в считан|ном слове сигналом с выхода 33 бЛока }10, поступающим на вхрд блока 16 и 1на вход 33 регистра 4, производится сброс и запись числа из накопителя 15в регистр 4. Сигнал О0 служено 1 с входа 47 блока 5 поступает на третий вход блока 14 и далее выдается на выход 25 устройства, прн этом триг гер 76 находится в нулевом состоянии, на выходе элемента НЕ 81 присутствует единичный сигнал. При обнаружении ошибок в считанном слове сигнале с входа 48 блокг1 10 производится установка триггера 76 в единичное состояние, запрещающее выдачу сигнала Обслужено 1 на выход 25. По окончании операции считывания из накопителя 15 сигналом с входа 32 блока 16 производится запись считанного .слова в регистр 4. Сигнал Оболуже- . но 2 поступает с входа 45 блока 16через первый.вход блока 14 ;элемент И 74, элемент ИЛИ 72, на выход 42и вход блока 5 и производит запуск его. Этот же сигнал через элемент И 74 блока 14 производит установку в единичное состояние триггера 77 и через э.лемент задержки 78 в нулевое состояние триггера 76. Единичный сигнал с выхода триггера 77 поступает на выход 44 ксммутатора 8 и ; разрешает прохождение числа, считан- i ного из накопителя 15,на входы 38 накопителя 1, причем контрольные разряды числа преобразуются по определенному закону cs iaTopaMH 9,у Этот же сигнал поступает на выход 43блока 5. Таким образом, число, считанное из накопителя 15, записы- , вается в накопитель 1. По окончании операции записи сигнал Обслужено 1 из блока 14 выдается на выход 25, одновременно устанавливает в нулевое состояние триггер 77. В случае обраЧ, деНия к устройству с операцией зариси в страницу памяти, продублированную в накопителе 1, операция вы- f полняется в обоих накопителях 1 и Записываемое число на входы 38 наког пителя 1 поступает с выходов регистра 3 через коммутатор 8, при этом также производится преобразование его контрольных разрядов в суммато pax 9. По окончании операции записи в накопителе 15 сигнал Обслужено 2 выдается на выход 25 устройства. Если обращение к устройству произво- : дится в страницу памяти, не продублированную в накопителе 1, то операция, производится только в накопителе 1 И по ее окончании на выход 25 выдае . ся сигнал Обслужено 2, В устройстве предусмотрена возможность автоматической замены стра ниц памяти в накопителе 1 на основе статистических данных о текущей час тоте их использования, Заменой стра ниц памяти управляет блок 12. Рассм рим процесс замещения страниц памяти. Пусть П; - статистический призна i-ft страницы памяти накопителя Г (где i l,2,...m и hi - число страни памяти в накопителе 1, kj - код управления преобразованием контроль ных разрядов числа при обращении к данной странице памяти. Каждой странице памяти в блоке 12 соответствует один из счетчиков 50щ (фиг.2) статистического признака данной страницы. При обращении к А -и странице памяти единичный сигнал с соответствующего выход элементов И 6 через вход 61 блока 12 поступает на первый вход соответ ствующего элемента И 52 и разрешае прохождение сигнала Пуск 1 с выхо да 41 на вход Сложение счетчика 50; , в котором производится лодиф кация статистического признакаП П;4К Если признак rij имеет максимально значение, т.е. соответствующий счет чик 50 находится в единичном состояНИИ, то на трет.ий вход соответствую щего элемента И 52 с выхода элемент И-НЕ 58 поступает нулевой потенциал и модификация не производится. При обращении к странице памяти не содержащейся в накопителе 1, на входе 61 блока 12 будут присутствовать только нулевые сигналы. Вследст вие этого на вторые входы всех элементов И 51 -51тс выхода элемента НЕ 60 поступает единичнйй сигнал, который разрешает прохождение сигнала Пуск 1 на входы Вычитание счетчиков 50,-50fn, в которых производится модификация статистических признаковП4.. При этом если какой-либо из признаков П 0, т.е. соответствующий из. счетчиков 50 находится в нулевом состоянии, то на первый вход элемента И 51J с выхода элемента ИЛИ 55 поступает нулевой сигнал и модификация признакаП, не. производится. Таким образом, нулевое значение .статистического признака свидетельствует о том, что часгота обращений к этой странице памяти стала меньше допустимой, следовательно, эту страницу памяти необходимо заменить. Единичный сигнал с выхода соответствующего элемента НЕ 57 поступает на четвертый вход элемента и 54 и разрешает прохожде-. ние сигнала .Обслужено 2 со входа 45 блока 12 через элемент и 54 и выход 65 на загтиси регистров 7. При этом в соответствующий регистр 7 производится запись адреса страницы последнего обращения, поступающего с выходов 35 регистра 2, Сигнал с выхода элемента И 54 через элемент ИЛИ 56 поступает на вход Установка 1 счетчика 50 и устанавливает максимальное значение статистического признака. Этот же сигнал через выходы 66 блока 12 поступает на вход формирователя 11 (фиг.1, в котором производится модификация кода управления преобразованием i контрольных разрядов К, ; ( +1. В дальнейшем при обращении к этой странице памяти единичный сигнал с выхода соответствующего из элементов И 6 поступает на вход формирователя 11 и разрешает прохождение кода У. с выхода формирователя 11 на вход 70 сумматоров 9. Максимально возможное число значений кода управления равно 2, где Е - число контрольных разрядов в накопителе 1. Рассмотрим преобразование контрольных разрядов в сумматорах 9 для случая четырех контрольных разрядов. Например, в накопителях 1 и 15 хранятся тридцатишестиразрядные числа с контрольным разрядом четности в каждом байте. Пусть, например, на управляющий вход 70 сумматоров 9 поступает код управления 1100. В этом случае первый и второй контрольные разряды чисел, записываемых в накопитель 1 и считываемых из него, будут инвертироваться в сумматорах 9, Единичное значение кода управления К; тахдвидешельствует о том, что дальнейшая смена i -ой страницы памяти накопителя 1 без предварительного ее обнуления запрещена, так как при этом возможно на- , хождение в данной странице чисел, принадлежащих разным страницам памяти накопителя 1, но с контрольными разрядами, преобразованными по одному и тому же закону. Для этого нулевой сигнал с выхода формирователя 11 поступает на вход 62 блока 12, на второй вход соответствующего элемента И 54 и запрещает замену этой страницы памяти. Если кодХ П)ахдля всех страниц памяти, то для дальнейшей работы устройства с накопителем 1 необходимо произвести его обнуление, т.е. по всем адре- . сам занести числа, контрольные разряды которых преобразованы в соответствии с кодом управления. В этом случае с выхода формирователя 11 в систему выдается сигнал обнуления накопителя 1. Таким образом, записб адреса новой страницы памяти в регистр 7 возможна при нулевом значении статистического признака и немаксимальном значении кода управления. Однако может оказаться, что несколько

страниц памяти удовлетворяют этим . усцовиям, например, страницы о номерами i г, п,.,. ,р, где ГП Vp П р При этом запись адреса новой страниг цы памяти производится в регистр 7 , с максимсшьным из этих номеров, например с номером П .

В остальные регистры 7 запись блокируется подачей нулевого сигнала с выхода элемента ИЛИ Б5 блока 12 на соответствующие входы элементов И 54 с номерами +1 i i m .Запись адресов страниц памяти в регистры 7 може. также осуществляться внешним образом В этом случае на вторые входы 20 подаются адреса страниц памяти, а на вход 26 - сигнал записи. Этот сигнал через элементы И 53 и выход 64 блока 12 поступает на .входы записи регистров 7, В устройстве предусмотрена возможность замены неисправных страниц памяти накопителя 15 страницами накопителя 1. Для этого перед иача-,. лом работы устройства в регистры заносятся адреса неисправных страниц памяти, а в соответствущие этим регистрам 7 разряды регистра 13 - нулевые метки. Нулевые сигналы с выходов регистра 13 через вход 63 блока.12 Г поступают на входы элементов И 53 и 54, блокируют сигналы записи адресов новых страниц Памяти в регкстры

1, хранящие адреса неисправных страниц. Работа устройства при обраще.нии к неисправным страницам памяти аналогична описанной. Обнуление накопителя 1 может быть организовано

параллельно во всех страницах памяти и производится одновременно с обс живанием обращений в накопителе 15, т.е. без приостановки работы устройства, что повылает быстродействие устройства. При этом единичный сигнал с второго входа 49 формирователя 11 поступает на вход блока 14, который блокирует запуск блока 5 при поступлении в усзгройство сигналов обращений на обслуживание. Запуск блока 5 при поступлении обращений для его обнуления г осуществляется сигналами Пуск 2, Операция 2 соответственно на входы 23 и 21 блока 14. По окончании обнуления на вход 31 формирователя 11 поступает сигнал, устанавливающий исходное нулевое состояние, при этом в устройстве возобновляется

работа с накопителем 1.

Технико-эконс шческие.преимущества предлагаемого устройства заключаются в его более высоких надежности и быстродействии по сравнению с известным.

Ы TfJ Т/г Ъ

.1

.LA19 f f

1 t f ii f

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент- США ( 4051461, кп | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Карцев М.А | |||

| Архитектура цифровых вычислительных систем | |||

| М., Наука, 1978, с.159, 202-204, 296 (прототип ). | |||

Авторы

Даты

1983-09-23—Публикация

1982-06-11—Подача