(54) УСТРОЙСТЮ ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ Х

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ | 1979 |

|

SU926653A2 |

| Цифровой фильтр | 1986 |

|

SU1354393A1 |

| Устройство для вычисления скользящего спектра | 1987 |

|

SU1418746A1 |

| Устройство для локального выравнивания гистограмм | 1986 |

|

SU1312614A1 |

| Генератор систем базисных функций Аристова | 1990 |

|

SU1748146A2 |

| Суммирующее устройство | 1987 |

|

SU1451681A1 |

| Устройство для возведения в степень | 1976 |

|

SU888106A1 |

| Устройство для параллельного формирования адресов | 1990 |

|

SU1734097A1 |

| Устройство для возведения в степень | 1976 |

|

SU744556A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1185329A1 |

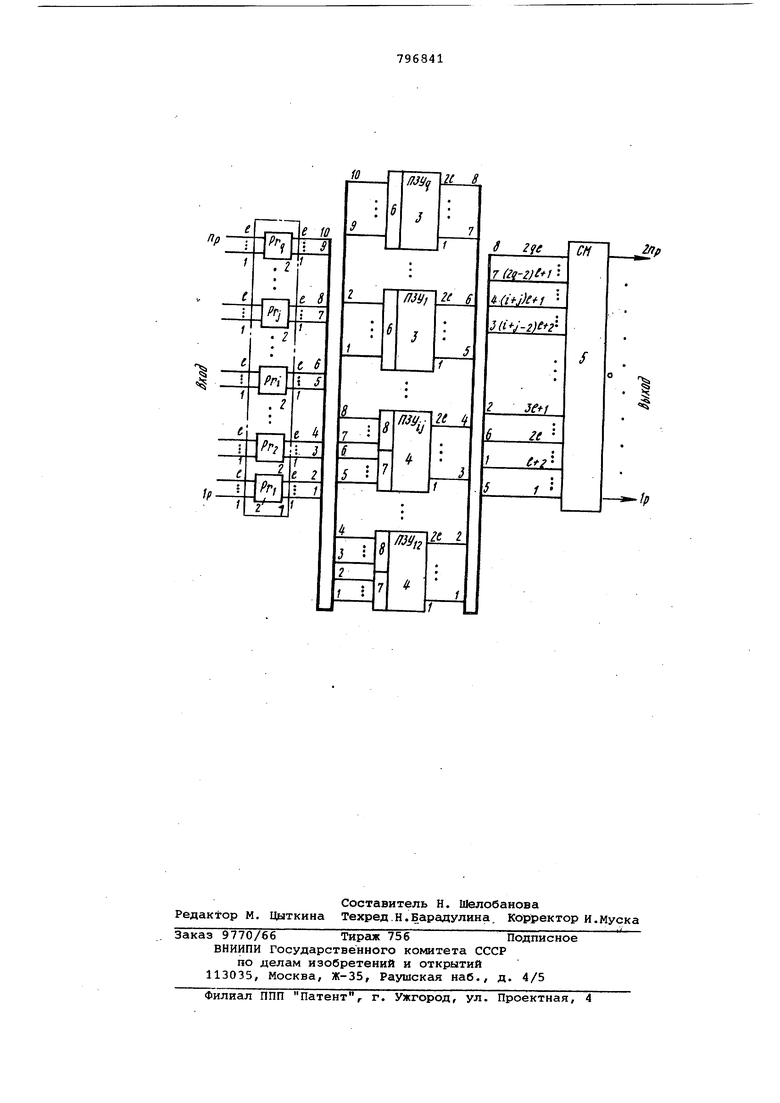

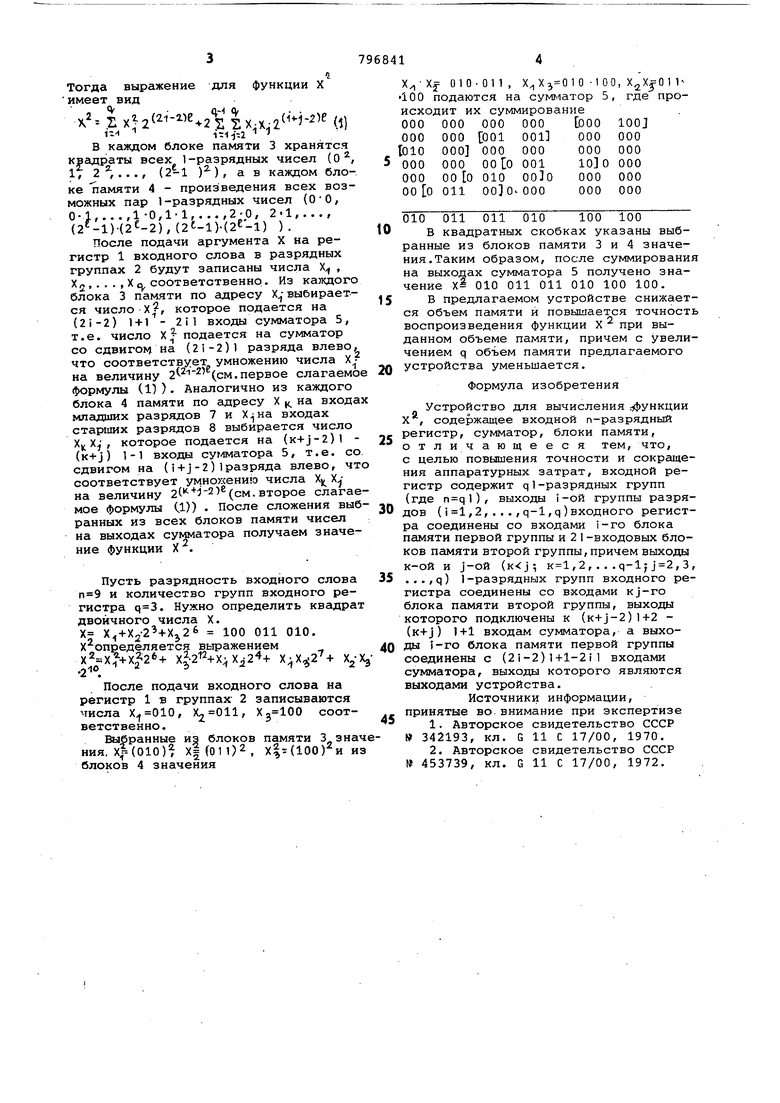

Изобретение относится к вычислительной технике и предназначено для -2 вычисления функции X . Устройство «может быть использовано в качестве специализированной ЦВМ или же входить в состав арифметического устройства универсальной ЦВМ. Известны устройства для вычисления функций, содержащие регистр входного слова, дешифратор, шифратор, выходной регистр ll , Недостаток устройств - невысокая точность восп юизведения функции. Наиболее близким по технической сущности к предлагаемому является j устройство для вычисления функции X содержащее входной п-разрядный регист сумматор, блоки памяти 2. Недостаток его заключается в низкой точности воспроизведения функции и большом объеме аппаратуры. - Цель изобретения-повышение точности и сокращение аппаратурных затрат. Поставленная цель достигается тем что в устройстве, содержащем входной п-разрядный регистр, сумматор/ блоки Пс1мяти, входной регистр содер хит qlразрядных групп (где п -ql), выходы 1-ой группы разрядов (i 1 , 2 , . . . .q-lj q) входного регистра соединены со входами i-ro блока памяти первой группы и 21-входовых блоков паг/1яти второй группы, причем выходы к- ой и j-ой ( ,2, .. .,q-l; ,3,. .. ,q) ) разрядных групп входного регистра соединены со входами Kj-ro блока памяти второй группы, выходы которого подключены к (K+J-2) l+2-(K+j) .)+ входам сумматора, а выходы i-ro блока памяти первой группы соединены с (2i-2). ) + 1-2{1 входами сумматора, выходы которого являются выходами устройства. , На чертеже изображена структурная: схема устройства. Она содержит входной регистр 1/ 1-разрядные группы 2 входного регистра, блоки 3 памяти ервой группы и 4 второй группы, сумматор 5, входы 6 блоков памяти первой группы, входы младших 7 и старших 8 разрядов/ блоков памяти второй группы. Устройство работает следующим образом. Двоичное число X эжно представить в виде ,....Х-2 - 4.х 2 - Х (. для функции X Тогда выражение имеет вид л- i хЬ( % (5) q-H v 1- ч В каждом блоке памяти 3 хранятся квадраты всех 1-разрядных чисел (0, 1, 2,.,., (2-1 )) , а в каждом блоке памяти 4 - произведения всех возможных пар 1-разрядных чисел (ОО, 0-1,...Д-0,1-1,. ..,2-0, 2-1,..., ()), (2t-l)-(2«-l) ). После подачи аргумента X на регистр 1 входного слова в разрядных группах 2 будут записаны числа Х , XjX С), соответственно. Из казкдого блока 3 памяти по адресу выбирается число X, которое подается на (21-2) 1 + 1 - 2М входы сумматора 5, т.е. число Х подается на сумматор со сдвигом на (2i-2)1 разряда влево, что соответствует умножению числа величину (см. первое слагаемо формулы (1)). Аналогично из каждого блока 4 памяти по адресу X ц, на входа младших разрядов 7 и входах старших разрядов 8 выбирается число , которое подается на (K+j-2)l (K+J) 1-1 входаа сугчматора 5, т.е. со сдвигом на (i+j-2)1разряда влево, чт соответствует умнохсению числа Ху на величину 2( (см. второе слагае мое ФОРМУЛЫ Ш) . после сложения выб .,„„„« „о T,v «TTovnn пямстти чипел ранных из всех блоков памяти чисел на выходах сумматора получаем значение функции Х. Пусть разрядность входного слова и количество групп входного регистра . Нужно определить квадрат двоичного числа X. Х X + X2-2 +Xj26 100 Oil 010. X определяется выражением Х Х +Х|2+ Х -22+Х;, Х,24+ Х2-Х После подачи входного слова на регистр 1 в группах 2 записываются числа , , соответственно. Выбранные из блоков памяти 3 знач .Xfe(OlO) x|(0l02, х|М100)и из 4 значения блоков XxiXj 010-011, о -1 00, 1400 подаются на сумматор 5, где происходит их суммирование 000 000 000 000 ООО 100 000 000 001 001 000 000 lOlO 000 000 000 000 000 000 000 001 000 000 00 о 010 OOlO 000 000 00 о 011 000 000 000 оТо on oTi olo Too Too в квадратных скобках указаны выбранные из блоков памяти 3 и 4 значения.Таким образом, после суммирования на выходах сумматора 5 получено значение Х 010 011 011 010 100 100. В предлагаемом устройстве снижается объем памяти и повышается точность воспроизведения функции X при выданном объеме памяти, причем с увеличением q обЪ|ем памяти предлагаемого устройства уменьшается. Формула изобретения Устройство для вычисления :5ФУНкции X , содержащее входной п-разрядный регистр, сумматор, блоки памяти, отличающееся тем, что, с целью повышения точности и сокргицения аппаратурных затрат, входной регистр содержит q1-разрядных групп Т (Г-ll П оУвходноТрегис : ° U--L,/;,... ,q i,q;ВХОДНОГО регист ра соединены со входами 1-го блока памяти первой группы и 2 1 -входовых блоков памяти второй группы, причем выходы к-ой и j-ой ( ,2,...q-1Jj 2,3, ...,q) 1-разрядных групп входного регистра соединены со входами Kj-ro блока памяти второй группы, выходы которого подключены к ()1+2 (K+J) 1+1 входам сумматора, а выхоДы i-ro блока памяти первой группы соединены с (21-2)1+1-211 входами сумматора, выходы которого являются выходами устройства. Источники информации, принятые во.внимание при экспертизе 1. Авторское свидетельство СССР № 342193, КЛ. G 11 С 17/00, 1970. 2. Авторское свидетельство СССР № 453739, КЛ. G 11 С 17/00, 1972.

tp

Авторы

Даты

1981-01-15—Публикация

1976-09-17—Подача