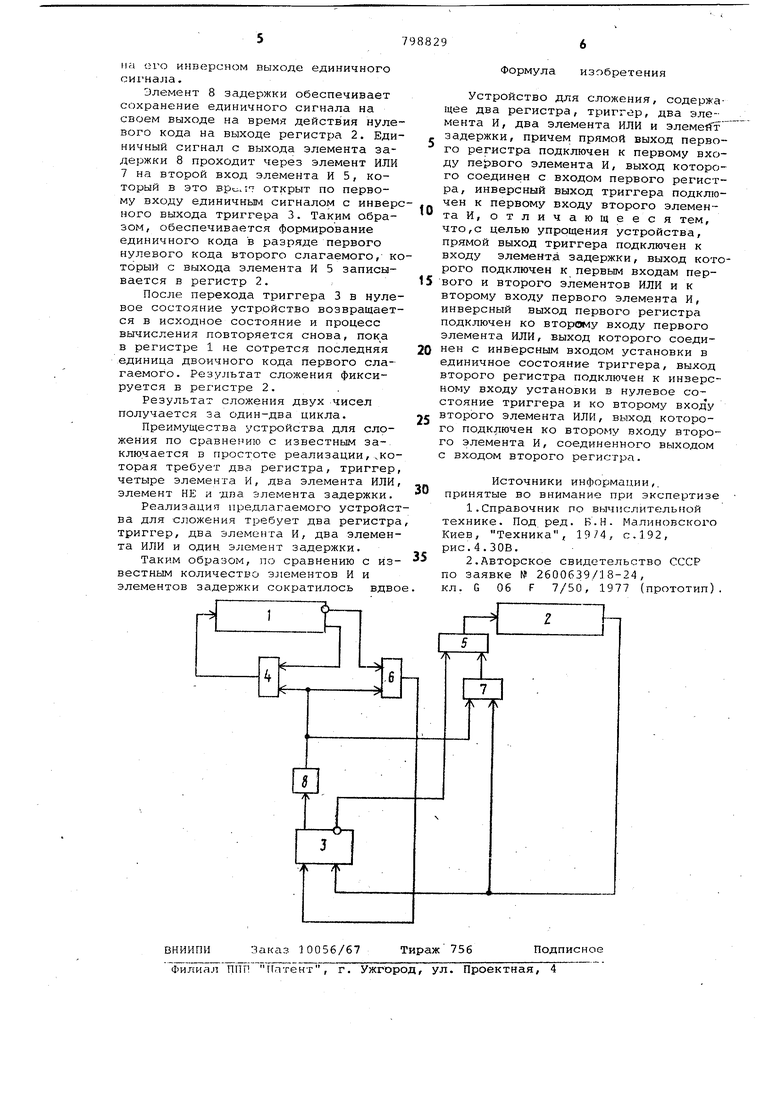

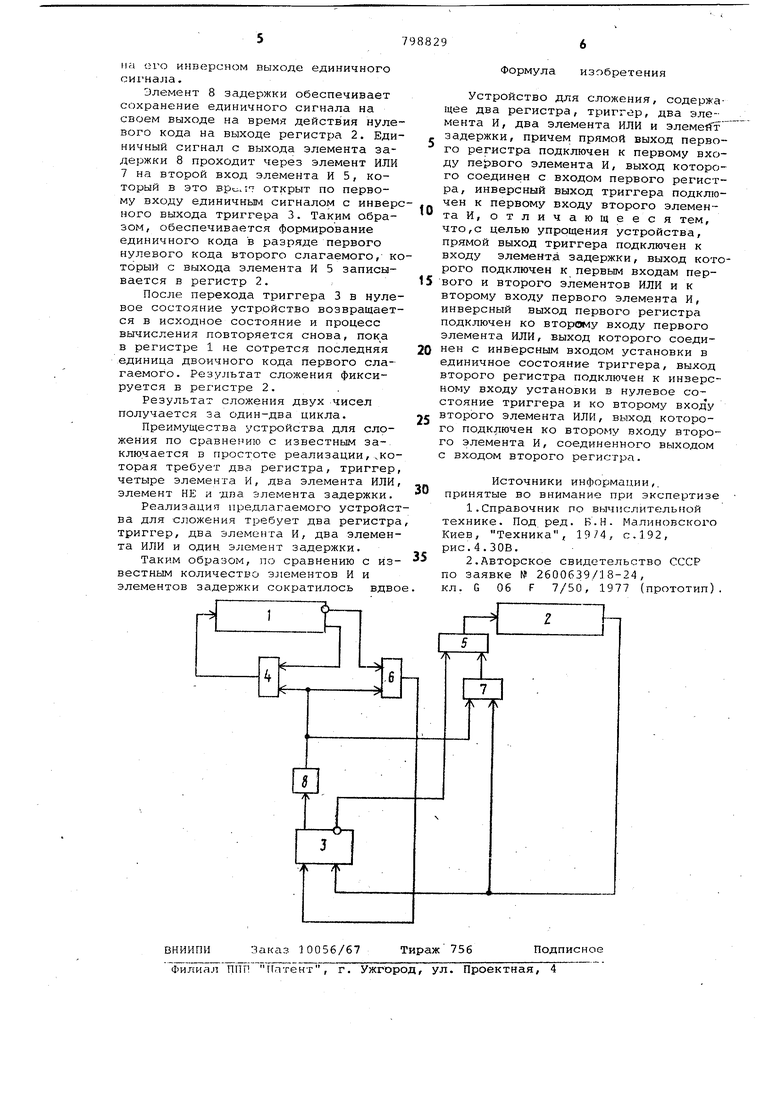

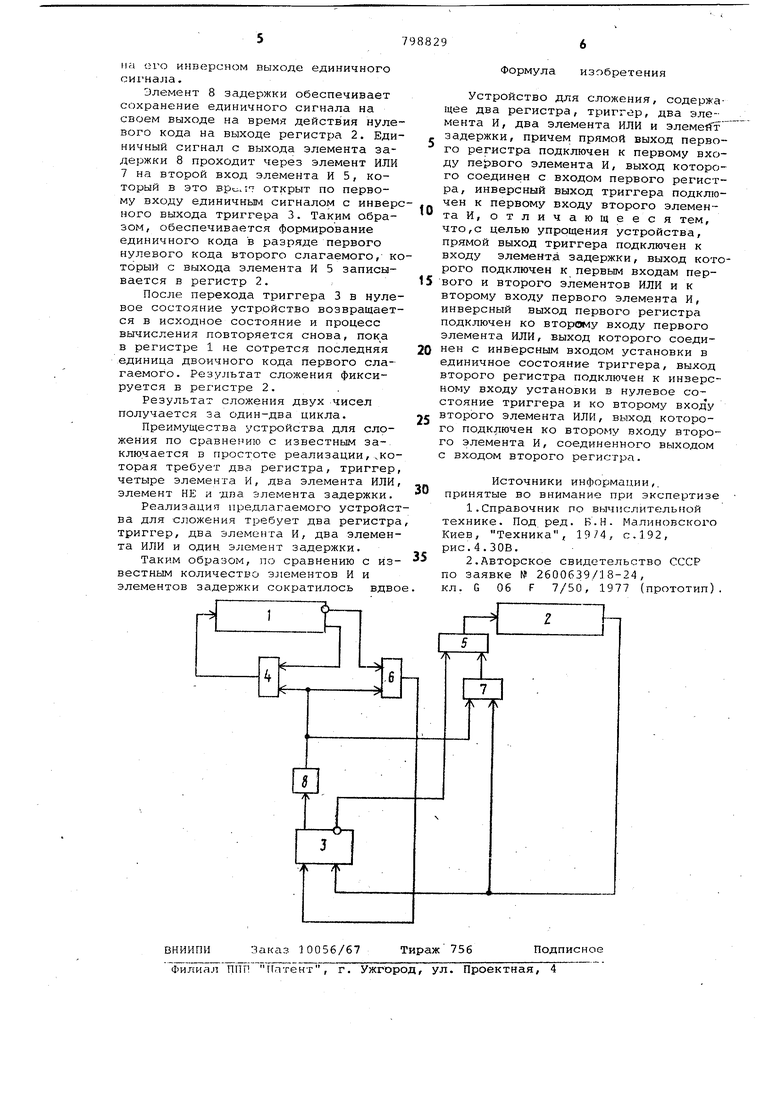

первого регистра подключен ко второму входу первого элемента ИЛИ, выход которого соединен с инверсным входом установки в единичное состояние триг гера, выход второго регистра подключен к инверсному входу установки в нулевое состояние триггера и ко втор му входу второго элемента ИЛИ, выход которого подключен ко второму входу второго элемента И, соединенного выходом с входом второго регистра. На чертеже изображена структурнсш схема устройства для сложения. Схема содержит два регистра 1 и 2, триггер 3, два элемента И 4 и 5, два элемента ИЛИ б и 7,,элемент 8 задержки.. Прямой выход регистра 1 подключен к первому входу элемента И 4, выход которого соединен с входом регистра 1. Инверсный выход триггера 3 подклю чен к первому входу элемента И 5. Прямой выход триггера 3 подключен к входу элемента задержки 8, выход которого подключен к первым входам элементов ИЛИ б и 7 и к второму входу элемента И 4. Инверсный выход первого регистра подключен ко второму входу элемента ИЛИ б, выход которого соединен с инверсным входом установки в единичное состояние триг гера 3. Выход регистра 2 подключен к инверсному входу установки в нулевое состояние триггйра 3 и ко второ, му входу элемента ИЛИ 7, выход которого подключен ко второму входу элемента И 5, соединенного с входом регистра 2. . , . Триггер 3 КЙ -типа собран из двух элементов И-НЕ и имеет инверсные входы установки в нулевое или единичное состояние. Устройство для сложения работает следующим образом. В исходном состоянии триггер 3 находится в нулевом состоянии. В регистр1 по синхронизирующим импул сам тактовой частоты последовательно начиная с младших разрядов, записывается двоичный код первого слагаемого. Двоичный код BTOporoi слагаемо го записывается в регистр 2 и считы вается с его выхода по синхронизирую щим импульсам, задержаннЕЛМ на полпериода тактовой частоты относитель но синхронизирующих импульсов регис ра 1. . В исходном состоянии элемент И 4 закрыт нулевым сигналом прямого вых да триггера 3, который передается через элемент 8 задержки на второй вход элемента И 4. На первых входах элементов ИЛИ 6 и 7 действует нуле вой сигнал прямого выхода триггера Единичный сигнал инверсного выхо да триггера 3 по.цде-рживает по перво му входу элемент И 5 в открытом со-зтоянии. Если в мпад1лих рапядам iieriBoio лагаемого записаны нулевые 1сол1з), то на инверсном выходе регистра 1 счиывается единичный сигнал, который роходит на выход элемента ИЛИ 6 и далее на инверсный вход установки в диничное состояние триггера 3. Таким Образом, триггер 3 сохраняет нулевое состояние, а младшие разряды второго слагаемого переписываются без изменения с выхода регистра 2 на его вход через элементы ИЛИ 7 и И 5. Так продолжается до первой.младшей единицы в двоичном коде первого слагаемого/ которая вызывает появление нулевого сигнала на инверсном выходе регистра 1, который приводит к формированию нулевого кода на выходе элемента ИЛИ б, поскольку на его,первый вход поступает нулевой сигнал с выхода элемента 8 задержки. Нулевой сигнал с выхода элемента ИЛИ б,поступает на инверсный вход установки триггера 3 переведет его в единичное состояние. Установка триггера 3в единичное состояние приводит к формированию на его прямом выходе единичного сигнала,, а на инверсном выходе нулевого сигнала. Элемент 8 задержки обеспечивает задержку перепада на прямом выходе триггера 3 на время действия единичного сигнала первой единицы кода первого слагаемого на прямом выходе регистра 1. В результате элемент И 4закрывается по второму входу нулевым сигналом с выхода элемента 8 задержки во время действия единичного сигнала первой единицы первого слагаемого на выходе регистра 1. Этим обеспечивается стирание первой единицы двоичного кода первого слагаемого, которая вызывает переход триггера 3 в единичное состояние. Спустя время задержки элемента В после установки триггера 3 в единичное состояние на первыхвходах элементов ИЛИ б и 7, а также на втором входе элемента И 4 устанавливается единичный сигнал прямого выхода триггера 3. Элемент И 5 закрывается по первому входу нулевым сигналом инверсного выхода триггера 3. Таким образом, после первой единицы, котораястирается, разряды первого слагаемого переписываются без изменения с прямого выхода регистра 1 на его вход через элемент и 4, а в это время в регистр 2 записываются нулевые коды с выхода элемента И 5, включая одноименный разряд первой единицы слагвемого. Так продолжается до первого нулевого кода второго слагаемого, который, поступая на инверсный вход установки триггера 3, переводит его в.нулевое состояние. Переход триггера 3 в нулевое состояние приводит к установке на о.гп прямом выходе нудгевого си)нала и

на его инверсном выходе единичного сигнала.

Элемент В задержки обеспечивает сохранение единичного сигнала на своем выходе на время действия нулевого кода на выходе регистра 2. Единичный сигнал с выхода элемента задержки 8 проходит через элемент ИЛИ 7 на второй вход элемента И 5, который в это вролт открыт по первому входу единичным сигналом с инверсного выхода триггера 3. Таким образом, обеспечивается формирование единичного кода в разряде первого нулевого кода второго слагаемого, который с выхода элемента И 5 записывается в регистр 2.

После перехода триггера 3 в нулевое состояние устройство возвращается в исходное состояние и процесс вычисления повторяется снова, в регистре 1 не сотрется последняя единица двоичного кода первого слагаемого. Результат сложения фиксируется в регистре 2.

Результат сложения двух чисел получается за один-два цикла.

Преимущества устройства для сложения по сравнению с известным заключается в простоте реализации,.которая требует два регистра, триггер четыре элемента И, два элемента ИЛИ, элемент НЕ; и -дяа элемента задержки.

Реализация предлагаемого устройства для сложения требует два регистра триггер, два элемента И, два элемента ИЛИ и один элемент задержки.

Таким образом, по сравнению с известным количество элементов И и элементов задержки сократилось вдво

Формула изобретения

Устройство для сложения, содержащее два регистра, триггер, два элемента И, два элемента ИЛИ и элемент задержки, причем прямой выход первого регистра подключен к первому входу первого элемента И, выход которого соединен с входом первого регистра, инверсный выход триггера подключен к первому входу второго элеменoта И, отличающееся тем, что,с целью упрощения устройства, прямой выход триггера подключен к входу элемента, задержки, выход которого подключен к первьпи входам пер5вого и второго элементов ИЛИ и к второму входу первого элемента И, инверсный выход первого регистра подключен ко второму входу первого элемента ИЛИ, выход которого соеди0нен с инверсным входом установки в единичное состояние триггера, выход второго регистра подключен к инверсному входу установки в нулевое состояние триггера и ко второму входу второго элемента ИЛИ, выход которо5го подключен ко второму входу второго элемента И, соединенного выходом с входом второго регистра.

Источники информации,,

0 принятые во внимание при экспертизе

1.Справочник по вычислительгюй технике. Под ред. Б.Н. Малиновского Киев, Техника, 1974, с.192, рис.4.ЗОВ.

5

2.Авторское свидетельство СССР по заявке № 2600639/18-24, кл. G 06 F 7/50, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения | 1979 |

|

SU851402A1 |

| Интегро-дифференциальный вычис-лиТЕль | 1979 |

|

SU798902A1 |

| Устройство для сравнения двоичныхчиСЕл | 1979 |

|

SU822178A1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2395833C2 |

| Многоканальный десятичный счетчик | 1979 |

|

SU824443A1 |

| Устройство для счета импульсов | 1979 |

|

SU809258A1 |

| СПОСОБЫ ВЫПОЛНЕНИЯ ЭЛЕМЕНТАРНЫХ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ (ЭВО) И УСТРОЙСТВО ИХ ОСУЩЕСТВЛЕНИЯ | 2013 |

|

RU2553221C2 |

| Устройство для вычитания | 1979 |

|

SU851403A1 |

| Устройство для вычитания | 1978 |

|

SU746513A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

Авторы

Даты

1981-01-23—Публикация

1978-12-26—Подача