(54) УСТРОЙСТВО ДЛЯ ИЛЧИТАНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычитания | 1978 |

|

SU811249A1 |

| Устройство для вычитания | 1978 |

|

SU736098A1 |

| Устройство для вычитания | 1979 |

|

SU789992A1 |

| Устройство для вычитания | 1977 |

|

SU693370A1 |

| Устройство для вычитания двоично-десятичных кодов | 1982 |

|

SU1043640A1 |

| Устройство для вычитания | 1978 |

|

SU746513A1 |

| Десятичный вычитающий счетчик | 1979 |

|

SU809584A1 |

| УСТРОЙСТВО ВЫЧИТАНИЯ | 1972 |

|

SU435523A1 |

| Счетчик для вычитания | 1984 |

|

SU1228276A1 |

| Устройство для сложения-вычитания | 1981 |

|

SU1005037A1 |

Изобретение относится к вычислительной технике и предназначено для вычитания двух двоичных чисел. Известно устройство для вычитания содержащее два регистра, однозарядны сумматор на три входа и два триггера 1 . Недостатком этого устройства явля ется сложность его реализации. Известно также устройство для вычитания, содержащее два регистра и триггер, единичный выход которого соединен с первым входом первого элемента И, нулевой выход - с первым входсий второго элемента И, единичный вход - с выходом первого элемента задержки, соединенного со входом и выходом второго элемента И, второй вход, которого подключен ко второму входу первого элемента И и выхо ду первого регистра, соединенного входом с выходом первого элемента И причем выход второго регистра соединен с первым входом третьего элемента И и со входом инвертора, выход которого подключен к первому входу четвертого элемента И, соединенного выходом с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу третьего элед«еита и, а выход - к входу второго регистра, нулевой выход триггера соединен со вторым входом третьего элемента И, единичный выход - со вторым входом четвертого элемента И, нулевой вход - с выходом второго элемента задержки, вход которого подключен к выходу второго элемента ИЛИ, / соединенного первым входом с выходом второго регистра и вторым входом с шиной сброса Г2. . Недостатком этого устройства для вычитания заключается в относительно большом количестве логических элементов. Наиболее .близким к предлагаемому является устройство для вычитания, содержащее два регистра и триггер, соединенный единичным выходом с первым входом первого элемента И, нулевьпй выходом с первым входом второго элемента И, единичным входом через первый элемент задержки с выходом второго элемента И, второй вход которого соединен со вторым входом первого элемента И и выходом первого регистра, соединенного входом с выходом первого элемента И, причем вход второго регистра соединен с выходом первогс5 элемента ИЛИ,

первый вход которого соединен с выходом третьего э 1емента И, соединенного первым входом с выходом второго регистра и первым входом второго элемента ИЛИ, второй вход которого подключен к шине сброса,единичный вход триггера соединен со вторым входом первого элемента ИЛИ, нулевой выход триггера соединен череэ второй элемент задержки со вторым входом третьего элемента И, нулевой вход триггера соединен с выходом второго элемента ИЛИ з.

Недостатком такого устройства является его относительная сложность.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем что в устройство для вычитания, содержащее два регистра, два элемента И, элемент ИЛИ и элемент задержки, вход которого соединен с выходом первого элемента И, выход первого регистра соединен с первым входом второго элемента И, выход которого соединен со входом первого регистра введен элемент ИСКЛЮЧЛЩЕЕ ИЛИ, выход которого соединен со входом второго регистра, первый вход - с прямым выходом второго регистра и второй вход - с выходом элемента ИЛИ и первым входом первого элемента И, который подключен вторым и третьим входами соответственно к инверсному выходу второго регистра и к шине сброса устройства, выход первого регистра соединен с первым входом элемента ИЛИ, выход элемента задержки подключен ко вторым входам элемента ИЛИ и второго элемента И.

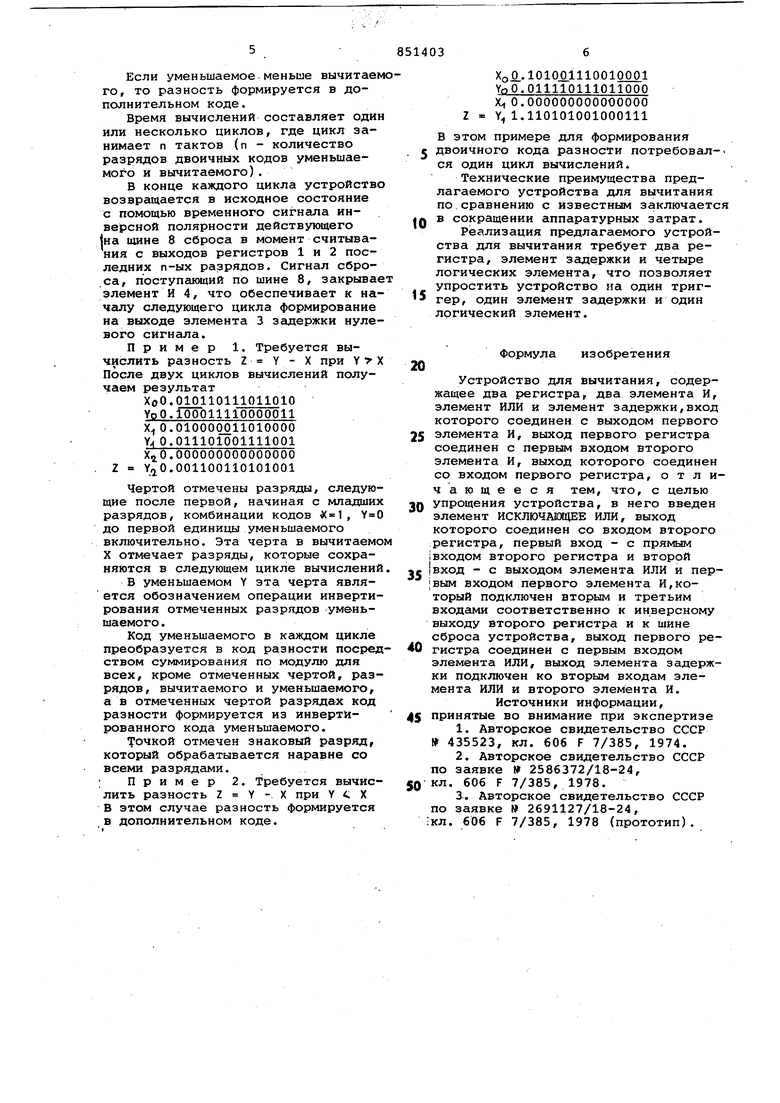

На чертеже изображена структурная схема устройства для вычитания.

Предлагаемое устройство содержит два регистра 1 и 2, элемент 3 задержки, два элемента И 4 и 5, элемент ИЛИ 6, элемент ИСКЛЮЧАЩЕЕ ИЛИ 7 и шину 8 сброса.

Вход регистра 1 соединен с выходом элемента И 5. Вход регистра 2 подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7, первый вход которого соединен с прямым вькодом регистра 2, а второй вход - с первым входом элемента И 4 и выходом Ьлемета ИЛИ 6.

Выход элемента 3 задержки соедине с перйыми входалш элемента И 5 и элеме рта ИЛИ б, который подключен вторым входом к выходу регистра 1 и BTOpc iy входу элемента И 5.

Вход элемента 3 задержки соединен с выходом элемента И 4, второй и третий входы которого подключены соответственно к инверсному выходу регистра 2 и к шине 8 сброса.

Устройство для вычитания работает следующим образом.

в регистре 1 содержится двоичный код вычитаемого,а в регистре 2 уменьшаемого. На выходе элемента 3 задержки действует нулевой сигнал. Двоичные коды вычитаемого и уменьшаемого считываются с выходов регистров 1 и 2 последовательно, начиная смладших разрядов. На входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 7 поступают сигналы двоичных кодов уменьшаемого и вычитаемого соответственно с выхода регистра 2 и через элемент ИЛИ-6 с выхода регистра 1. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7 суммирует по модулю два двоичные коды уменьшаемого и вычитаемого и результат записывается в регистр 2. В это время младшие разряды вычитаемого стираются с помощью элемента И 5, который закрыт нулевым сигналом выхода элемента задержки 3

Так продолжается до первой комбинации единичного кода вычитаемого и нулевого кода уменьшаемого. В этом случае срабатывает элемент И 4, на выходе которого формируется единичный сигнал. В следующем такте единичный сигнал выхода элемента И 4 начинает действовать на выходе элемента 3 задержки, что приводит к открыванию элемента И 5 и формированию на выходе элемента ИЛИ б единичного сигнала.

После первой комбинации 1-0 кодов вычитаемого и уменьшаемого элемент И 4 поддерживается в открытом состоянии единичным сигналом элемента ИЛИ б до сигнала первой единицы уменьшаемого, который, поступая с инверсного выхода, регистра 2 переводит элемент И 4 в закрытое состояние В следующем такте нулевой сигнал выхода элемента И 4 начинает действовать на выходе элемента задержки 3, возвращая устройство в исходное состояние .

Таким образом, после первой комбинации 1-0 кодов вычитаемого и уменьшаемого до первой единицы уменьшаемого, включая и время обработки этого разряда уменьшаемого, на выходе элемента 3 задержки действует единичный сигнал, который поддерживает элемент и 5 в открытом состоянии и через элемент ИЛИ б° поддерживает единичный сигнал на втором входе элемента ИСКЛЮЧАКВДВЕ ИЛИ 7,что переводит элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 7 в режим инвертирования двоичного кода уменьшаемого. В этом случае, с выхода регистра 2 на его вход записывается инвертированный код уменьшаемого, а с выхода регистра 1 на его вход через элемент И 5 Переписывается без изменения двоичный код вычитаемого.

Дальнейшие вычисления повторяются аналогичным образом до полной очистки регистра 1. В регистре 2 фиксируется двоичный код разности.

Если уменьшаемое меньше вычитаемого, то разность формируется в дополнительном коде.

Время вычислений составляет один или несколько циклов, где цикл занимает п тактов (п - количество разрядов двоичных кодов уменьшаемого и вычитаемого).

В конце каждого цикла устройство возвращается в исходное состояние с помощью временного сигнала инве рсной полярности действующего на ишие 8 сброса в момент считывания с выходов регистров 1 и 2 последних п-ых разрядов. Сигнал сброса, поступгиощий по шине 8, закрывает элемент И 4, что обеспечивает к началу следующего цикла формирование на выходе элемента 3 задержки нулевого сигнала.

Пример 1. Требуется вычислить разность Z Y - X при Y X После двух циклов вычислений получаем результат

ХрО.010110111011010

YoO.fOOTOllllOOOOOll

.010000011010000

Уи 0.011101001111001

.000000000000000 Z Х,0.001100110101001

Чертой отмечены разряды, следующие после первой, начиная с младших разрядов, комбинации кодов 1, до первой единицы уменьшаемого включительно. Эта черта в вычитаемом X отмечает разряды, которые сохраняются в следующем цикле вычислений.

В уменьшаемом У эта черта является обозначением операции инвертирования отмеченных разрядов уменьшаемого .

Код уменьшаемого в каждом цикле преобразуется в код разности посредством суммировани.я по модулю для всех, кроме отмеченных чертой, разрядов, вычитаемого и уменьшаемого, а в отмеченных чертой разрядах код разности формируется из инвертированного кода уменьшаемого.

Точкой отмечен знаковый разряд, который обрабатывается наравне со всеми разрядами.

Пример 2. Требуется вычислить разность 2 У -. X при У С X В этом случае разность формируется в дополнительном коде.

ХоО.101001110010001

УоО.011110111011000

.000000000000000

Z - У 1.110101001000111

в этом примере для формирования 5 двоичного кода разности потребовал-, ся один цикл вычислений.

Технические преимущества предлагаемого устройства для вычитания по.сравнению с известным заключается в сокращении аппаратурных затрат.

Реализация предлагаемого устройства для вычитания требует два регистра, элемент задержки и четыре логических элемента, что позволяет упростить устройство на один триггер, один элемент задержки и один логический элемент.

Формула изобретения

20

Устройство для вычитания, содержащее два регистра, два элемента И, элемент ИЛИ и элемент задержки,вход которого соединен с выходом первого

элемента И, выход первого регистра соединен с первым входом второго элемента И, выход которого соединен со входом первого регистра, отличающееся тем, что, с целью

упрощения устройства, в него введен элемент ИСКЛЮЧМЩЕБ ИЛИ, выход которого соединен со входом второго регистра, первый вход - с прямым (ВХОДОМ второго регистра и второй

|вход - с выходом элемента ИЛИ и пер|вым входом первого элемента И,который подключен вторым и третьим входс1ми соответственно к инверсному выходу второго регистра и к шине сброса устройства, выход первого регистра соединен с первым входом

элемента ИЛИ, выход элемента задержки подключен ко вторым входам элемента ИЛИ и второго элемента И. Источники информации,

принятые во внимание при экспертизе

кл. 606 F 7/385, 1978.

кл. 606 F 7/385, 1978 (прототип).

Авторы

Даты

1981-07-30—Публикация

1979-11-15—Подача