Изобретение относится к вычислительной технике, в частности к упра ляющим устройством, основанным на микропрограммного управлен и может быть использовано в специал зированных управляющих процессорах для реализации программ, ориентированных на разветвленный логический анализ, при наличии программу для выполнения которых требуется процедура приоритетного прерывания, на-i пример программ реального масштаба, времени. Известно микропрограммное устрой ство, содержащее блок памяти, регис ры , схемы приема информации, такто вый генератор, счетчик тактов, узел раз решен ия считывание, элементы И, НЕ и дешйфраторьа Cl . Недостатком этого устройства является отсутствие возможности многоразрядной модификации адресов микрокоманд. Наиболее близким по технической сущности к предлагаемому является програм.1ное устройство, содержащее дешифратор, шифратор, регистр запро сов, регистр адреса, дополнительный регистр адреса, блок элементов ИЛИ группу элементов И ,2 . Недостатками устройства являются отсутствие возможности организации УСЛОВНЫХ переходов в nporpavwe и работы с прерьшанием. Цель изобретения - расширение функциона льных возможностей за счет осуществления режима работы с прерыванием. Эта цель достигается тем, что в микропрограммное устройство управления, содержсодее дешифратор, группа выходов которого соединена с группой адресных входов дешифратора и является группой адресных выходов устройства, группа выходов шифратора соединена.с первой группой входов блока элементов ИЛИ, вторая группа входов которого является первой группой входов устройства, группа. ВХОДОВ дешифратора соединена с группой разрядных выходов регистра адреса, группа информационных входов которого соединена с группой разрядных выходов дополнительного регистра адреса, введены коммутатор, регистр прерываний, элементы 1Л НЕ, причем группа входов регистра прерываний соединена с группой выходов блока элементов ИЛИ и с первой группой входов коммутатора, вторая

группа входов которого соединена с группой разрядных выходов регистра прерываний, вход которого соединен с выходом элемента И, первый вход которого соединен с выходом дешифратора, с первым входом коммутатора и через элемент НЕ со вторым входом коммутатора, второй входэлемента И соединен с первьм входом синхронизации устройства, второй и третий входы синхронизации которого соединены соответственно с входами синхронизации дополнительного регистра адреса и регистра :адреса, входы прерывания которых соединены с входом прерывания устройства и с третьи входом элемента И, группа выходов коммутатора соединена с группой информационных входов дополнительного регистра адреса, группа информационных входов шифратора соединена со второй группой входов устройства.

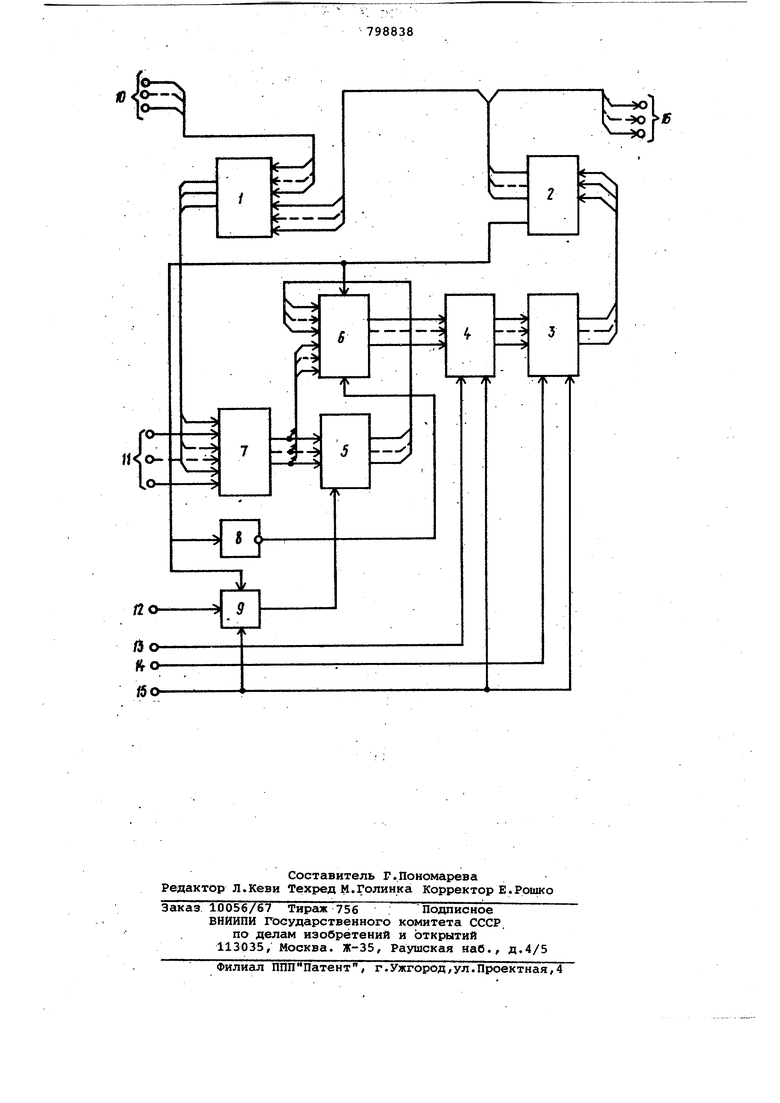

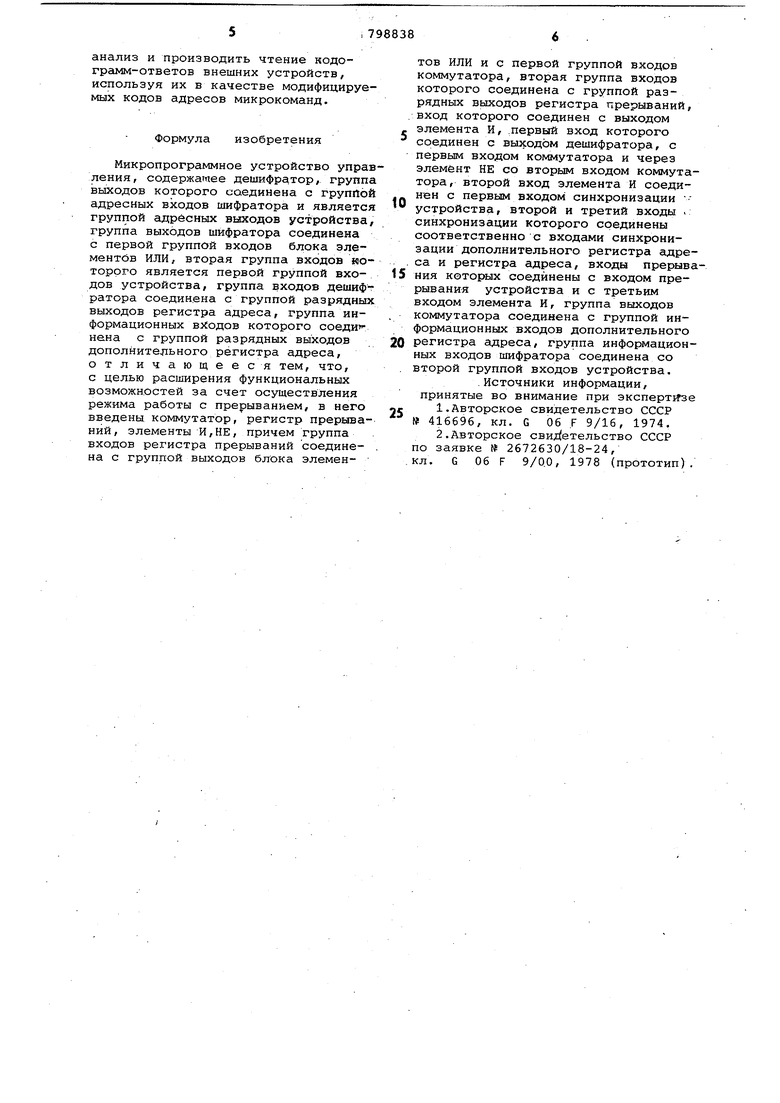

На чертеже приведена блок-схема устройства.

У.стройство содержит шифратор 1, дешифратор 2, регистр 3 адреса, дополнительный регистр 4 адреса, регистр 5 прерываний, коммутатор б, блок 7 элементов ИЛИ, элемент НЕ 8, элемент И 9, вторую группу входов 10, первую группу входов 11, входы 12-14 синхронизации вход 15 прерывания, группу выходов 16 устройства.

Устройство работает следующим образом.

После того, как устройство закончило развертывание во времени очередной программы, с нулевого выхода дешифратора 2 на соответствующий выход группы выходов 16 поступает сигнал, указывающий на то, что устройство свободно от выполнения прораммыи находится в режиме ожидания сигналов запроса на работу очередной микропрограммы. Один из нескольких разделенных во времени сигналов запроса поступает на соответствующий вход второй группы входов 10 и вызывает работу соответствующей микропрограммы. Сигнал запроса, поступая на соответствующий вход шифратора 1 задает на его выходе код адреса миг; крокоманды, поступающей 4ejie3 блок 7 элементов ИЛИ на входы регистра 3 прерываний и через коммутатор б на входы дополнительного адреса 4. Сигналы синхронизации, поступающие последовательно на входы 12-14 синхронизации производят запись кода адреса микрокоманды в регистр 5 прерываний, дополнительный регистр 4 адреса и регистр 3 адреса.

В результате на соответствующем выходе дешифратора 2 появляется сигнал, представляющий собой (единую), микрокоманду, которая поступает на один из выходов 16 и на соответствующий вход шифратора 1, з.адавая адрес следующей микрокоманды. Таким образом, после вызова устройство генерирует последовательность микрокоманд, реализующих работу соответствующей микропрограммы. Адреса- микрокоманд задаются соответствующими соединениями выходов дешифратора 2 с входами шифратора 1. Последняя микрокоманда каждой микропрограммы на вход шифратора 1 не подается. В результате на его выходах появляется нулевой адрес, по которому возбуждается нулевой выход дешифратора 2 и устройство переходит в режим ожидания очередной временной метки, имитирующей работу соответствующей микрокоманды.

Устройство позволяет производить многоразрядную кодовую модификацию адреса микрокоманды путем дизъюнкции на блоке 7 элементов ИЛИ кода основного адреса, поступающего с выходов шифратора 1 на первые входы блойа 7 элементов ИЛИ и модифицирующего кода поступающего на вторые входы блока 7 элементов ИЛИ с соответствующих входов первой группы входов 11. При-этом, за счет дизъюнкции разрядов модифицирующего кода с разрядными кода основного адреса, находящимся в нулевом состоянии и определяется ветвление программы.

Работа с прерыванием производится следующим образом. Сигнал прерывания, поступая с входа 15 прерывания закрывает элемент И 9, прекращая поступление синхротактов на вход управления регистра 5 прерываний и обнуляя содержимое дополнительного регистра 4 адреса и регистра 3 адреса. Таким образом, работа текущей микропрограммы прерывается, а адрес микрокоманды,с которой начнется работа после возврата к прерванной программе, сохраняется в регистре 5 прерываний. После этОго соответствующий сигнал запроса, поступая на соответствующий вход второй-группы входо 10, запускает прерывающую программу, последняя микрокоманда которой адресуется к выходу дешифратора 2, сигна с которого открывает элемент И 9 и на один такт подключает выходы регистра 5 прерываний через коммутатор 6 к входам дополнительного регистра 4 адреса, производя возврат к прерванной микропрограмме.

Таким образом, данное устройство позволяет осуществлять работу набора микропрограммы в сочетании с возможностью многоразрядной кодовой модификации адреса любой микрокоманды, а также режим работы с прерыванием, что значительно расширяет функциональные возможности устройства.

Указанные преимущества позволяют эффективно использовать устройство при построении управляющих процессоров, программы которых ориентированы на разветвленный логический

анализ и производить чтение кодограмм-ответов внешних устройств, используя их в качестве модифицируемых кодов адресов микрокоманд.

Формула изобретения

Микропрограммное устройство управления, содержагаее дешифратор, группа выходов которого соединена с группой адресных входов шифратора и является группой адресных выходов устройства, группа выходов шифратора соединена с первой группой входов блока элементов ИЛИ, вторая группа входов которого является первой группой входов устройства, группа входов дешифг ратора соединена с группой разрядных выходов регистра адреса, группа информационных входов которого соеди нена с группой разрядных выходов дополнительного регистра адреса, отличающееся тем, что, с целью расширения функциональных возможностей за счет осуществления режима работы с прерыванием, в него введены коммутатор, регистр прерываний, элементы И,НЕ, причем группа входов регистра прерываний соедине- . на с группой выходов блока элемен-

тов ИЛИ и с первой группой входов коммутатора, вторая группа входов которого соединена с группой разрядных выходов регистра прерываний, .вход которого соединен с выходом - элемента И, .первый вход которого соединен с выходом дешифратора, с первым входом коммутатора и через элемент НЕ со вторым входом коммутатора, второй вход элемента И соеди- нен с первым входом синхронизации устройства, второй и третий входы . синхронизации которого соединены соответственно с входами синхронизации дополнительного регистра адре. са и регистра адреса, входы прерывания которых соединены с входом прерывания устройства и с третьим входом элемента И, группа ВБКОДОВ коммутатора соединена с группой ин-формационных входов дополнительного 0 регистра адреса, группа информационных входов шифратора соединена со . второй группой входов устройства.

.Источники информации, принятые во внимание при экспертизе 5 1.Авторское свидетельство СССР № 416696, кл. G 06 .F 9/16, 1974. 2.Авторское свид:(етельство СССР по заявке № 2672630/18-24, кл. G 06 F 9/0.0, 1978 (прототип).

(О JS

V-H

nd

Х, ям 1

л/

F5r

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

| Микропрограммное устройство управления с контролем | 1983 |

|

SU1136162A1 |

| Устройство для программного управления и контроля | 1985 |

|

SU1280574A1 |

| Сбоеустойчивое микропрограммное устройство управления | 1982 |

|

SU1101823A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Микропрограммное устройство управления с контролем | 1985 |

|

SU1267414A1 |

| Микропрограммное устройство для приоритетного обслуживания группы абонентов | 1984 |

|

SU1302277A1 |

| Микропрограммное устройство для ввода-вывода информации | 1983 |

|

SU1144099A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

u-J.-J

-7 -

ЙОfto

Авторы

Даты

1981-01-23—Публикация

1978-10-09—Подача