Изобретение относится к вычислительной технике.

Известны запоминающие устройства (ЗУ) , содержащие ферритовые матрицы с раздельными проводами считывания и записи, устройство управления выборкой координатных проводов ферритовых матриц, блок местного управления, ус тройство считывания и записи информации,в которых разрядные провода подключены к разрядным формирователям

ИНаиболее близким техническим решением к предлагаемому является ЗУ, содержащее матричный накопитель, разряд ные шины которого через первые элементы согласования подключены к источнику питания, инвертор, вторые элементы согласования, информационные шины, управляющую шину и шину ну.пево.г потенциала 2.

Однако известные ЗУ содержат большое количество разрядных формирователей, сложных по построению, и харак теризуются большим потреблением мощности при записи информации.

цель изобретения -упрощение устройства и уменьшение потребляемой мощности.

Поставленная цель достигается тем что в известное устройство введены формирователь и группы ключей, выполвенные на. транзисторах, причем коллекторы транзисторов ключей первой группы подключены к одним из концов разрядных шин, другие концы которых , подключены к. коллекторам транзисторов ключей второй группы, через развязывающие диоды - к эмиттерам одних из транзисторов ключей первой и второй групп, а через вторые элементы согласования - к шине нулевого потенциала, эмиттеры других транзисторов ключей первой и второй групп подключены через развязывающие диоды к выходу формирователя, вход которого подключен к управляющей шине, базы транзисторов ключей первой и второй групп подключены через инверторы к информационным шинам, а -через согласующие резисторы - к источнику питания.

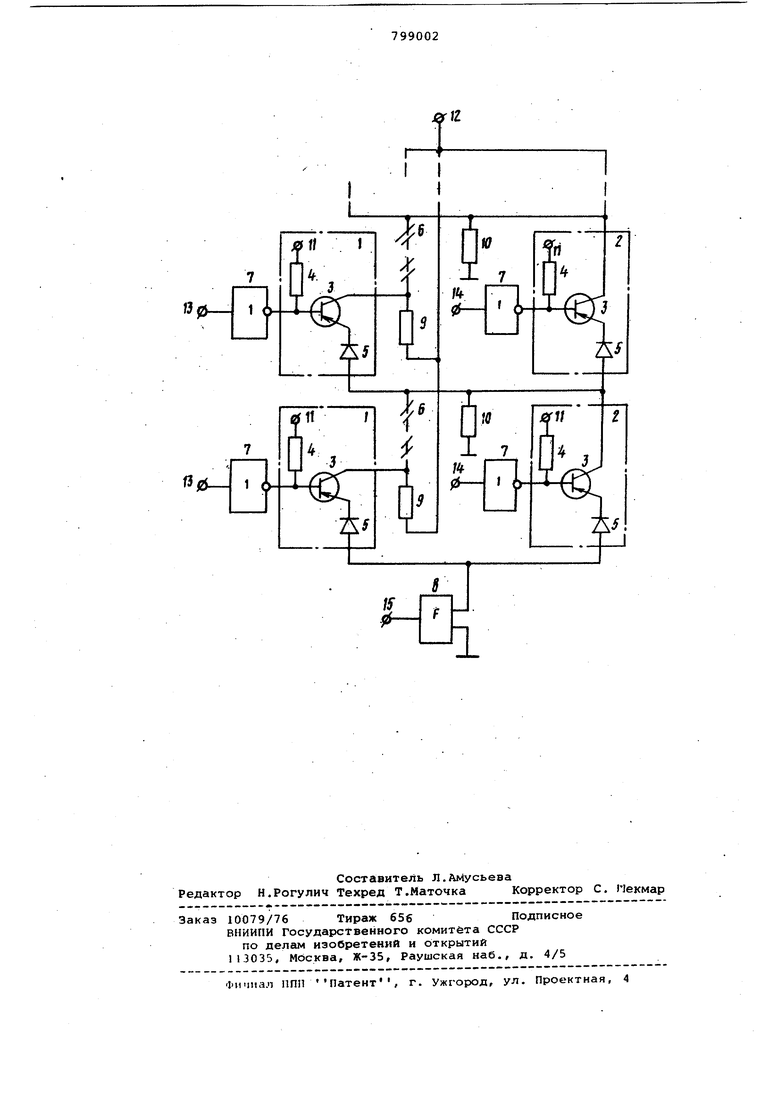

На чертеже представлена схема ЗУ.

Устройство содержит ключи 1 и 2, выполненные на транзисторах 3, в цепи базы которого включен резистор 4, а в цепи эмиттера - развязывающий диод 5, разрядные шины 6, инверторы 7, формирователь 8, согласующие резисторы 9 и 10, клеммы 11-15. Клеммы 11 и 12 служат для подклюнйя питающих напряжений, клеммы 13 и 14 - для подключения, соответствен но, прямых и инверсных выходов регис ра, числа устройства считывания и записи информации, клемма 15 - для подключения входа формирователя 8 к одному из выходов блока местного управления ЗУ.При появлении на клеммах 13 потенциалов,соответствующих прямо коду записываемого слова,и на клем.мах 14 потенциалов, соответствующих обратному коду записываемого слова, подготавливаются к срабатыванию ключ 1 и 2. С приходом на клемму 15 из блока местного управления (на чертеже не показан) сигнала запуска формирователя срабатывает формирователь 8, формируя импульс тока записи. Импульс тока записи проходит последова тельно через ключи 1, 2 и разрядные шины 6 к клемме 11. При эт.ом импульс тока записи проходит через те разряд ные шины б, ключи 1 которых открыты потенциалами на клеммах 13, и через те ключи 2, которые открыты потенциа лами на клеммах 14, минуя параллельн подключенные к ним закрытые ключи 1 с подключенными к ним разрядными шин Mif 3. Формирователь 8 либо построен по схеме для работы в линейном режиме или по схеме для работы в ключевом режиме. В последнем случае в коллекторные цепи ключей 2 подключают урав нивающие резисторы. Замена разрядных формирователей ключами в ЗУчуменьшает количество разрядных формирователей,довольно сложных по построению, особенно в тех случаях, когда от них требуется работа в линейном режиме с целью стабилизации тока. Включение разрядных шин в последо вательную цепь снижает TOKonoTpe6jje ние запоминающим устройством в несколько раз, что особенно важно для ЗУ малой емкости. Формула изобретения Запоминающее устройство, содержащее матричный накопитель, разрядные шины которого через первые элементы согласования подключены к источнику питания, инверторы, вторые элементы согласования, информационные шины, управляющую ишну и шину нулевого потенциала, о т л и.ч аю ще е с я тем, что, с целью упрощения устройства и уменьшения потребляемой мощности, в него введены формирователь и группы ключей, выполненные на транзисторах, причем коллекторы транзисторов ключей первой группы подключены к одним из концов.paзpяДj ных шин, другие концы которых подключены непосредственно к коллекторе транзисторов ключей второй группы, через развязывающие диоды - к эмиттерам одних из транзисторов ключей первой и второй групп, а через вторые элементы согласования - к шине нулевого потенциала, эмиттеры других транзисторов ключей первой и второй групп подключены через развязывающие диоды к выходу формирователя, вход которого подключен к управляющей шине, Транзисторов ключей первой и второй групп подключены через инверторы к информационным шинам, а через согласующие резисторы к источнику питания. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 498647, кл. QU С 11/06, 12.06.74. 2.Шигин А.Г., Дерюгин А.А.Цифровые вычислительные машины. М. , Энергия 1975, с. 98. § 4-4 (прототип),

00-Н

Г301

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1985 |

|

SU1269208A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ | 1972 |

|

SU434481A1 |

| Запоминающее устройство | 1981 |

|

SU959165A1 |

| Запоминающее устройство | 1976 |

|

SU613405A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| Устройство для обращения к памяти (его варианты) | 1982 |

|

SU1092561A1 |

| Оптоэлектронный модуль для обработки изображений | 1985 |

|

SU1283963A1 |

| Полупостоянное запоминающее устройство с электрической перезаписью информации | 1983 |

|

SU1088068A1 |

| Усилитель записи-считывания | 1986 |

|

SU1437913A1 |

| Матричный накопитель | 1979 |

|

SU799007A1 |

Авторы

Даты

1981-01-23—Публикация

1979-01-08—Подача