1

Изобретение .относится к эалоътнающим устройствам.

Известно устройство для контроля блока постоянной памяти, которое содержит блок управления, подключенный к счетчику адреса, связанному с блоком индикации адреса и проверяемым блоком постоянной памяти (БПП), сумматор, входы которого соединены с выходами поверяемого блока и блока управления, выходы - со входом схемы сравнения, вЪ1ход которой подключен к блоку управления.

В этом устройстве операция суммирования считанной с БПП информации осуществляется за время нескольких рабочих обращений к одному адресу с использованием информации, выведенной за одно обращение 1.

Недостатком устройства является невозможность контроля достоверности считывания информации второго и последующих обращений к одному адресу проверяемого БПП при неустойчивом считывании.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство для контрсля постоянного запоминающего блока, содержащее регистр числа, выходы которого

подключены к одним входам схемы сравнения, вторые входы которой подсоединены к выходам БПП, а выход - к блоку управления, подсоединенного к

счетчику адресов, подключеннсн гу ко входам ПЗБ и блок вентилей, информационные входы которого подключены к другим входам схемл сравнения, управляющие входы объединены и подключены к блоку управления, а выходи подключены ко входам резтистра числа 2. Однако это устройство, условно принимая информацию, считываемую с проверяемого БПП в первом обращении

по адресу, за эталонную, не обеспечивает контроля достоверности считанной информации из ЕПП в первом обргидении .

Цель изобретения - повышение достоверности контроля считанной информации .

Поставленная цель достигается тем, что в устройство для контроля блока постоянной памяти, содержащее счетчик, регистр числа, первую схему сравнения, элементы И и блок управления, I причем выходы регистра числа подключены к одним из йходов первой сх®« сравнения, другие входы которой сое-,

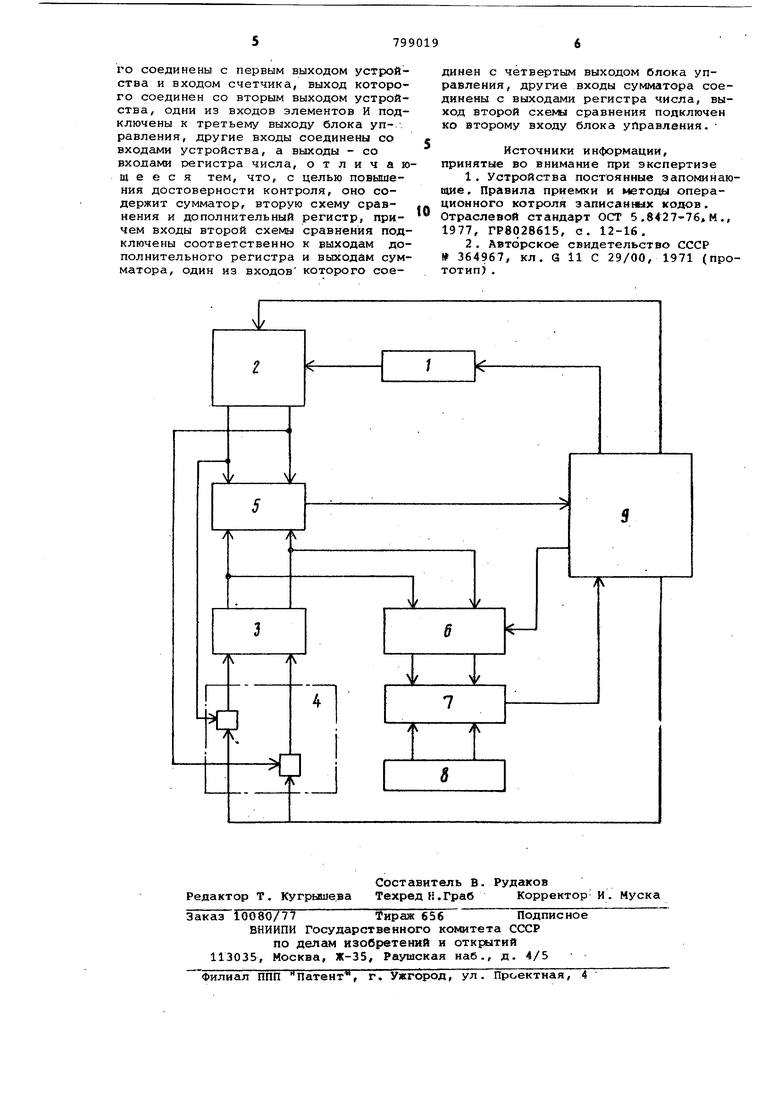

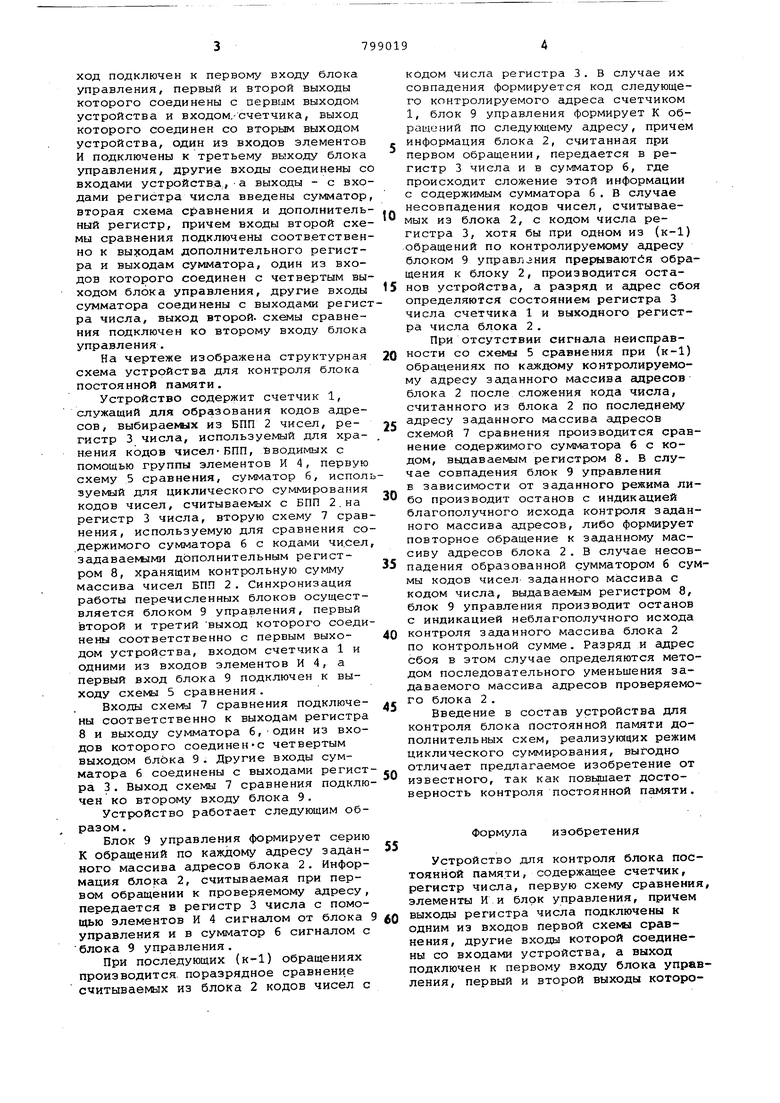

динены со входами устройства, а выход подключен к первому входу блока управления, первый и второй выходы которого соединены с первым выходом устройства и входом,-счетчика, выход которого соединен со вторым выходом устройства, один из входов элементов И подключены к третьему выходу блока управления, другие входы соединены с входами устройства,а выходы - с вхо дами регистра числа введены сумматор вторая схема сравнения и дополнитель ный регистр, причем входы второй схе мы сравнения подключены соответствен но к выводам дополнительного регистра и выходам сумматора, один из входов которого соединен с четвертым вы ходом блока управления, другие входы сумматора соединены с выходами регис ра числа, выход второй- схемы сравнения подключен ко второму входу блока управления. На чертеже изображена структурная схема устройства для контроля блока постоянной памяти. Устройство содержит счетчик 1, служащий для образования кодов адресов, выбираемых из БПП 2 чисел, регистр 3 числа, используемый для хранения кодов чисел-БПП, вводимых с помощью группы элементов И 4, первую схему 5 сравнения, сумматор 6, испол зуемый для циклического суммирования кодов чисел, считываемых с БПП 2.на регистр 3 числа, вторую схему 7 срав нения, используемую для сравнения со держимого сумматора 6 с кодами чисел задаваемыми дополнительным регистром 8, хранящим контрольную сумму массива чисел БПП 2. Синхронизация работы перечисленных блоков осуществляется блоком 9 управления, первый второй и третий выход которого соеди нены соответственно с первым выходом устройства, входом счетчика 1 и одними из входов элементов И 4, а первый вход блока 9 подключен к выходу схемы 5 сравнения. Входы схемы 7 сравнения подключены соответственно к выходам регистра 8 и выходу сумматора 6,-один из входов которого соединение четвертым выходом блока 9. Другие входы сумматора б соединены с выходами регист ра 3, Выход схемы 7 сравнения подклю чен ко второму входу блока 9. Устройство работает следующим образом , Блок 9 управления формирует серию К обращений по каждому адресу заданного массива адресов блока 2. Информация блока 2, считываемая при первом обращении к проверяемому адресу, передается в регистр 3 числа с помощью элементов И 4 сигналом от блока 9 управления и в сумматор 6 сигналом с блока 9 управления. При последующих (к-) обращениях производится, поразрядное сравнение считываемых из блока 2 кодов чисел с кодом числа регистра 3. В случае их совпадения формируется код следующего контролируемого адреса счетчиком 1, блок 9 управления формирует К обращений по следующему адресу, причем информация блока 2, считанная при первом обращении, передается в регистр 3 числа и в сумматор б, где происходит сложение этой информации с содержимым сумматора б, В случае несовпадения кодов чисел, считываемых из блока 2, с кодом числа регистра 3, хотя бы при одном из (к-1) обращений по контролируемому адресу блоком 9 управления прерываются обращения к блоку 2, производится останов устройства, а разряд и адрес сбоя определяются состоянием регистра 3 числа счетчика 1 и выходного регистра числа блока 2 . При отсутствии сигнала неисправности со схемы 5 сравнения при (к-1) обращениях по каждому контролируемому адресу заданного массива адресов блока 2 после сложения кода числа, считанного из блока 2 по последнему адресу заданного массива адресов схемой 7 сравнения производится сравнение содержимого сумматора 6 с кодом, выдаваемым регистром 8. В случае совпадения блок 9 управления в зависимости от заданного режима либо производит останов с индикацией благополучного исхода контроля заданного массива адресов, либо формирует повторное обращение к заданному массиву адресов блока 2 . В случае несовпадения образованной сумматором 6 суммы кодов чисел- заданного массива с кодом числа, выдаваемым регистром 8, блок 9 управления производит останов с индикацией неблагополучного исхода контроля заданного массива блока 2 по контрольной сумме. Разряд и адрес сбоя в этом случае определяются методом последовательного уменьшения задаваемого массива адресов проверяемого блока 2 . Введение в состав устройства для контроля блока постоянной памяти дополнительных схем, реализукяцих режим циклического суммирования, выгодно отличает предлагаемое изобретение от известного, так как повьпаает достоверность контроля постоянной па «1яти. Формула изобретения Устройство для контроля блока постоянной памяти, содержащее счетчик, регистр числа, первую схему сравнения, элементы И и блок управления, причем выходы регистра числа подключены к одним из входов первой схемы сравнения, другие входы которой соединены со входами устройства, а выход подключен к первому входу блока управления, первый и второй выходы которо

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1977 |

|

SU714503A1 |

| Устройство для контроля памяти | 1979 |

|

SU783855A1 |

| Устройство для контроля блоков оперативной памяти | 1986 |

|

SU1358003A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU936036A1 |

| Устройство декодирования тональных сигналов | 1988 |

|

SU1570034A1 |

| Постоянное запоминающее устройство с самоконтролем | 1979 |

|

SU858118A1 |

| Устройство для контроля памяти | 1979 |

|

SU809395A1 |

| Устройство для контроля блоковпОСТОяННОй пАМяТи | 1979 |

|

SU809399A1 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

Авторы

Даты

1981-01-23—Публикация

1979-04-10—Подача