1

Изобретение относится к запоминающим устройствам .

Известно устройство для контроля памяти, которое содержит кодовый преобразователь, обрабатывающий контролный разряд и размещенный в системе передачи данных между процессором и запоминающим устройством 1

Недостатком этого устройства является то, что его затрудиительяо применять в двунаправлеиных системах передачи данных,.

Наиболее близким по технической сущности к предлагаемому изобретению является устройство, содержащее регистр, мультиплексор данных, схеглу свертки и шинные формирователи 21.

Недостатком этого устройства является то, что при его испольэоваиия с двунаправленными шинами значительно увеличивается оборудование (возрастает количество регистров и схем сверток), что приводит к снижению достоверности передачи информации, т.е. надежности устройства. Устройство также обладает ограниченным быстродействием, определяемым полным временем срабатывания многоразрядной свертки, которая должна срабатывать дважды при передаче по одно магистрали адреса и данных.

Цель изобретения - повышение быстрюдействия и надежности устройства.

Поставленная цель достигается тем, что.в устройство контроля памяти, содержащее регистр адреса, дв4 мультиплексора, две группы форкмрователей сигналов, блок управления, первый

триггер, первый блок свертки по модулю два и схему сравнения, п.ичем выход регистра адреса соединен с первым входом первого мультиплексора, выход которого подключен ко входу первого

блока свертки по модулю два и первым входам формирователей сигналов,- вхрд регистра адреса соединен со BTOJMJM входом первого мультиплексора н с одним из выходов фор1 в1рователей сигналов второй группы, другие выходы которых подключены к первому входу второго мультиплексора, второй входкоторого соединен с одним из выходов (ормиррвателей сигналов первой

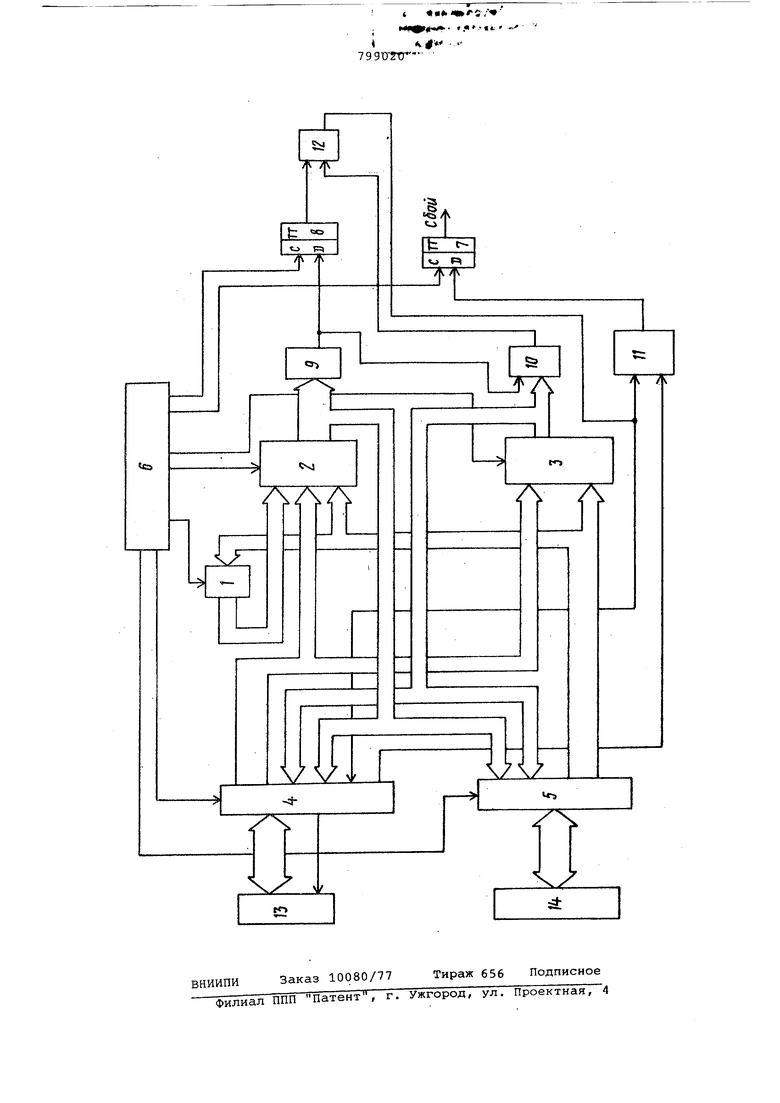

группы, другие выходы которых подключены к третьему входу первого мультиплексора, выход второго мультиппексора соединен со вторыми входили форкмрователей сигналов, третьи входы которых подключены к информационным и адресным входам устройства, первый и второй входы схемы сравнения соедг нены соответственно свыходом и первым входом одного из формирователей сигналов первой группы, второй вход которого подключен ко входу устройст ва., выход схемы сравнения соединен с первым входом первого триггера, выхо которого подключен- к индикаторному выходу устройства, второй вход перв го триггера и управляющие входы регистра адреса, мультиплексоров и фор мирователей сигналов соединены с со ответствуквдими выходами блока управ ления, вёедены второй триггер, второй блок свертки по модулю два и по лусумматор, причем первый вход втор го блока свертки по модулю два подключен к выходам второго мультиплек сора, второй вход - к первому входу второго триггера и выходу первого блока свертки по модулю два, а выход к одному из входов полусумматора, другой вход которого соединен с выходом второго триггера, а выход - с вторым входом схеглы сравнения, втор ВХОД второго триггера подключен к соответствующему выходу блока управ ления . На чертеже изображена функциональ ная схема предлагаемого устройства. Устройство содержит регистр 1 адреса, первый 2 и второй 3 мультиплек соры, первую 4 и вторую 5 группы фор мирователей сигналов, блок б управления, первый триггер 7 и второй триггер 8, являющийся D-триггером,о первый 9 и второй 10 блоки свертки по модулю два, схему 11 сравнения и полусумматор 12. Выход регистра 1 адреса, содержащий п шин, соединен с первым входом первого мультиплексора 2, выход кото рого, содержащий п 1иин, подключен ко входу первого блока 9 свертки по модулю два и первым входам формировате лей сигналов групп 4 и 5. Вход регистра 1 адреса соединен со вторым входом, содержащим п шин, первого мультиплексора 2 и с одним из выходов формирователей 5 сигналов второй группы, другие выходы которых подключены к первому входу, содержащему m шин, второго мультиплексора 3, второй вход которого, содержащий m шин, соединен с одним из выходов формирователей сигналов первой группы 4, другие выходы которых подключены к третьему входу, содерЖсвдему п шин, первого мультиплексора 2. Выход второго мультиплексора 3 соединен со вторыми входами формирователей сигналов первой 4 и второй 5 групп, третьи входы которых, содер жащие п + m разрядов, подключены к информационным и адресным входам устройства. Первый и второй входы схемы 11 сравнения соединены соответственно с выходом и первым входом одного из формирователей сигналов первой группы 4, второй вход которого подключен ко входу устройства. Выход схемы 11 сравнения соединен с первым входом первого триггера 7, выход которого подключен к индикаторному входу устройства . Второй вход первого триггера 7 и управляющие входы регистра 1 адреса, мультиплексоров 2 и 3 и формирователей сигналов первой 4 и второй 5 групп соединены с соответствующими выходами блока 6 управления, . Первый вход второго блока 10 свертки по модулю два подключен к выходам второго мультиплексора 3, второй вход - к первому входу второго триггера 8 и выходу первого блока 9 свертки по модулю два, а выход - к одному из входов полусумматора 12, друной вход которого соединен с выходом второго триггера 8, а выход - с вторым входом схемы 11 сравнения. Второй вход второгс триггера 8 подключен к соответствующему выходу блока б управления, являющегося микропрограммным. Контролируемое запоминакхцее устройство и блок 14 микропроцессоров подключены двунаправленными щинами к адресным и информационным входам. устройства. Устройство работает следующим образом. Предлагаемое устройство для конт-роля памяти позволяет выполнить контроль передачи информации запоминающего устройства в двух режимах: в режиме считывания информации из запоминающего устройства и в режиме записи информации в запоминающее устройство. В режиме считывания п-разрядный адрес, сформированный в блоке 14 микропроцессоров через формирователи 5 второй группы, управляемые микропрограммным устройством 6 управления, запоминается на регистре 1 адреса. С выхода регистра 1 адреса через первый мультиплексор 2 и формирователи 4 сигналов первой группы адрес поступает в запоминающее устройство 13. С выхода мультиплексора 2 п-разрядные адреса поступают также на первый блок 9 свертки по модулю два,и результат свертки запоминается на втором триггере 8. По соответствующему, адресу из контролируемого запоминающего устройства 13 через формирователи 4 сигналов первой группы, п разрядов информации поступает через мультиплексор 2 на первый блок 9 свертки по модулю два и m разрядов информации поступает через второй мультиплексор 3 на второй блок 10 свертки по модулю два, в последнюю . ступень которого поступает результа с выхода первого блока 9 свертки помодулю два . На выходе полусумматора 12 получается контрольный разряд как результат свертки информации, считанной из запоминающего устройства и поступающей с блока 10, и адреса, запомненного в триггер 8 в предыдущем такте. На выходе схемы 11 сравнения получается результат сравнения контрольного разряда, считанного с запоминающего устройства 13 через один из формирователей 4 сигналов первой группы и контрольного разряда с выхода полусумматора 12. Результат сравнения запоминается в триггере 7, управляемом микропрограммным устройством 6 управления, а на выходе триггера 7 (индикаторном выходе устройства) формируется сигнал Сбой.

Во втором режиме (записи) п-разрядный адрес и информация, сформированные в блоке 14 микропроцессоров, поступают, как и в первом режиме, через формирователи 5 сигналов второй группы, регистр 1 адреса, первый мултиплексор 2 и формирователи 4 сигналов второй группы, в контролируемое запс 1ииающее устройство 13.

С выхода мультиплексора 2 п разрядов адреса и п разрядов информации поступает на вход блока 9 и результа свертки гщреса запоминается на триггере 8, а m разрядов информации, сформированной в блоке 14 микропроцессоров, поступает через формирователи 5 сигналов второй группы и второй мультиплексор 3 на второй блок 10 св.ертки по модулю два,в последнюю ступень которого подается результат свертки с выхода блока 9.

На выходе полусумматора 12 формируется контрольный разряд как результат свертки по модулю два информации, поступившей из блока 14 микропроцессоров, и адреса, запомненного в триггере 8 в предыдущем такте. Это контрольный разряд с выхода полусумматора 12 вместе с п разрядами информации , поступающими с выхода первого мультиплексора 2, и m разрядами информации, поступаю1ди1 1И с выхода второго мультиплексора 3, подаются через формирователи 4 первой группы на запись в контролируемое запоминающее устройство 13.

Технико-экономические преимуществ предлагаемого устройства заключаются в повышении его быстродействия и надежности при обеспечении возможности работы с двунаправленными шинами.

Формула изобретения

Устройство для контроля памяти, содержащее регистр адреса, два мультиплексора, две группы формирователей сигналов, блок управления, первый триггер, первый блок свертки по модулю два и схему сравнения, причал выход регистра адреса соединен с первым входом первого мультиплексора, выход которого подключен ко входу первого блока свертки,по модулю два и первым входам формирователей сигналов, вход регистра адреса соединен со вторым входом первого мультиплексора и с одним из выходов формирователей сигналов второй групгол, другие выходы которых подключены к первому входу второго мультиплексора, второй вход которого соединен с одним из

5 выходов формирователей сигналов первой группы, другие выходы которых подключены к третьему входу первого мультиплексора, выход второго мульт.иплексора соединен со вторыми входами

Q формирователей сигналов, трютьи входы которых подключены к информационным и алресньгм входам устройства, первый и второй входы схемы сравнения соединены соответственно с выходом и первым входом одного из форми5рователей сигналов первой группы, второй вход которого подключен ко входу устройства, выход схемы сравнения соединен с первым входом первого триггера, выход которого подклю0чен к индикаторному выходу устройства, второй вход первого триггера, и управляющие входы регистра адреса. Мультиплексоров и формирователей сигналов соединены с соответствую5щими выходами блока управления, о тл и ч а ю щ е е с я тем, что, с целью повышения быстродействия и надежности устройства, оно содержит второй триггер, второй блок свертки

0 по модулю два и полусумматор, причем первый вход второго блока свертки по модулю два подключен к выходам второго мультиплексора, второй вход к первому входу второго триггера и выходу первого блока свертки по мо5дулю два, а выход - к одному из входов полусумматора, другой вх д которого соединен с выходом второго триггера, а выход - с вторым входом схемы сравнения, второй вход второго

0 триггера подключен к соответствующему выходу блока управления.

Источники информации, принятые во внимание при экспертизе

1.Заявка Японии № 52-647,

кл. 97 (7) С 01, опублик. 10.01.77.

2.Заявка Японии № 52-26663, кл. 97 (7) G 11, опублик. 15.07.77

(npOTi. ГИП) .

.

79gicr tr

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Устройство для цифровой магнитной записи | 1989 |

|

SU1647634A2 |

| Программируемая линия задержки | 1990 |

|

SU1723656A1 |

| Сигнатурный анализатор | 1986 |

|

SU1386995A1 |

| Устройство для контроля и диагностирования цифровых узлов | 1989 |

|

SU1755207A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1700558A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для контроля микропроцессорной системы | 1987 |

|

SU1474650A2 |

| Многопроцессорная система | 1989 |

|

SU1686455A1 |

Авторы

Даты

1981-01-23—Публикация

1979-04-11—Подача