1

Изобретение относится к области вычислительной техники и может быть использовано при конструировании и разработке цифровых интегрирующих .машин (ЦИМ) .параллельнопоследовательного типа.

В -последовательных цифровых интеграторах, параллельных ЦИМ с многоразрядными прира1ден.ия1ми, обычно применяется алгоритм умножения младшими разрядами вперед. Особенностью этого метода является то, что образование каждого последующего приращения интеграла возможно только после окончания процедуры перемножения текущего значения подынтегральной функции на приращение аргумента.

При организации наиболее экономичной структуры электронной коммутации решающих |блоков используется для передачи приращений всего один информационный канал. В этом случае значительно увеличивается общее время вычислений из-за того, что в момент передачи Приращений процесс интегрирования должен -прерываться.

Для устранения этого недостатка цифровых интеграторов последовательного типа можно применить алгоритм умножения на одиН , начиная со старших, что-позволяет фор-мировать старшие разряды лрнращений интеграла и передавать их в другие интеграторы Б процессе операции умножения.

не дожидаясь ее окончания. Однако использование такого алгоритма сокращает лишь то время, которое отводится для -коммутации решающих блоков, но не ускоряет сам процесс

вычислений.

Цель изобретения - сокращение времени вычислений в -последовательном цнфровом интеграторе, предназначенном для ЦИМ параллельного-типа, использующей однокаиальиую

электронную коммутацию решающих блоко. Это достигается путем использования алгоритма умножения одновременно на два разряда, начиная со старших, и такой организации структуры выходного устройства, которая

позволяет кодировать и передавать между иитеграторами -по одному информационному каналу образующиеся в -процессе умнол ения пары разрядов приращения и коды -коррекции в переданные старшие разряды без прерывания процесса вычислений.

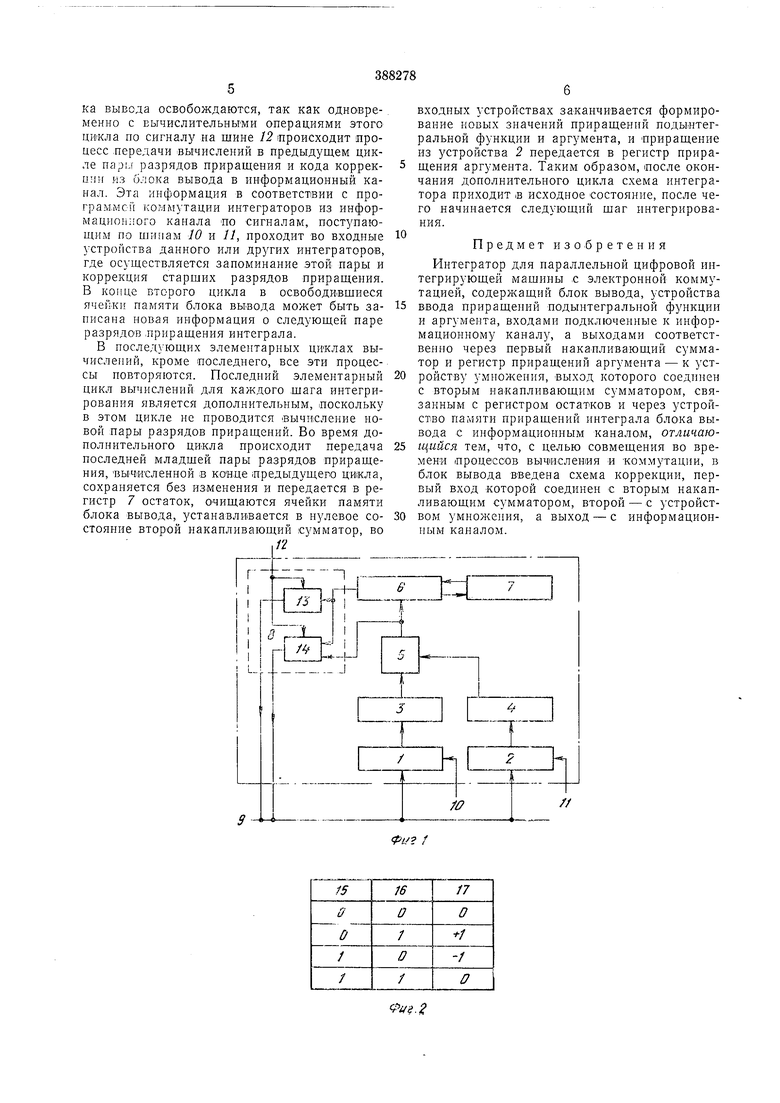

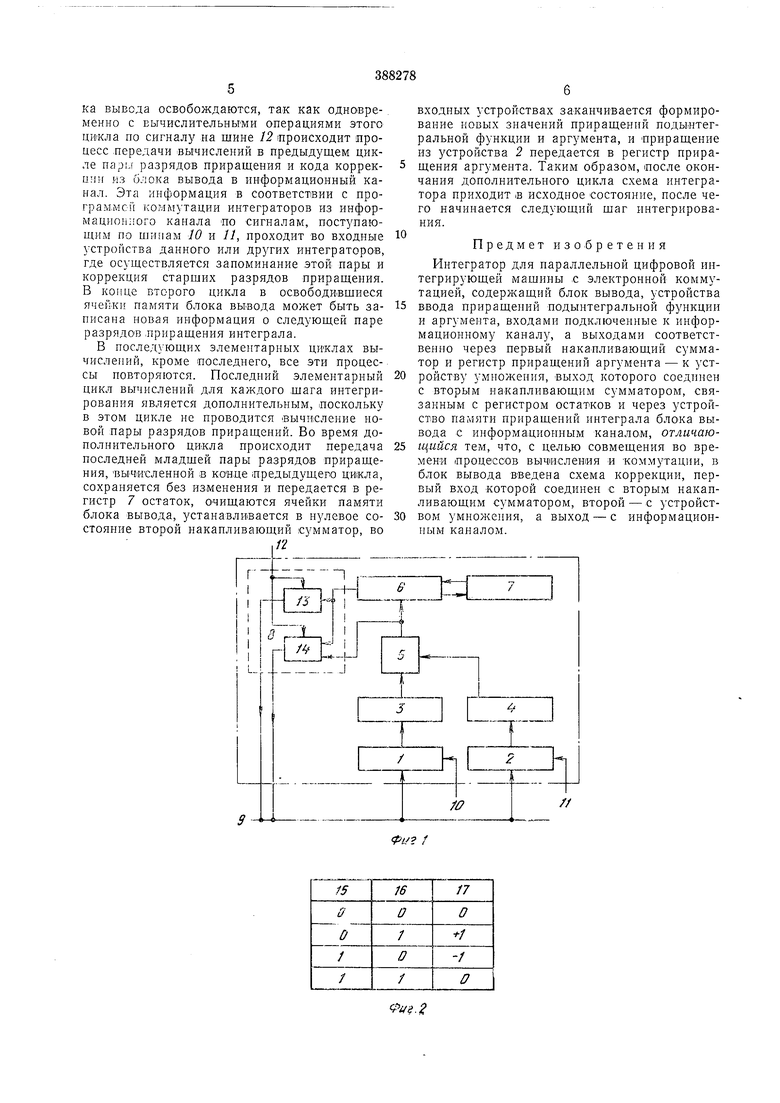

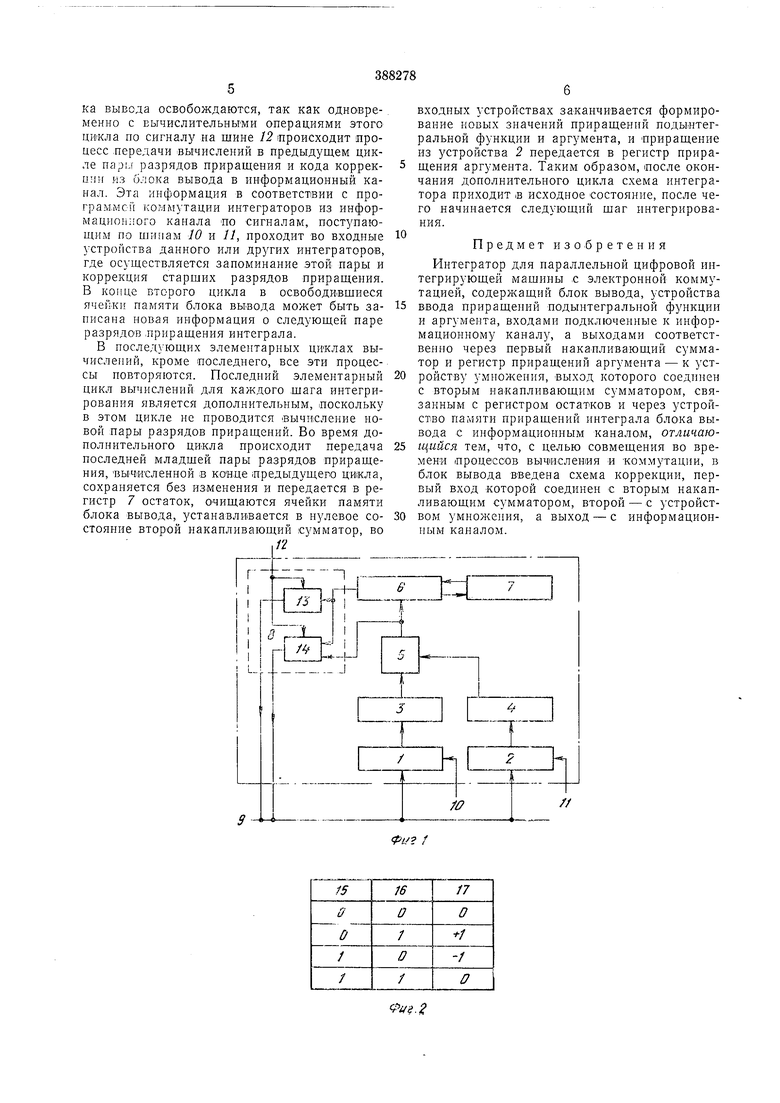

На фиг. 1 показана функциональная схема такого интегратора; на фиг, 2 - таблица возможных значений кода коррекции старщих разрядов приращений.

Предлагаемый интегратор содержит устройства ввода 1пр-нращений подынтегральной функции / и аргумента 2, иервый накапливающий сумматор 3, регистр 4 приращений аргумента, устройство 5 умножения, второй

накапливающий сумматор 6, реги-стр 7 остатKOiB, блок 8 вывода. Интегратор подключен к информационному каналу 9. Устройства /, 2 и блок 8 управляются сигналами, поступающими по шинам 10, 11 и 12 из устройства управления ЦИМ. Устройства / и 2 осуществляют прием пар разрядов приращений подыитегральной функции и аргумента, коррекцию лрннятых величин и формирование из нпх кодов приращений. Выход устройства 1 связан с первым сум.матором 3, в котором накалливаются и хранятся текущие значения подынтегральной 4)ункцин. Выход устройства 2 соединен с входом регистра 4, где хранится код приращения аргумента. Этот код выдается в устройство 5 умножения парами разрядов, начиная со старщих. Устройство умножения Предназначено для получения частичных произведений путем умножения значения -подынтегральной функции, поступающего из первого накапливающего сумматора, на пары разрядов приращения аргумента в соответствии с алгоритмом умножения на два старщих разряда. Выход устройства умножения соединен с входом второго сумматора 6, в котором происходит накоплекие суммы частичных произведений. Из сумматора 6 пары знаковых разрядов каждой суммы частичпых произведений поступают в устройство 13 памяти, а разряд, содержащий возможный неренос из знаковых разрядов, - в схему 14 коррекции, в которой он запоминается. Схема коррекции запоминает также знак частичного произведения, приходящий с выхода устройства умножения. Схема коррекЦИК помимо функции запоминания формирует также код коррекции в соответствии с таблицей, показанной на фиг. 2. Ио сигналу, поступающему по щине 12, содержимое устройства памяти и код коррекции из схемы коррекции выдаются в информациоиный канал 9. Со вторым накапливающим сумматором связан регистр, который хранит значение остатков, получаемых so втором накапливающем сумматоре, и выдает в иего лары разрядов остатка, начиная со старщих. В таблице, изображенной на фиг. 2, в столбцах 15, 16 приведены возможные комбинации знака частичных произведений, получаемых на выходе устройства умножения (столбец /5), и переноса из знаковых разрядов сумм на выходе второго накапливающего сумматора (столбец 16). В столбце 17 показан код коррекции переданных старщих разрядов приращения. Этот код принимать три значения +1; 0; -1. Работает интегратор так, что вычисление приращения иитеграла и передача этого приращения в другие интеграторы совмещены во времени. Это достигается лутем такой организации вычислительного процесса, когда получение полного значения приращения интеграла осуществляется за несколько циклов, в каждом из которых определяется иовая пара разрядов приращения и одновременно передается в другие интеграторы пара, вычисленная в предыдущем цикле. В связи с этим под олным шагом интегрирования понимается процесс формирования и передачи всего многоразрядного приращения, а под элементарным циклом вычислений процесс формирования и передачи в другие решающие блоки пары разрядов и кода коррекции м огоразрядного приращения. К началу каждого шага нитегрнрования интегратор приходит в такое состояние, при котором со входном лстройстве 1 хранится приращение подынтегральной функции, в регистре 4 - приращение аргумента, в первом накапливающем сумматоре - предыдущее значение иодынтегралыюй функции, второй накапливающий сумматор и ячейки памяти блока вывода сброшены в нуль, а в регистре 7 хранится значение остатка. Этот остаток представляет собой те разряды произведения подынтегральной функции на все разряды приращения аргумента, которые остались после выделения из этого произведеиия всех разрядов приращения интеграла в предыдущем шаге интегрирования. В первом цикле в первом накапливающем сумматоре происходит суммирование предыдущего значения подынтегральной функции с прирап№н:ием, поступающим из устройства ввода приращения подынтегральной функции, и 1передача нового значения подынтегральной функции на устройство 5, где осуществляется умножение этой величины на два старших разряда приращения аргумента (в первом цикле это знаковые разряды), выдаваемых из регистра приращения аргумента. Полученное первое частичное произведение суммируется с содержимым второго накапливающего сумматора (в первом цикле это нуль). Два знаковых разряда получепной суммы представляют собой пару старшнх разрядов приращения, а в разряде, предшествующем знаковым, хранится возможный перенос из знаковых разрядов - информация для образования кода коррекции. Этн три разряда вместе со значением знака первого частичного произведеиия в самом коице первого цнкла записываются в ячейки памяти блока вывода, после чего содержимое второго накапливающего сумматора сдвигается на два разряда в сторону старщих, а в освободившиеся младшие разряды записывается пара старщих разрядов остатка из регистра остатков. На этом первый цикл заканчивается. Во втором цикле содержимое первого накапливающего сумматора не изменяется, и поэтому вычисленное в первом цикле значение нодынтегральиой функцин умножается в устройстве 5 иа следующую пару разрядов приращения аргумента, выдаваемую из регистра приращения аргумента. После этого выполняются остальные операпии, рассмотренные лри описании первого цикла. К концу второго цикла ячейки памяти бло

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой интегратор | 1975 |

|

SU650084A1 |

| ЦИФРОВОЙ ИНТЕГРАТОР | 1973 |

|

SU369590A1 |

| Цифровой интегратор | 1985 |

|

SU1365081A1 |

| Интегроарифметическое устройство | 1990 |

|

SU1784975A1 |

| Модуль интегрирующей вычислительной структуры | 1984 |

|

SU1257641A1 |

| Детерминированно-вероятностныйиНТЕгРАТОР | 1979 |

|

SU840859A1 |

| Решающий блок цифровой интегрирующей структуры | 1983 |

|

SU1104514A1 |

| Устройство для обработки чисел в избыточном последовательном коде | 1985 |

|

SU1330629A1 |

| Цифровой интегратор | 1979 |

|

SU903875A1 |

| Цифровой интегратор | 1982 |

|

SU1027725A1 |

Авторы

Даты

1973-01-01—Публикация