Изобретение относится к вычислительной технике и может быть иснользовано при разработке устройств, в которых используются процессоры с микропрограммнЬ)1м управлением.

Цель изобретения - повышение достоверности функционирования за счет оперативного обхода нежелательных участков микропрограммы.

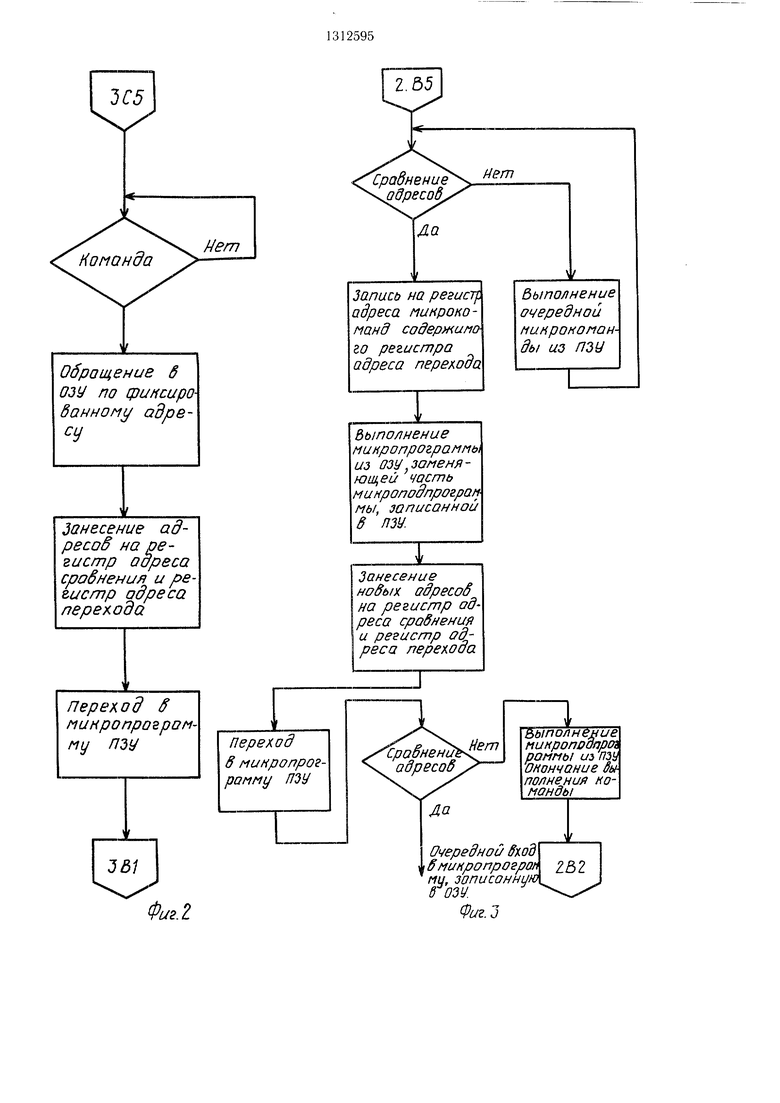

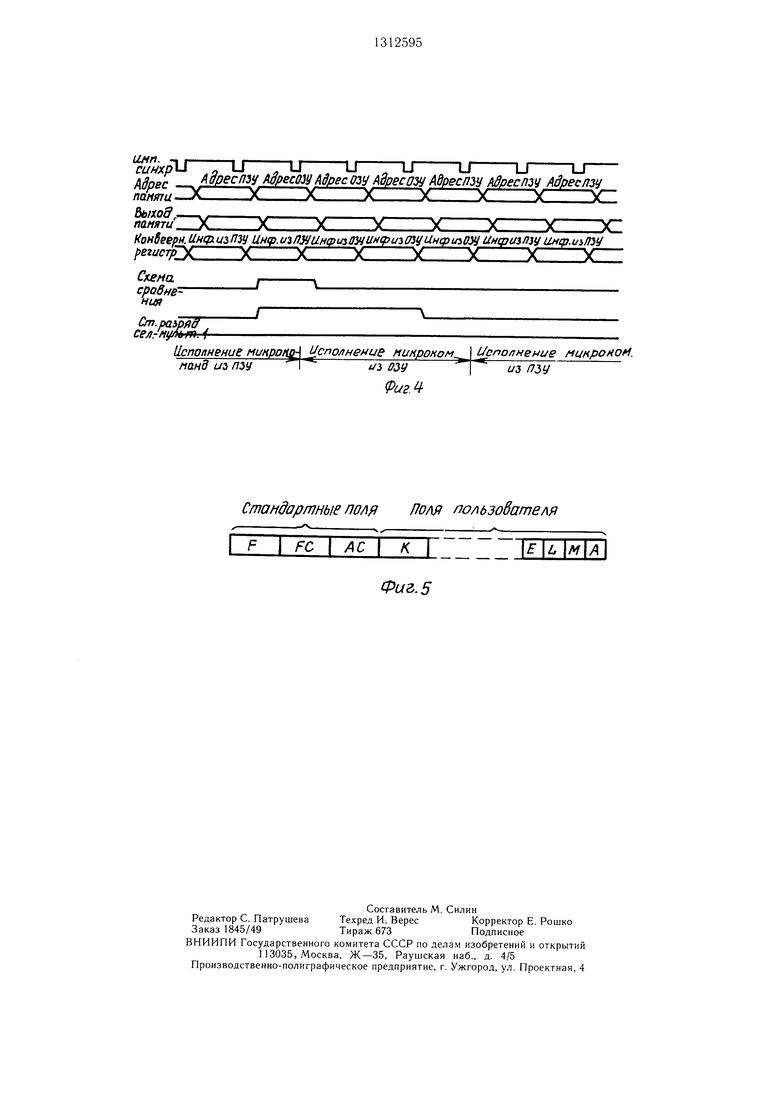

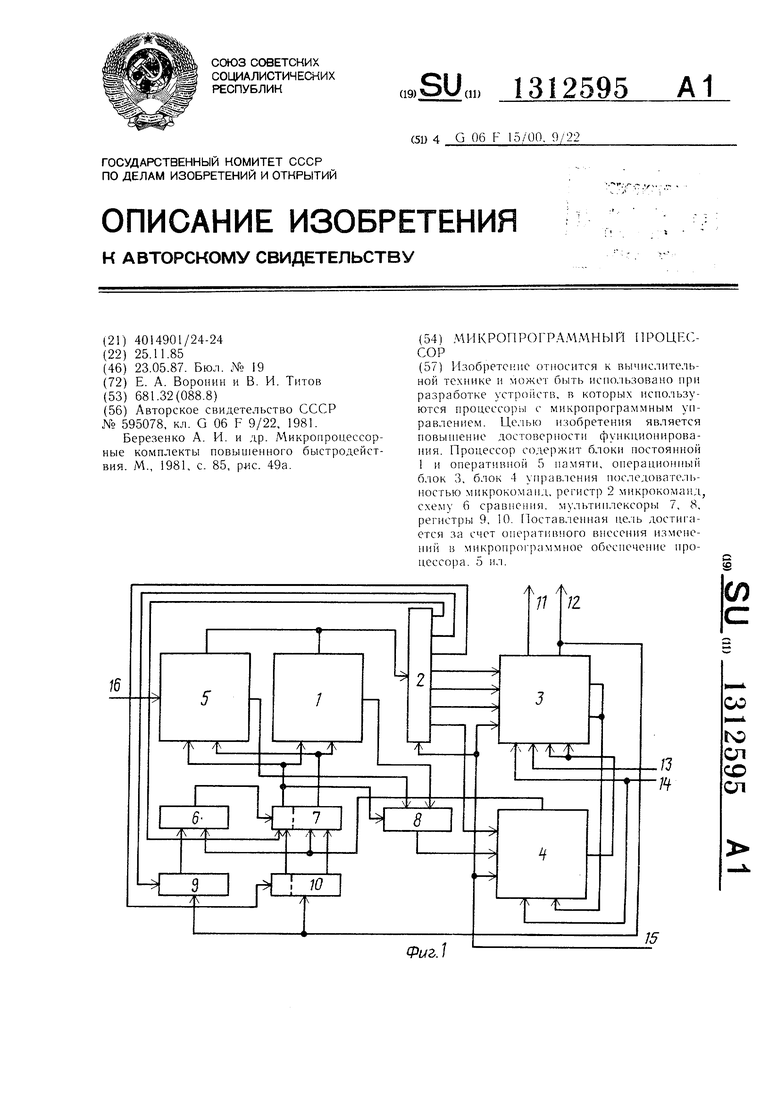

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 и 3 - алгоритмы работы устройства; на фиг. 4 - временная диаграмма работы устройства; на фиг. 5 - форма микрокоманды.

Устройство содержит блок 1 постоянной памяти, регистр 2 микрокоманд, операцион- ный блок 3, блок 4 управления последовательностью микрокоманд, блок 5 оперативной памяти, схему б сравнения, мультиплексоры 7 и 8, регистр 9 адреса сравнения, регистр 10 адреса перехода, адресный выход 11 процессора, информационный выход 12 про- цессора, входы информационный 13, кода операции 14, тактовых импульсов 15, начальной загрузки 16 процессора.

На фиг. 5 обозначено: F - поле микроопераций, подается на входы кода микроко- манды блока 3; FC - поле управления признаками, подается на входы управления признаками блока 4; АС - поле перехода, через мультиплексор подается на вход управления адресом следующей микрокоманды блока 4; К - поле маски, подается на вход маски блока 3; Е - разряд управления, разрешает выдачу информации из блока 3 на выход 12; L - разряд управления, разрешает занесение информации с выхода 12 на 10 регистр адреса перехода; М - разряд управления, разрешает занесение информа- ции с выхода 12 на регистр 9 адреса сравнения; А - разряд управления, определяет считывание информации либо из блока 1 постоянной памяти, либо из блока 5 оперативной памяти. Блоки 1 и 5 памяти могут переходить в состояние с высоким выходным сопротивлением.

Устройство работает следующим образом.

Микропрограмма работы устройства, записанная в блоке 1, состоит из микроподпрограмм выполнения отдельных команд, Начальный адрес каждой микроподпрограммы формируется блоком 4 как функция от кода команды, поступающего в этот блок с соответствующих разрядов входа 14. Перед началом работы устройства в блок 5 по фиксированным адресам записывается информа- ция, содержащая адреса микрокоманд, хранящихся в блоке 1, после формирования которых блоком 4 будет выполняться часть микроподпрограммы, записанная в блоке 5 и отсутствующая в блоке 1, начиная с адреса который записывается в фиксированные ячейки блока 5. Таким образом, каждой микроподпрограмме, хранящейся в блоке 1, соответствует записанный в фиксированную

ячейку блока 5 адрес первого выхода из этой микроподпрограммы (в процессе работы этот адрес записывается на регистр 9) и адрес первого входа в микропрограмму, записанную в блоке 5 (этот адрес записывается на регистр 10). В случае отсутствия изменений в микроподпрограмме, записанной в блоке 1, в фиксированную ячейку блока 5, соответствующую данной микроподпрограмме, записывается адрес, не существующий в блоках 1 и 5. Кроме того, в блок 5 записываются те части микронодпрограмм, которые отсутствуют в блоке 1, но должны выполняться в ходе исполнения команды.

Нри поступлении с входа 14 кода команды на входы блока 4 последний формирует на выходах адреса микрокоманды первый адрес микроподпрограммы выполнения поступившей команды, расположенной в блоке 1. Затем из блока 1 считывается микрокоманда, которая формирует в блоке 4 адрес фиксированной ячейки блока 5 и через мультиплексор 7 подает его на адресные входы памяти. Старший разряд мультиплексора 7, определяющий обращение к блокам 1 или 5, определяется в этом случае значением соответствующего разряда регистра 2. Занося в этот разряд «О или «1, можно считывать микрокоманды либо из блока 1, либо из блока 5. Затем происходит занесение первого адреса выхода из микроподпрограммы на регистр 9 и первого адреса заменяюп ей микропрограммы на регистр 10. Это занесение происходит в результате выполнения в блоке 3 микрокомаНх1Ы, по которой информация с соответствующих разрядов регистра 2 поступает на входы маски блока 3 и переписывается на выход 12. В этом случае вход маски используется для передачи константы, представляющей собой адрес памяти микрокоманд. Выдача информации из блока 3 на выход 12 управляется разрядом регистра 2, который подает соответствующее значение на вход разрешения информации блока 3. Содержимое соответствующих полей микрокоманды с регистра 2 поступает на управляющие входы регистра 9 и регистра 10, разрешая запись на них информации, находящейся на выходе 12. Затем путем изменения содержимого разряда регистра 2, определяющего считывание микрокоманды из блока 1 или из блока 5, происходит переход в микроподпрограмму выполнения команды, записанной в блоке 1. Старший разряд мультиплексора 7, являясь управляющим сигналом для мультиплексора 8, переключает на входы управления адресом следующей микрокоманды блока 1 соответствующие выходы либо блока 1, либо блока 5.

Микроподпрограмма выполнения команды из блока 1 исполняется до момента выдачи сигнала схемой 6 сравнения. Это произойдет в случае совпадения адреса, записанного на регистре 9, с адресом, сформированным блоком 4 на выходе управления

адресом следующей микрокоманды. Под воздействием сигнала со схемы 6 сравнения мультинлексор 7 подает на адресные входы блоков памяти содержимое регистра 10. Его старший разряд определяет обран1ение к блоку 5. Дальн1е происходит выборка и выполнение микрокоманд из блока 5, заменяющих часть микроподпрограммы выполнения команды, записаппой в блоке 1. Затем на регистр 9 заносится адрес следующего выхода из микроподпрограммы блока 1, а на регистр 10 заносится адрес очередной микропрограммы блока 5, заменяющей другую часть микроподпрограммы блока L В случае отсутствия изменений па регистр 9 заносится несуществующий адрес. Происходит переход к считыванию микрокоманд из блока 1 путем изменения содержимого соответствующего разряда регистра 2. Если в процессе даль- нейщего выполнения микроподпрограммы возникает сигнал сравнения, работа устройства происходит аналогично описанному. При отсутствии сравнения выполнение команды заканчивается и микропрограмма ожидает следующую команду.

Формула изобретения

Микропрограммный пропессор, содержащий блок постоянной памяти, операционный блок, блок управления последовательностью микрокоманд, регистр микрокоманд, причем выход кода микрооперации блока постоянной памяти подключен к информационному входу регистра микрокоманд, выходы кода операции и кода маски которого подключены соответственно к входу кода операции и к входу маски операционного блока, тактовый вход которого подключен к тактовому входу процессора и соединен с синхровходами регистра микрокоманд блока управления последовательностью микрокоманд, вход записи признаков перехода, вход признаков перехода и выход признаков перехода которого подключены соответственно к выходу кода управления признаками регистра микрокоманд, выходу и входу переноса и сдвига вправо операционного блока, первый информационный вход которого подключен к входу кода операции процессора и соединен с входом кода микрокоманды блока управления последовательностью мик- рокомапд, второй информационный вход операционного блока подключен к инфор0

мационному входу процессора, адресный и информационный выходы операционного блока подключены соответствеппо к адресному и информациопному выходам процоссора, отличающийся тем, что, с целью новы- 1нения достоверности функционирования, в него введены блок оперативной памяти, схема сравнения, два мультиплексора, регистр адреса сравнения и регистр адреса перехода, причем вход разрен1ения выдачи информации и информационный выход операционного блока подключены соответственно к выходу признака выдачи ипформации регистра микрокоманд и к информационным входам регистров адреса сравне1П1я и адреса

5 перехода, сипхровходы которых подключены соответственно к выходам первого и BTOpoi o признаков записи информации регистра микрокоманд, выход кода микрооперации блока оперативной памяти подключен к информационному входу регистра микрокоманд, выход признака типа блока памяти которого подключен к стар1нему разряду первого информационного входа первого мультиплексора, старший разряд второго информационного входа которого подключен

5 к старшему разряду выхода ре1 истра адреса перехода, младпше разряды выхо.та которого подключены к млад1ним 1)азрядам информационного входа первого му.чьтип.пек- сора, выход адреса микрокоманды блока управления последовательностью микроко0 манд подключен к первому входу схемы сравнения и к млад1ним разрядам первого информационного входа первого мультиплексора, старший разряд выхода первого мультигкпек- сора подк.чючеп к управляющему входу второго мультиплексора и к входам выборки

5 блоков постоянnoil и оперативной памяти, выходы кода управления адресом перехода которых подключены соответственно к первому и второму информациоп1Ц51м входам второго мультиплексора, выход которого подк.чючеп к входу управлеш1Я адресом перехода блока управления пос.чедователь- ностью микрокоманд, выход регистра адреса сравнения подключен к второму входу схемы сравнения, выход которой подключен к управляющему входу первого му.чьтип.тексора,

5 младшие разряды вхо.аа которого подключены к адресным входам блока постоянной намяти и блока оперативной намяти, информационный вход которого нодключен к входу начальной загрузки процессора.

Обращение 6 ОЗУ по финсиро- doHHOfiy одре- су

Занесение адресов на регистр адреса сробненил и регистр адреса лере)(,ода

Нет

t

быпалнение ачереднои мимранаман- ды из ПЗУ

L

Выполнение нинропрограммы из ОЗУjSQfieHfl- юш,ей часть минрападпраграп мы, записанной 8 ПЗУ.

Занесение нобых. одресоб на регистр адреса срабнения и регистр адреса перемда

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство управления | 1982 |

|

SU1156071A1 |

| Вычислительное устройство | 1987 |

|

SU1430962A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1134937A1 |

| Микропрограммное устройство управления | 1974 |

|

SU503240A1 |

| Микропрограммный процессор | 1974 |

|

SU535567A1 |

| Процессор | 1986 |

|

SU1332328A1 |

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммный процессор | 1978 |

|

SU765809A2 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство микропрограммного управления | 1984 |

|

SU1226453A1 |

Изобретение относится к вычислительной технике и может быть исио.пьзовано нри разработке ycTpoiicTB, в которых используются процессоры с микропрограммным управлением. Целью изобретения является повышение достовер1 ости функционирования. Процессор содержит блоки ностоянной 1 и оперативной 5 памяти, операционный блок 3, блок 4 управления нос.чедовате.пь- иостью микрокоманд, регистр 2 микрокома1 д схему 6 сравнения, мультиилексоры 7, 8, регистры 9, 10. Поставленная цель достигается за счет оперативного внесения изменений j микропро1-раммное обеспечение процессора. 5 ил. (О ,/3 / со to ел со ел

Пере)(од

8 минропрог- рапму ПУУ

выполнение HUKponoaapoi рампы из ПЗУ Онончоние ды- полиения ко- нанды

Фиг. 2

Очередной Swd бнинропрогро ми, зописанниг .

Фиг. J

HXD Г - ULJUиLj

л/УпоГ A Spec ПЗУ мресОЗУ Адрес 02У Адрес азу Адрес ПЗУ Адреспзу Афеспзу ларе с - г ..-.-сy-3LzVsr sr V

памяти -л-X-X-XXX, ХBbixoff - -панятид

Конбеерн. ungi из лзу Цндз. и- пУ1ин(ригау индзиг огдиндригОУ инсризпу имср. регистуЦXXУ УУХ

Ст. сел.-нумСтандартные noAf) Поля пользователя

F FC АС I К

Фиг. 5

| Суппорт токарного станка | 1976 |

|

SU595078A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Березенко А | |||

| И | |||

| и лр | |||

| Микропроцессорные комплекты повышенного быстродействия | |||

| М., 1981, с | |||

| Устройство для выпрямления опрокинувшихся на бок и затонувших у берега судов | 1922 |

|

SU85A1 |

| Способ смешанной растительной и животной проклейки бумаги | 1922 |

|

SU49A1 |

Авторы

Даты

1987-05-23—Публикация

1985-11-25—Подача