(54) УСТРОЙСТВО МИКРОПРОГРА/VlMHOrO УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1522203A1 |

| Микропрограммный процессор | 1980 |

|

SU947868A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для управления каналами | 1979 |

|

SU877519A1 |

| Процессор | 1984 |

|

SU1246108A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство микропрограммногоупРАВлЕНия | 1979 |

|

SU811253A1 |

| Устройство для контроля | 1981 |

|

SU1072052A1 |

I

Устройство микропрогаммного управления со страничной организацией памяти относится к вычислительной технике, в частности, к цифровым вычислительным машинам с микропрограммным управлением.

Известно устройство микропрограммного управления со стековой памятью, в котором стековая память обеспечивает запоминание адресов возврата 1.

Недостатком данного устройства является большой объем оборудования.

Наиболее близким к предлагаемому является устройство микропрограммного управления программоуправляемой электронной лавишной вычислительной машины «Искра-125, содержащее ПЗУ, регистр микрокоманд, счетчик адреса, регистр страниц, блок выполнения микрокоманд (в состав последнего входит дешифратор микрокоманд), дополнительный регистр страницСУ. .

Однако вложение подпрограмм известное устройство не обеспечивает, в связи с чем приходится использовать трехбайтовую микрокоманду ПК (переключатель). В этом случае возрастает объем ПЗУ и требуется дополнительное время для обращения к подпрограммам.

Кроме того, совмещение в одном слове кода команды и кода страницы перехода накладывает ограничение на количество страниц ПЗУ, вследствие чего для увеличения объема ПЗУ необходимо либо увеличить разрядность слова, лкбо увеличить формат микрокоманды ПВ, что приводит к дополнительному увеличению аппаратурных затрат и объема ПЗУ, а также к дополнительным затратам времени.

Цель изобретения - сокращение оборуQ дования и повышение быстродействия.

Указанная цель достигается тем, что устройство микропрограммного управления, содержащее блок постоянной памяти, выход которого соединен с информационным входом регистра микрокоманд, выход которого соединен со входом дешифратора микрокоманд, вход блока постоянной памяти соединен с выходами счетчика адреса и регистра стратниц, содержит стековую память, коммутатор, триггер, элементы И и НЕ, причем

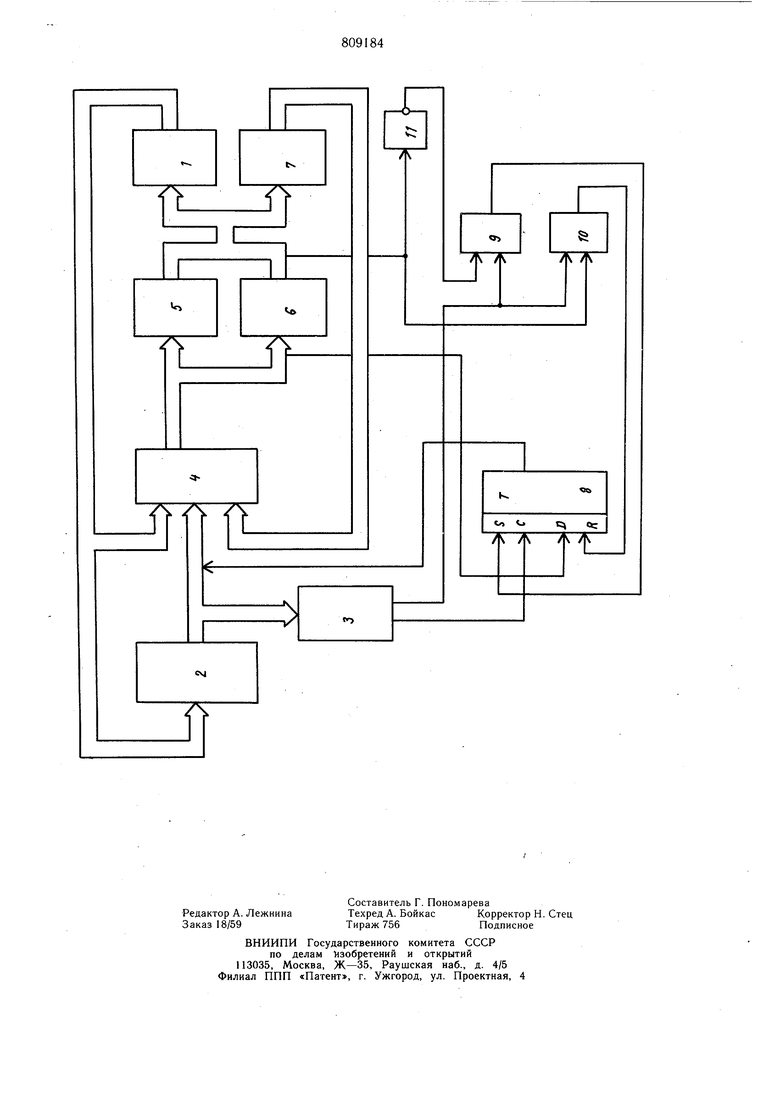

первый вход коммутатора соединен с выходом блока постоянной памяти, второй и третий входы коммутатора соединены соответственно с выходами регистра микрокоманд И стековой памяти, вход которой соединен с выходами счетчика адреса и регистра страниц, входы которых соединены с выходом коммутатора; выход триггера соединен с вторым входом коммутатора, С-вход триггера соединен с первым выходо1)Д дешифратора микрокоманд, D-вход триггера - с выходом коммутатора, а S- и R-входы триггера соединены соответственно с выходами первого и второго элементов И, выход регистра страниц подключен к первому входу второго элемента И и через элемент НЕ с первым входом первого элемента И, а вторые входы первого и второго элементов И соединены с вторым выходом дешифратора микрокоманд. На чертеже приведена блок-схема устройства микропрограммного управления. Устройство содержит блок 1 постоянной памяти, регистр 2 микрокоманд, дешифратор 3 микрокоманд, коммутатор 4, 5 адреса, регистр б страниц и стековую память 7. При этом счетчик 5 адреса определяет внутристраничный адрес команды, регистр 6 страниц определяет номер выбранной страницы ПЗУ, а стековая память 7 обеспечивает хранение адресов возврата. Кроме того, в состав устройства входят триггер 8, элементы И 9 и 10 и элемент НЕ 11, которые обеспечивают выбор той или иной половины ПЗУ 1. ПЗУ 1 имеет объем 16 К байт и состоит из 64 с. по 256 байт каждая, которые организованы в виде двух половин. Обращение к каждой из них осуществляется в зависимости от состояния шестого разряда регистра 6 страниц, причем «О соответствует страницам с нулевой по тридцать первую (цервая половина ПЗУ 1), а «1 -с тридцать второй по шестьдесяттретью (вторая половина ПЗУ 1). Стековая память 7 обеспечивает хранение 16-ти.слов по два байта каждое. Выход ПЗУ 1 соединен с входом регистра 2 микрокоманд и с первым входом коммутатора 4, выход которого соединен, в свою очередь, со входом счетчика 5 адреса и с входом регистра 6 страниц, причем выход шестого разряда коммутатора 4 соединен также с D-входом триггера 8. Выход регистра 2 микрокоманд соединен с входом дешифратора 3 и со вторым входом коммататора 4, причем входы пяти младших разрядов коммутатора 4 подключены к выходам пяти младших разрядов регистра 2 микрокоманд, а вход шестого разряда - к выходу триггера 8. Выходы счетчика 5 адреса и регистра 6 страниц подключены к адресным входам ПЗУ 1 и к входам стековой памяти 7, причем выход шестого разряда регистра 6 страниц подключен также к входу элемента НЕ ,11 и к входу элемента И 10. Выход элемента НЕ 11 соединен со входом элемента И 9, а выход дешифратора 3 - с входами элементов И 9 и 10. Выход последнего соединен с R - входом триггера 8, S-вход которого подключен к выходу элемента И 9, а С-вход - к выходу дешифратора 3. Кроме того, выход стековой памяти 7 соединен с третьим входом коммутатора 4. Предлагаемое устройство работает следующим образом. При выполнении любой микрокоманды передачи управления ее код, выбранный из ПЗУ 1 по адресу со счетчика 5 адреса и регистра 6 страниц, поступает на вход регистра 2 микрокоманд и хранится в нем в течение всего времени выполнения данной микрокоманды. Исходное положение триггера 8 соответствует состоянию «О. Микрокоманда ПВ является двухбайтовой, причем три старших разряда первого байта (6-8) содержат код данной микрокоманды, пять младших (I-5)-номер страницы ПЗУ, а второй байт представляет собой адрес ячейки ПЗУ. При выполнении микрокоманды ПВ на первом этапе происходит увеличение на единицу содержимого счетчика 5 адреса и запись нового содержимого счетчика 5 адреса и содержимого регистра 6 страниц в стековую память 7 (с предварительным увеличением ее адреса на единицу. На втором этапе вначале из ПЗУ 1 осуществляется выборка второго байта данной микрокоманды, который через первый вход коммутатора 4 записывается в счетчик 5 адреса. Затем номер страницы ПЗУ из пяти младших разрядов регистра 2 микрокоманд,и триггера 8 через второй вход коммутатора 4 поступает в шестиразрядный регистр 6 страниц. Таким образом, в счетчике 5 адреса и регистра 6 страниц оказывается полный адрес ячейки ПЗУ, в которую передается управление, а полный адрес ячейки возврата запоминается в стековой памяти. Микрокоманда ВВ является однобайтовой. При ее выполнении на первом этапе из стековой памяти 7 считывается первый байт адреса возврата, который через третий вход коммутатора 4 записывается в счетчик 5 адреса. На втором этапе содержимое счетчика 5 адреса увеличивается на единицу, так как при выполнении микрокоманды ПВ в стековой памяти 7 оказывается записанный фактический адрес второго байта этой микрокоманды, а не адрес следующей микрокоманды. Одновременно из стековой памяти 7 считывается второй байт адреса возврата - номер страницы ПЗУ (ячейки возврата), который через третий вход коммутатора 4 записывается в регистр 6 страниц (с последующим уменьшением на единицу адреса стековой памяти 7). При этом информация с выхода шестого разряда коммутатора 4 поступает на О-вход триггера 8 и заносится в последний, так как на его С-вход поступает соответствующий управляющий сигнал с выхода дешифратора 3. Таким образом, в счетчике 5 адреса и регистре 6 страниц оказывается полный адрес ячейки возврата, а содержимое триггера 8 соответствует выбранной половине ПЗУ1, т.е. той половине, в которой расположен адрес ячейки возврата. Для перехода из одной половины ПЗУ1 в другую используется микрокоманда УСП (Установка страниц ПЗУ), которая является однобайтовой. При ее выполнении управляющий сигнал с выхода дешифратора 3 поступает на входы элементов И 9 и 10. В результате этого, при наличии «1 в шестом разряде регистра 6 страниц сигнал «1 с выхода последнего поступает на вход элемента НЕ 11 и на вход элемента И 10. Элементы И 9 и 10 и элемент НЕ 11 срабатывают, причем на Р-вход триггера 8 поступает сигнал «1, а на S-вход - сигнал «О, так что триггер 8 устанавливается в состояние «О. При наличии «О в шестом разряде регистра 6 страниц на R-вход триггера 8 поступает сигнал «О, а на S-вход - сигнал «1, так что триггер 8 устанавливается в состояние «1. Таким образом, по микрокоманде УСП осуш,ествляется установка триггера в состояние, противоположное состоянию шестого разряда регистра 6 страниц. Микрокоманда ПК является трехбайтовой, причем первый байт содержит код данной микрокоманды, второй - номер страницы ПЗУ, а третий - адрес ячейки ПЗУ. Данная микрокоманда обладает той особенноетью, что адрес третьего байта не является постоянным, а может изменяться, например по содержимому сумматора центрального процессора (не показан). В этом случае адрес третьего байта может равняться сумме адреса второго байта, увеличенного на единицу и содержимого сумматора. Для реализации этого принципа используют или непосредственное сложение адресов в сумматоре с последуюшей пересылкой результата в счетчик 5 адреса, или добавление в последний количества единиц, равного содержимому сумматора. Поскольку в микрокоманде ПК для номера страницы ПЗУ отводится целый байт, это позволяет непосредственно с помбщью этой микрокоманды обращаться к обоим половинам ПЗУ 1. Это обеспечивается тем, что при выборке второго байта из ПЗУ 1 его содержимое через первый вход коммутатора 4 поступает не только на регистр 6 страниц, но и в триггер 8 (см. микрокоманду ВВ). Так как изменение содержимого регистра страниц происходит только после выборки третьего байта, то с целью задержки в этой цепи используется буферный регистр (не показан). Таким образом, на примере микрокоманды ПК видно, что данное устройство обеспечивает работу и с такими микрокомандами, которые позволяют обращаться к обеим половинам ПЗУ 1. Предлагаемое устройство микропрограммного управления позволяет сократить объем ПЗУ приблизительно на 6%, повысить быстродействие приблизительно на 10% и удвоить объем ПЗУ с меньшими затратами оборудования. При этом экономия ПЗУ для хранения микропрограммы составляет не менее от общего объема ПЗУ. Формула изобретения Устройство микропрограммного управления, содержащее блок постоянной памяти, выход которого соединен с информационным входом регистра микрокоманд, выход которого соединен со входом дешифратора микрокоманд, вход блока постоянной памяти соединен с выходами счетчика адреса и регистра страниц, отличающееся тем, что, с целью сокращения оборудования и повышения быстродействия, оно содержит стековую память, ко.ммутатор, триггер, элементы И и НЕ, причем первый вход коммутатора соединен с выходом блока постоянной памяти, второй и третий входы коммутатора соединены соответственно с выходами регистра микрокоманд и стековой памяти, вход стековой памяти coeдинe с выходами счетчика адреса и регистра страниц, входы которых соединены с выходом коммутатора, выход триггера соединен со вторым входом коммутатора, выход триггера соединен со вторым входом коммутатора, С-вход триггера соединен с первым выходом дешифратора микрокоманд, D-вход триггера - с вы.ходом коммутатора, S- и R-входы триггера соединены соответственно с выходами первого и второго элементов И, выход регистра страниц соединен с первым входом второго элемента И и через элемент НЕ с первым входом первого элемента И, вторые входы первого и второго элементов И соединены с вторым выходом дешифратора микрокоманд. Источники информации, принятые во внимание при экспертизе 1.Патент США № 3794980, кл. 340-172, 5, опублик. 1974. 2.Техническая документация 1ЦЗ. 050. 173. Л., ГСКТБ, 1975 (прототип).

Авторы

Даты

1981-02-28—Публикация

1979-04-12—Подача