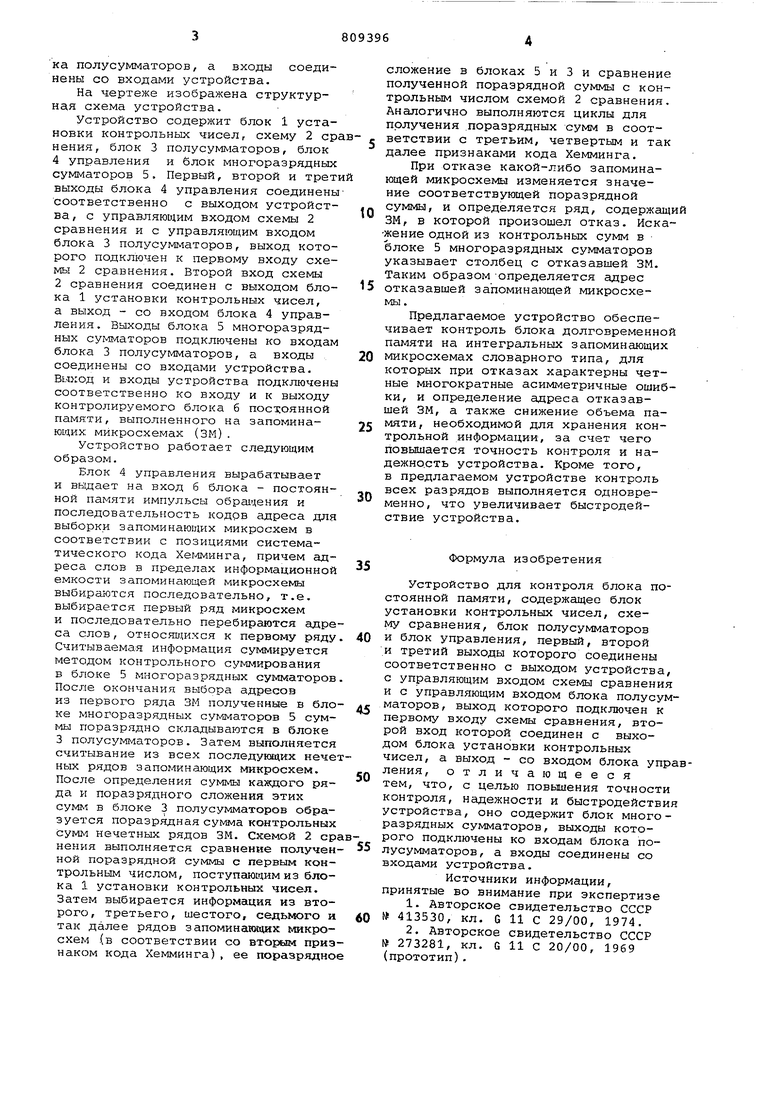

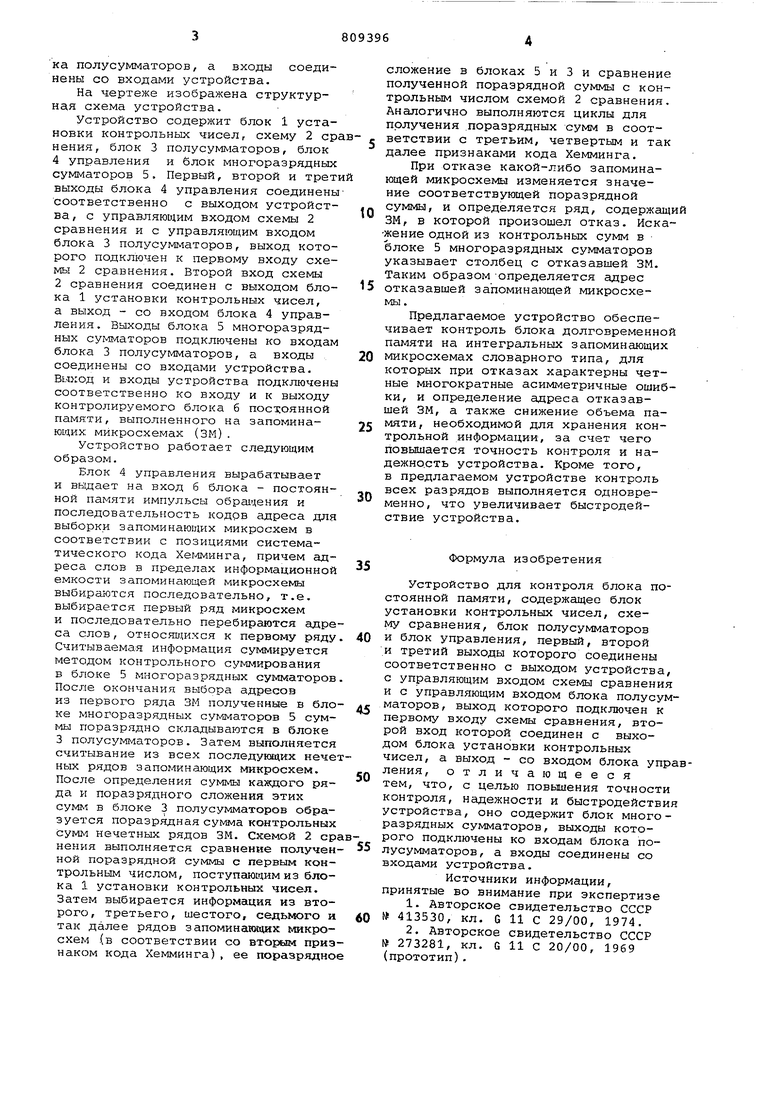

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКА ПОСТОЯННОЙ ПАМЯТИ ка полусумматоров, а входы соединены со входами устройства. На чертеже изображена структурная схема устройства. Устройство содерхшт блок 1 установки контрольных чисел, схему 2 сра нения, блок 3 полусуь1маторов, блок 4 управления и блок многоразрядных сумматоров 5. Первый, второй и трети выходы блока 4 управления соединены соответственно с выходом устройства, с управляющим входом схемы 2 сравнения и с управляющим входом блока 3 полусумматоров, выход которого подключен к первому входу схемы 2 сравнения. Второй вход схемы 2 сравнения соединен с выходом блока 1 установки контрольных чисел, а выход - со входом блока 4 управления. Выходы блока 5 многоразрядных суг Ф1аторов подключены ко входам блока 3 полусумматоров, а входы соединены со входами устройства. ВЕЛХОД и входы устройства подключены соответственно ко входу и к выходу контролируемого блока 6 пос1:оянной памяти, выполненного на запомина- ющих микросхемах (ЗМ). Устройство работает следующим образом. Блок 4 управления вырабатывает и выдает на вход 6 блока - постоянной памяти импульсы обра1дения и последовательность кодов адреса для выборки запоминающих микросхем в соответствии с позициями систематического кода Хе1.Ф1инга, причем адреса слов в пределах информационной емкости запоминающей микросхемы выбираются последовательно, т.е. выбирается первый ряд микросхем и последовательно перебираются адре са слов, относящихся к первому ряду Считываемая информация суммируется методом контрольного суммирования в блоке 5 многоразрядных сумматоров После окончания выбора адресов из первого ряда ЗМ полученные в бло ке многоразрядных сумматоров 5 сумГ/1Ы поразрядно складываются в блоке 3 полусумматоров. Затем выполняется считывание из всех последукгцкх нече ных рядов запоминающих микросхем. После определения суммы каждого ря да и поразрядного сложения этих сумм в блоке 3 полусумматоров обра зуется поразрядная сумма контрольны Сумм нечетных рядов ЗМ. Схемой 2 с нения выполняется сравнение получе ной поразрядной суммы с первым кон трольным числом, поступеиощим из бло ка 1 установки контрольных чисел. Затем выбирается информация из вто рого, третьего, шестого, седьмого так далее рядов запоминающих микро схем (в соответствии со при наком кода Хемминга), ее поразрядн ложение в блоках 5 и 3 и сравнение олученной поразрядной суммы с конрольным числом схемой 2 сравнения. Аналогично выполняются циклы для олучения поразрядных сумм в соответствии с третьим, четвертым и так далее признаками кода Хемминга. При отказе какой-либо запоминающей микросхемы изменяется значение соответствующей поразрядной суммы, и определяется ряд, содержащий ЗМ, в которой произошел отказ. Искаение одной из контрольных сумм в блоке 5 многоразрядных сумматоров указывает столбец с отказавшей ЗМ. Таким образом -определяется адрес отказавшей запоминающей микросхемы . Предлагаемое устройство обеспечивает контроль блока долговременной памяти на интегральных запоминающих микросхемах словарного типа, для которых при отказах характерны четные многократные асимметричные ошибки, и определение адреса отказавшей ЗМ, а также снижение объема памяти, необходимой для хранения контрольной информации, за счет чего повышается точность контроля и надежность устройства. Кроме того, в предлагаемом устройстве контроль всех разрядов выполняется одновременно, что увеличивает быстродействие устройства. Формула изобретения Устройство для контроля блока постоянной памяти, содержащее блок установки контрольных чисел, схему сравнения, блок полусумматоров и блок управления, первый, второй и третий выходы которого соединены соответственно с выходом устройства, с управляющим входом схемы сравнения и с управляющим входом блока полусумматоров , выход которого подключен к первому входу схемы сравнения, второй вход которой соединен с выходом блока установки контрольных чисел, а выход - со входом блока управления, отличающееся тем, что, с целью повышения точности контроля, надежности и быстродействия устройства, оно содержит блок многоразрядных сумматоров, выходы которого подключены ко входам блока полусумматоров, а входы соединены со входами устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 413530, кл. G 11 С 29/00, 1974. 2.Авторское свидетельство СССР № 273281, кл. G 11 С 20/00, 1969 (прототип).

ЗН

I о I I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля постоянной памяти | 1979 |

|

SU824316A1 |

| Устройство для контроля блоков постоянной памяти | 1979 |

|

SU858115A1 |

| Устройство для контроля долго-ВРЕМЕННОй пАМяТи | 1979 |

|

SU813508A1 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU877621A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1111205A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Запоминающее устройство с автономным контролем | 1980 |

|

SU907588A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1115107A1 |

| ЦИФРОВОЙ СИНТЕЗАТОР ЧАСТОТЫ | 2022 |

|

RU2793776C1 |

L.

I

K.J

Авторы

Даты

1981-02-28—Публикация

1979-05-03—Подача