(54) ЗАПОМдаАКМЦЕЕ УСТРОЙСТВО С АВТОНОМНЫМ КОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

| Запоминающее устройство с коррекцией ошибок | 1982 |

|

SU1161990A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU972601A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU875456A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с обнаружением ошибок | 1983 |

|

SU1149315A1 |

| Запоминающее устройство с диагностикой отказов /его варианты/ | 1984 |

|

SU1196958A1 |

I

Изобретение относится к вычислительной технике, а именно к запоминающим устройствам на многоразрядных модулях памяти на интегральных микросхемах со схемами о&гаружершя отказавших модулей.

Известно устройство для кодирования и декодирования циклических кодов при передаче информации по каналам связи. В устройстве используются постоянные запоминающие блоки и сумматоры (1).

Уcтpoйtтвo требует для обнаружения ошибок либо большого времени на деко;и рованне, либо большой избыточности.

Известна информагцюнная память, состоящая из М модулей памяти по В разрядов в каждом модуле, устройство контроля, состоящее из В блоков контроля по тетиости и обнаруживающее ошибки при отказе модуля памяти, т.е. до В разрядов (2).

Недостатком устройства является излишняя избыточность в проверочных разрядах и невозможность определения места отказа.

Наиболее близким к предлагаемому по тех1шческой сущности являются запоминающие

устройства с контролем на основе ««елового контроля по мо;;улю, содержащие накопитель, информационные входы которого подклкгаены к входам первого формирователя контрольных разрядов, а информаш онные выходы - ко входам второго формирователя контрольных разрядов, схему срав1К1шя, одни входы которой подключены к выходу второго формирователя контрольных разрядов, а другие к выходам контрольных разрядов накопите10ля 3.

Однако устройство характеризуется недостаточной точностью контроля, а именно невозможностью определения номера отказавшего модуля н определения всех оишбок при откаISзе одного МОДУЛЯ.

Цель изобретения - повышение точности

контроля.

Поставлеиная цель достигается тем, что в запоминающее устройство с автономным

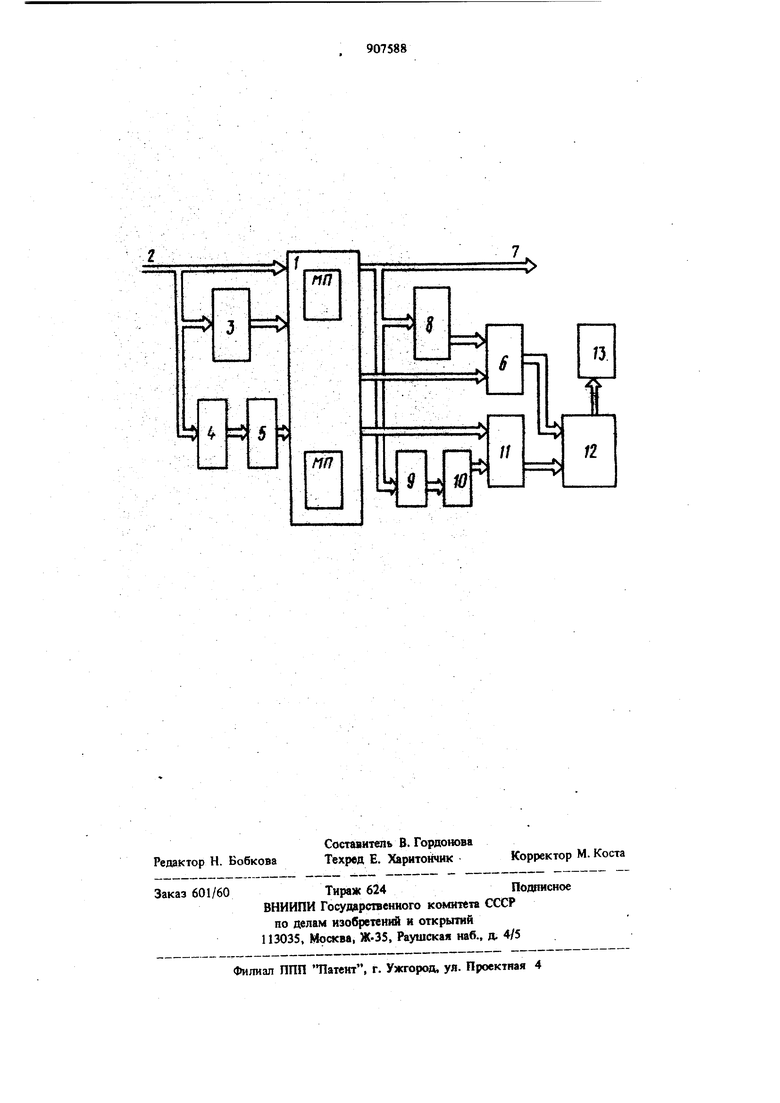

20 контролем, содержащее накопитель лнформационные входы которого подключены к входам первого формирователя сигналов контрольных разрядов и являются ниформавдон3. 90 ными входами устройства , одни контрольные входы накопителя подключены к выходам первого формирователя сигналов контрольных разрядов, выходы накопителя подключены к входам второго формирователя сигналов контрольных разрядов и являются информационными выходами устройства, выходы второго формнрователя сигналов контрольных разрядов подключены к одним входам схемы сравнения, вторые входы которой подключены к одним контрольным выходам накопителя, дополнительно введены первый постоянный накопитель, входы которого подключены к информационным входам накопителя, первый формирователь сигналов четности, входы которого подключены к выходам первого постоянного накопителя, а выходы - к другим контрольным входам накопителя, второй постоянный накопитель, входы которого подклю чены к информационным выходам накопителя второй формирователь сигналов четности , вхо ды которого подключены к выходам второго постоянного накопителя, сумматор-вычитатель, одни входы которого подключены к другим контрольным выходам накопителя, а другие входы - к выходам второго формирователя сигналов четности, и третий постоянный накопитель, одни входы которого подключены к выходам схемы сравнения, другие входы к выходам сумматора-вычитателя, а выходы третьего постоянного накопителя явЛ|Яются управляющими выходами устройства. На чертеже представлена блок-схема предлагаемого устройства с автономным контролем Устройство содержит накопитель , информационные входа: 2, первый формирователь 3 сигналов контрольных разрядов, первый посто янный накопитель 4, первый формирователь 5 сигналов четности, схему 6 сравнения, информ ционные выходы 7, второй формирователь 8 сигналов контрольных разрядов, второй постоянный накопитель 9, второй формирователь 10 сигналов разрядов четности, сумматор-вычитатель 11, третий постоянный накопитель 12 и регистрирующую схему 13. Устройство работает следующим образом. На информационные входы 2 накопителя входы первого формирователя 3 сигналов контрольных разрядов и входы первого тшстоянного накопителя 4 поступает двоичный код числа, подлежащего записи в очередном цикле. В информационные разряды накопителя 1 непосредственно, а в контрольные разряды после соответствующей обработки в кодирующем устройстве, состо 1щем из первого постоянного накопителя 4, первого формирователя 5 четности и первого формирователя 3 сигналов контрольных разрядов по модулю 3. Если А - величина нечетного выбранного модуля, то возможная величина разрядности модуля памяти не превышает величину () разряд и количество охваченнь1х контролем модулей памяти не может превышать величины (А-1). Количество контрольных разрядов, необходимых для записи вычета числа по модулю А, определяется величиной К } + + logsА, где logjA - целая часть тасла. С помощью первого формирователя 3 сигналов контрольных разрядов по модулю определяется вычет записываемого числа, который записьшается в Kj контрольных разряда. Определение вычета производится следующим образом. Всем (А-1) разрядам с первого модуля памяти придается вес один. Всем (А-1) разрядам со второго модуля памяти придается вес два. Всем (А-1) разрядам с третьего модуля памяти придается вес три и т.д. Указанные разряды в соответствии с присвоенны1У и весами поступают на первый форл ирователь 3 сигналов контрольных разрядов по модулю А. Известно , что формирователи по нечетному модулю имеют входы с весами 1, 2, 4, ..., т.е. равными степени двойки. Поэтому для того, чтобы иметь вес, не равный степени двойки, необходимо разряды с модулей памяти с такими весами подать одновременно на несколько входов с различными весами первого формирователя 3 сигналов по модулю А. Это позволяет закодировать все контролируемые модули {акопителя 1. Определение Кр контрольных разрядов в первом постоянном накопителе 4 производится- следующим образом. Первый постоянный накопитель 4 состоит из (А-1) модуля, каждый из которых предназначен для кодировки своего модуля памяти. {А-1) разряд с модуля памяти поступает на вход своего первого постоянного накопителя 4, где производится кодировка по следующему алгоритму 00 - одна кодовая комбинация для всех комбинаций, содержащих всего 1 единицу в коде из (А-1) разрядов одна кодовая комбинация для всех комбинаций, содержащих две единицы в коде из (А-1) разрядов - одна кодовая комбинация одна кодовая комбинация. т.е, для кода из (А-1) разрядов необходимо всего (2 1) кодовая комбина)1.ия , для того, 1гтобы определить иалиаде ошибки любой кратности в (А-1) разрядном модуле всех () МОЛ)лей памяти. Лля этого необходимо иметь когпрольные рачрлды К, количество которых определяется т иыражения

Кп 1 + 1од,(А-1)), где logj(A-r) - целая часть числа.

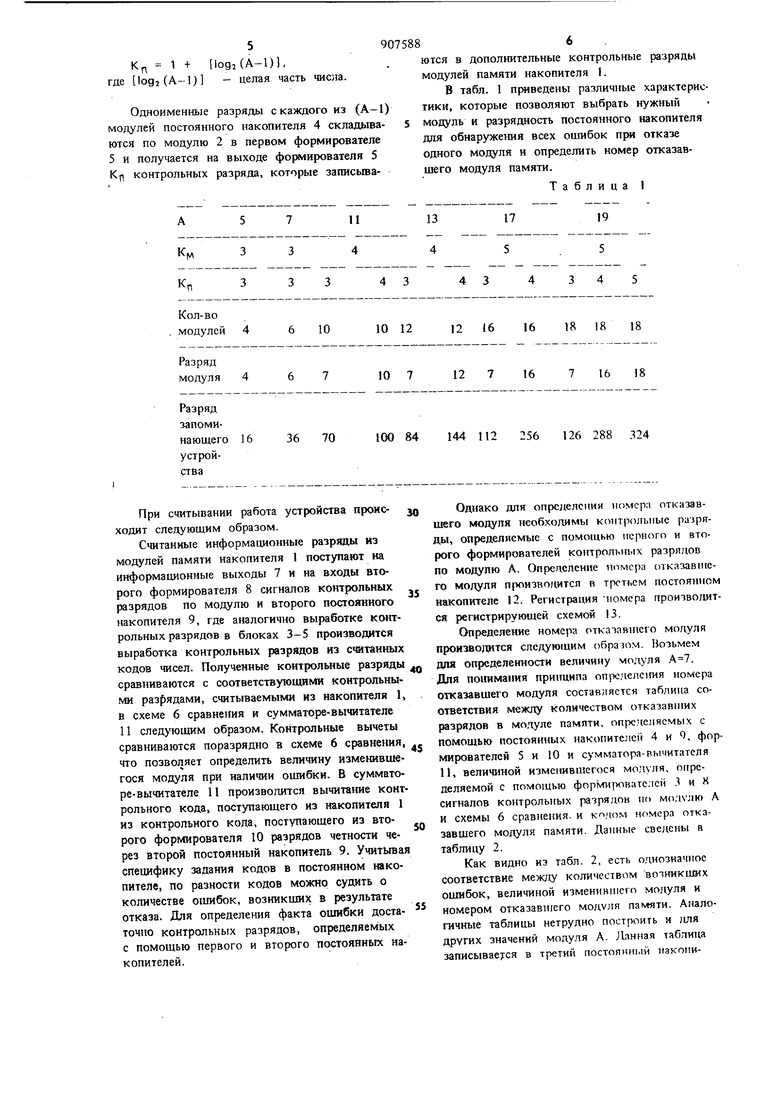

Одноименные разряды с каждого из (А-1) модулей постоянного накопителя 4 складыва- 5 модуль и разрядность постоянного накопителя ются по модулю 2 в первом формирователедля обнаруже1шя всех ошибок при отказе

5 и получается на выходе формирователя 5одного модуля и определить номер отказавКп контрольных разряда, которые записьшз-шего модуля памяти. При считывании работа устройства происходит следующим образом. Считанные информационные разряды из модулей памяти накопителя 1 поступают на информационные выходы 7 и на входы второго формирователя 8 сигналов контрольных разрядов по модулю и второго постоянного накопителя 9, где аналогично выработке контрольных разрядов в блоках 3-S производится выработка контрольных разрядов из считанных кодов чисел. Полученные контрольные разряды сравниваются с соответствуюишми контрольными разрядами, считываемыми из накопителя 1, в схеме 6 сравнения и сумматоре-вычитателе 11 следующим образом. Контрольные вычеты сравниваются поразрядно в схеме 6 сравнения, что позволяет определить величину изменившегося модуля при наличии ошибки. В сумматоре-вычитатепе 11 производится вычитагше контрольного кода, поступающего из накопителя 1 из контрольного кода, поступающего из второго формирователя 10 разрядов четности через второй постоянный накопитель 9. Учитывая специфику задания кодов в постоянном накопителе, по разности кодов можно судить о количестве ошибок, возникишх в результате отказа. Для определения факта ошибки достаточно контрольных разрядов, определяемых с помощью первого и второго постоянных накопителей.

9075886

ются в дополнительные контрольные разряды модулей памяти накопителя I.

В табл. 1 приведены различные характеристики, которые позволяют выбрать нужный

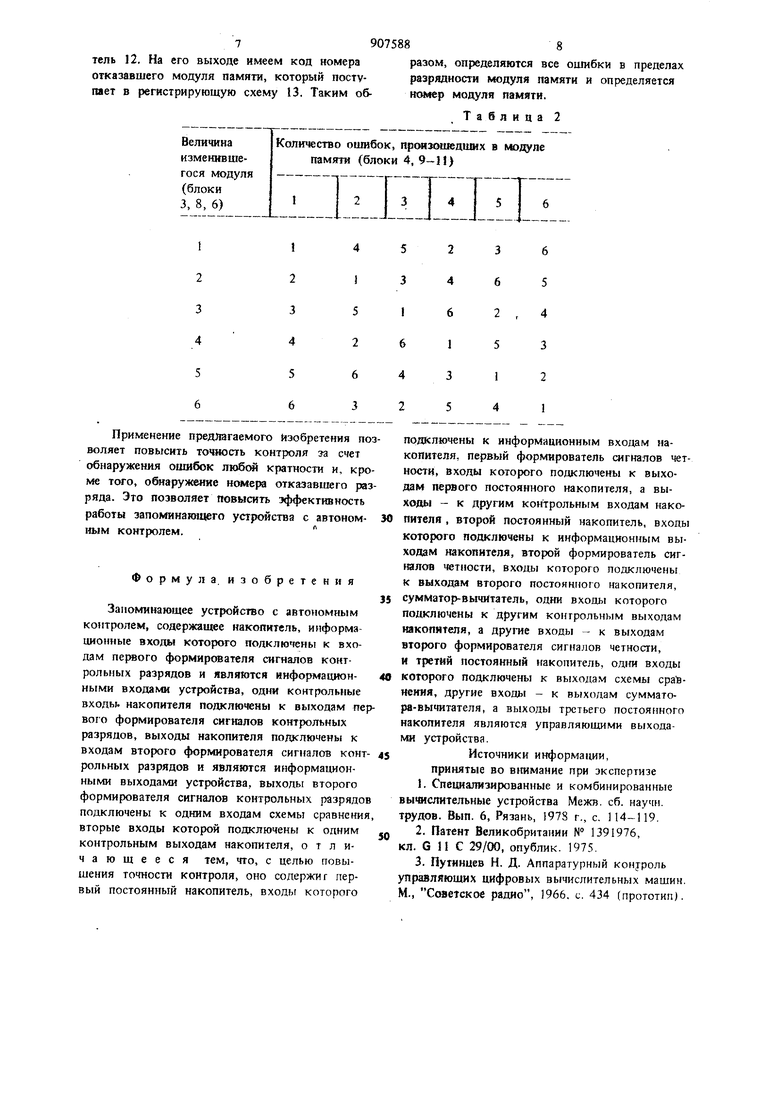

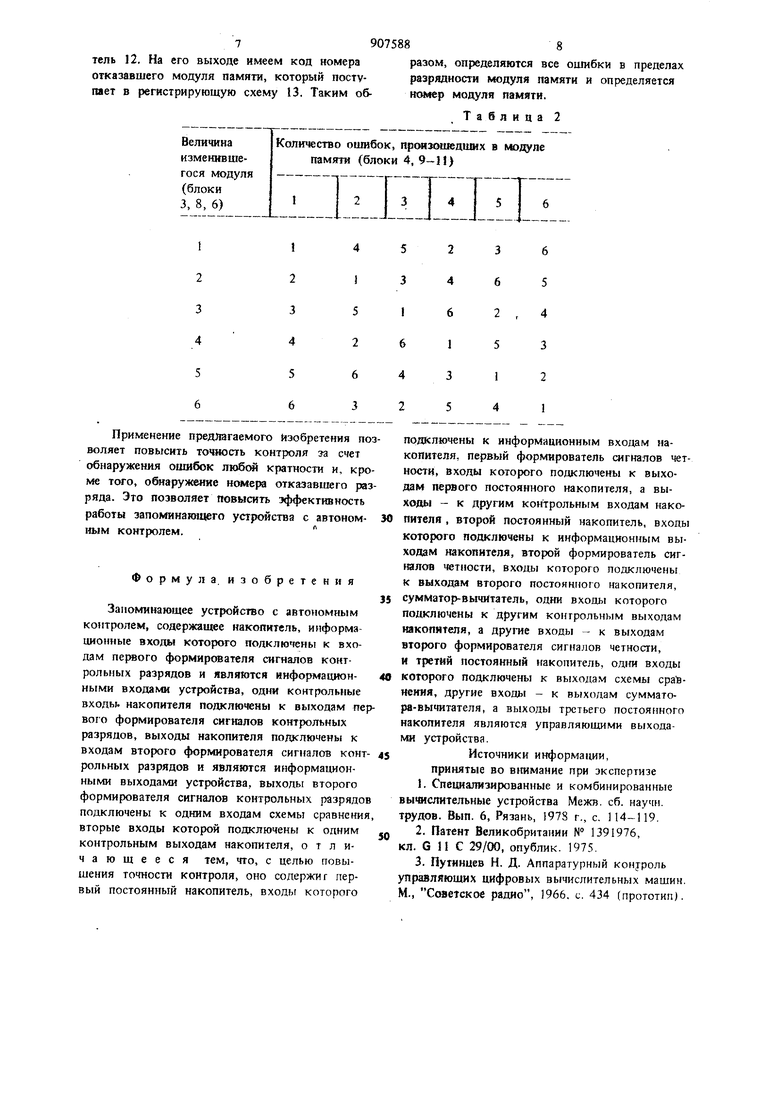

Таблица I Однако для определения номера отказавшего модуля необходимы контрольные разряды, определяемые с помощью iicpiioro и второго формирователей контрольных разрядов по модулю А. Определеине тчтмсра отказавшего модуля производитсп п третьем постоянном накопителе |2. Регистрация номера производится регистрирующей схемой 13. Определение номера отказавшего модуля производится следующим обра}ом. Возьмем для опрюделенности величину модуля . Для по1тма1 ия принципа оп;тс,челе1шя номера отказавшего модуля составляется таблица соответствия между количеством отказавших разрядов в модуле памяти, определяемых с помощью постоянных накопителей 4 и Ч, формирователей 5 и 10 и сумматора-вычитателя 11, величиной изменившегося модуля, определяемой с помощью формщювателе 3 и Н сигналов контрольных разрядов чо МОДУЛЮ Л И схемы 6 сравнения, и кодом номера отказавшего модуля памяти. Данные сведень в таблицу 2. Как видно из табл. 2, есть однозначное соответствие между количеством в пникщих ошибок, величиной изменившего модуля и номером отказавшего МОДУЛЯ памяти. Аналогичные таблицы нетрудно построить и ;шя других значений модуля А. Ланная таблица записывается в третий постоянный накопитель 12. На его выходе имеем код номера отказавшего модуля памяти, который поступает в регистрирующую схему 13. Таким обПрименение предяагаемого изобретения по воляет повысить точйюсть контроля за счет обнаружения ошибок любЫ кратности и, кро ме того, обнаружение номера отказавшего ра ряда. Это позволяет повысить эффективность работы запоминаннцего устройства с автономным контролем. Формула, изобретения Запоминающее устройство с автономным контролем, содержащее накопитель, информационные входа которого подключены к входам первого формирователя сигналов контрольных разрядов и являются информационными входами устройства, одни контрольные входы, накопителя подолючены к выходам пе вого формирователя сигналов контрольных разрядов, выходы накопителя поделючены к входам второго формирователя сигналов конт рольных разрядов и являются информационными выходами устройства, выходы второго формирователя сигналов контрольных разрядо подключены к одним входам схемы сравнени вторые входы которой подключены к одним контрольным выходам накопителя, отличающееся тем, что, с целью повышения точности контроля, оно содержит первый постоянный накопитель, входы которого

9075888

разом, определяются все ошибки в пределах разрядности модуля памяти и определяется номер модуля памяти.

Таблица 2 подключены к информационным входам накопителя, первый формирователь сигналов четности, входы которого подключены к выходам первого постоянного накопителя, а выходы - к другим контрольным входам накопителя , второй постоянный накопитель, входы которого подключены к информационным выходам накопителя, второй формирователь сигкалов четности, входы которого подключены к выходам второго постоянного накопителя, сумматор-вычитатель, одни входы которого подключены к другим контрольным выходам накопителя, а другие входы - к выходам второго формирователя сигналов четности, и третий постоянный накопитель, одни входы которого подключены к выходам схемы сра1внсния, другие входы - к выходам сумматора-вычитателя, а выходы третьего постоянного накопителя являются управляющими выходалш устройства. Источники информации, принятые во внимание при экспертизе 1.Специализированные и комбинированные вывдслительные устройства Межв. сб. научи. трудов. Вып. 6, Рязань, 1978 г., с. 114-П9. 2.Патент Великобритании № 1391976, кл. G И С 29/00, опублик. 1975. 3.Путинцев Н. Д. Аппаратурный контроль управляющих цифровых вычислительных машин. М., Ссшетское радио, 1966. с. 434 (прототип).

Авторы

Даты

1982-02-23—Публикация

1980-07-10—Подача