(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПОСТОЯННОЙ

ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блокапОСТОяННОй пАМяТи | 1979 |

|

SU809396A1 |

| Устройство для контроля постоянной памяти | 1979 |

|

SU824316A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1080218A2 |

| Устройство для контроля блоков постоянной памяти | 1980 |

|

SU877621A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для контроля долго-ВРЕМЕННОй пАМяТи | 1979 |

|

SU813508A1 |

| Устройство для контроля блоковпОСТОяННОй пАМяТи | 1979 |

|

SU809404A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| Постоянное запоминающее устройство с самоконтролем | 1979 |

|

SU858118A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

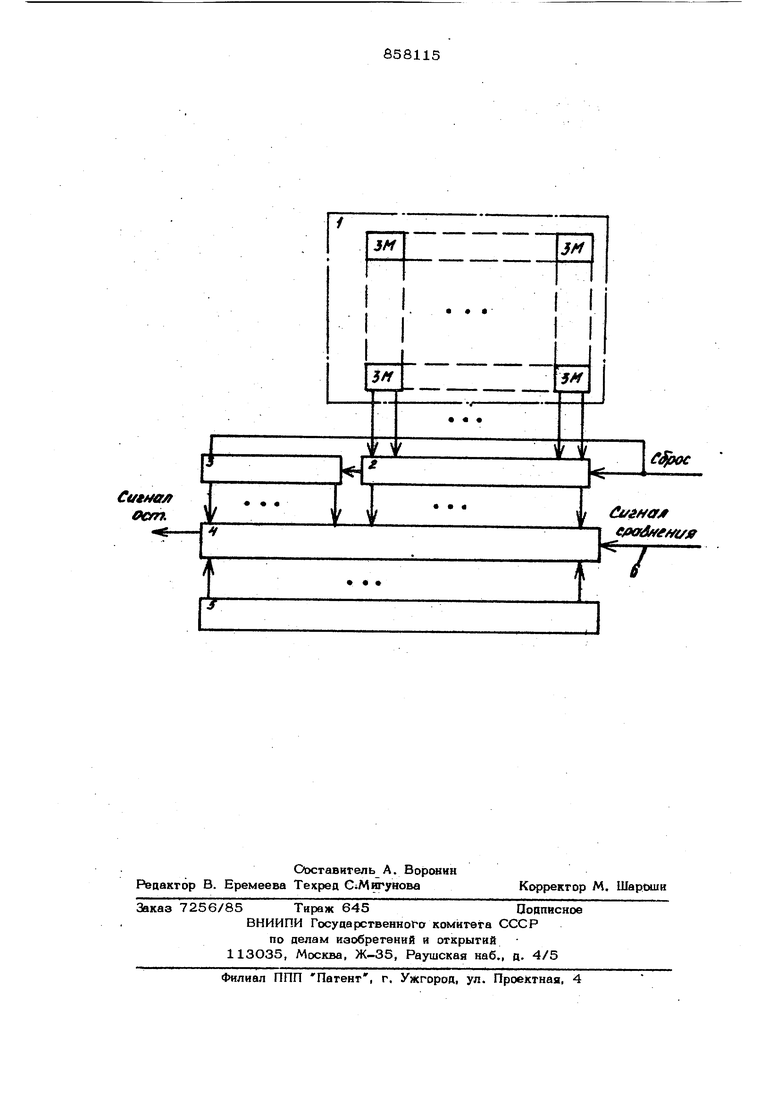

Изобретение огносится к области вычислительной техники, а именно к контролю долговременных запоминающих устройств на интегральных запоминающих микросхемах (ЗМ) словарного типа. Известен способ связи, использующий метод контрольного суммирования пр передаче информации между устройствами ЦВМ Г1. Однако способ не позволяет обнаруживать многократные пакетные ошибки. Известно также устройство для контро ля постоянных запоминающих устройств, которое в режиме контрольного суммирова ния осуществляет контроль путем после довательного сложения считываемых; слоев из ПЗУ и сравнение п.олученной суммы с контрольным числом 2. Однако устройство не позволяет обнару)й1вать некоторые комбинации четных ошибок при использовании в блоке памяти многоразрядных ЗМ. Наиболее близким по технической сущности к предлагаемому является устрой ство для контроля блока памяти по методу контрольного суммирования, содерж щее многоразрядный сумматор, узел установки контрольных чисел и регистр сравнения. Контроль информации основан на сравнении в регистре сравнения контрольных чисел, поступающих из угла, н многоразрядной суммы, полученной при сложении всех чисел блока в сумматоре при считывании. Подобное устройство позволяет определить однократную ошибку ГЗ. Недостатком известного устройства является низкая точность контроля при возникновении многократных ошибок в старших разрядах и использовании в блока памяти ЗМ словарного типа. Для ЗМ характерен асимметричный характер ошибр$ и псшные отказы,приводящие к многократ- . ным групповым ошибкам в массиве хранимой информации. Вероятность необнаружения четной ошибки Оц в старших разрядах для блока па-385мяги на ЗМ можно оценить следующим выражениемгде п , m - соответственно количество слов и разрядов в ЗМ. Цель изобретения - повышение точности устройства. Поставленная цель достигается тем, что в устройство для контроля блоков постоянной памяти, содержащее сумматор, информационные входы которого соединены со входами устройства, блок сравнения, первый вход которого соединен с шиной разряжения сравнения, блок установки контрольного двйичного числа, выходы которого подключены к одним из входов блока сравнения, информационные выходы сум матора соединены с другими входами блока, сравнения, выход которого соединен с вы ходом устройства, введен счетчик, вход кото рого соединен с выходом переноса единиц .сумматора, а выходы счетчика соединены соответствующими входами сумматора. На чертеже представлена функциональная схема предлагаемого устройства. Устройство содержит контролируемый блок постоянной памяти 1, сумматор 2, счетчик 3, блок сравнения 4, блок установки контрольного двоичного числа 5 и шину разрежения сравнения 6. Устройство работает следующим образом. При подаче на вход блока памяти 1 последовательно изменяемого кода адреса и импульса запроса с выхода блока памяти 1 многоразрядные числа считываются в сумматоре 2, где производится сложение. Единицы переполнения при сложении поступают с выхода переноса стар шего разряда сумматора 2 в счетчик 3. После того как все числа, хранимые в блоке памяти 1, будут считаны и просуммированы в блоке сравнения 4 под де ствием сигнала сравнения осуществляется сравнение суммы, полученной в сумматоре-2 и счетчике 3 с контрольным двоич 54 ным числом, поступающим из блока 5. Если суммы совпадают, вырабатывается сигнал сравнения и сигнал останова. Предлагаемое устройство позволяет обнаруживать многократные ошибки при отказе ЗМ в старших разрядах блока памяти. Вероятность обнаружения многократных ошибок зависит от количества разрядов счетчика 3. Если количество разрянов К счетчика 3 выбрать исходя из выражения.. 1 го вероятность обнаружения многократных ошибок будет близка к 1, в то время как известное устройство пропускает четные ошибки в старших разрядах, вероятность возникновения которых определяется из формулы (1) и достигает гГри различных tn,H п значения 25%. Формула изобретения Устройство для контроля блоков постоянной памяти, содержащее сумматор, информационные входы которого соединены со входами устройства, блок сравнения, первый вход которого соединен с шиной разрешения сравнения, блок установки контрольного двоичного числа, выходы которого подключены к одним из входов блока сравнения, информационные выходы сумматора соединены с другими входами блока сравнения, выход которого соединен с выходов устройства, отличающееся тем, что, с целью повышения точности устройства, в него введен счетчик, вход которого соединен с выходом переноса единиц сумматора, а выходы счетчика соединены с соответствующими входами сумматора. Источники информации, принятые во внимание при экспертизе 1.Патент США М , кл. 340-140, 1 А, 1973. 2.Авторское свидетельство СССР N 563697, кл. Q 11 С 29/00, 1976. 3.Клямко Э. И. Схемный и тестовой контроль автоматических цифровых вычислительных машин, М., Советское радио, 1963, с. 192 (прототип).

Авторы

Даты

1981-08-23—Публикация

1979-05-25—Подача