(54) ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

мультиплексор, первые входы которого подключены к выходам регистра, вторые выходы - к выходам дешифратора, а управляющий вход - к пятому входу блока управления, первый и второй блоки индкации, входы которых подключены соответственно к выходам второго мультиплексора и схемы сравнения.

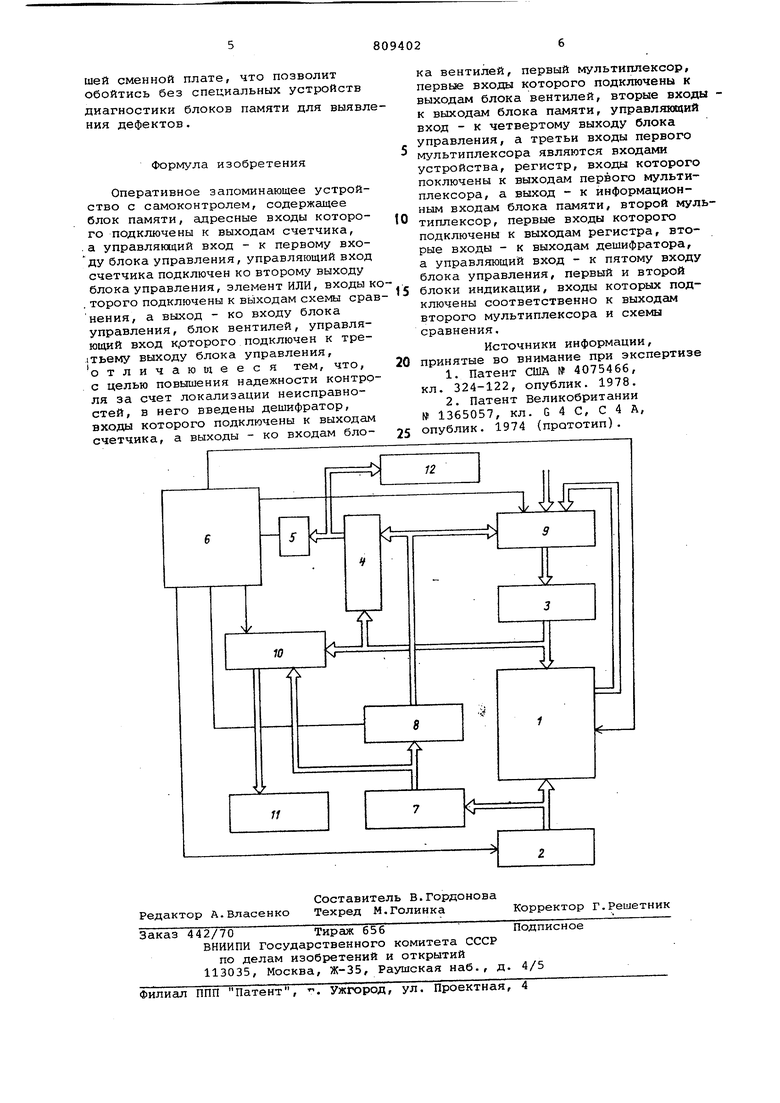

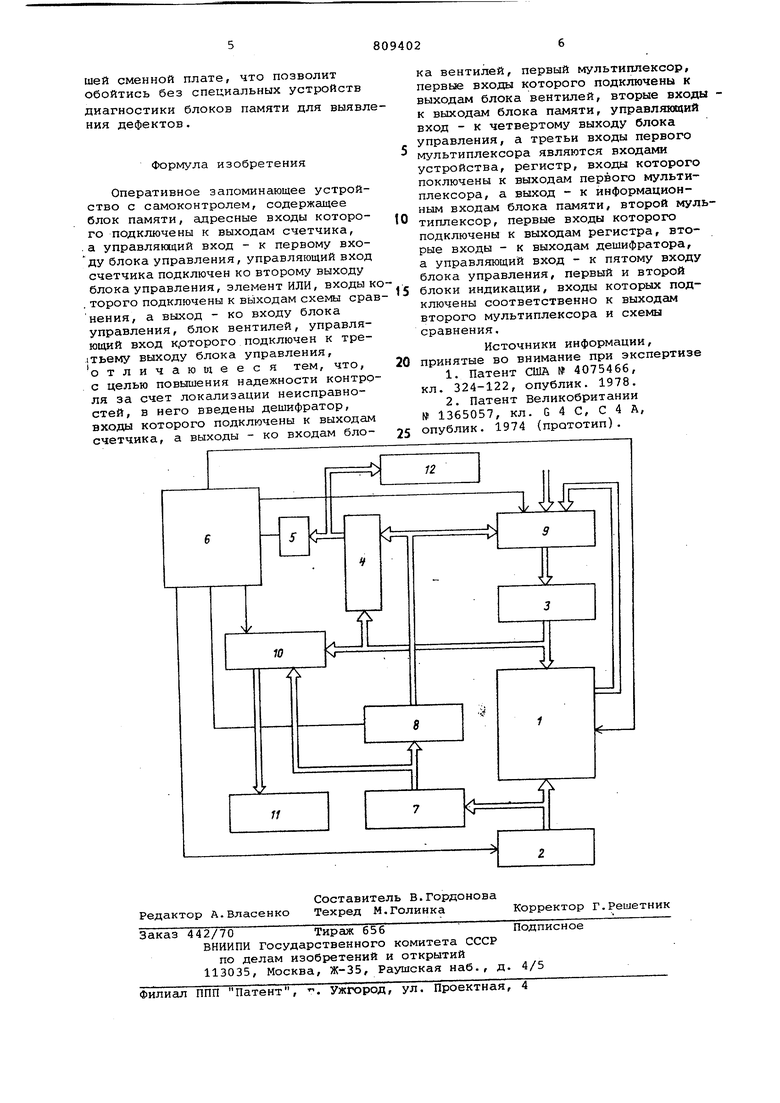

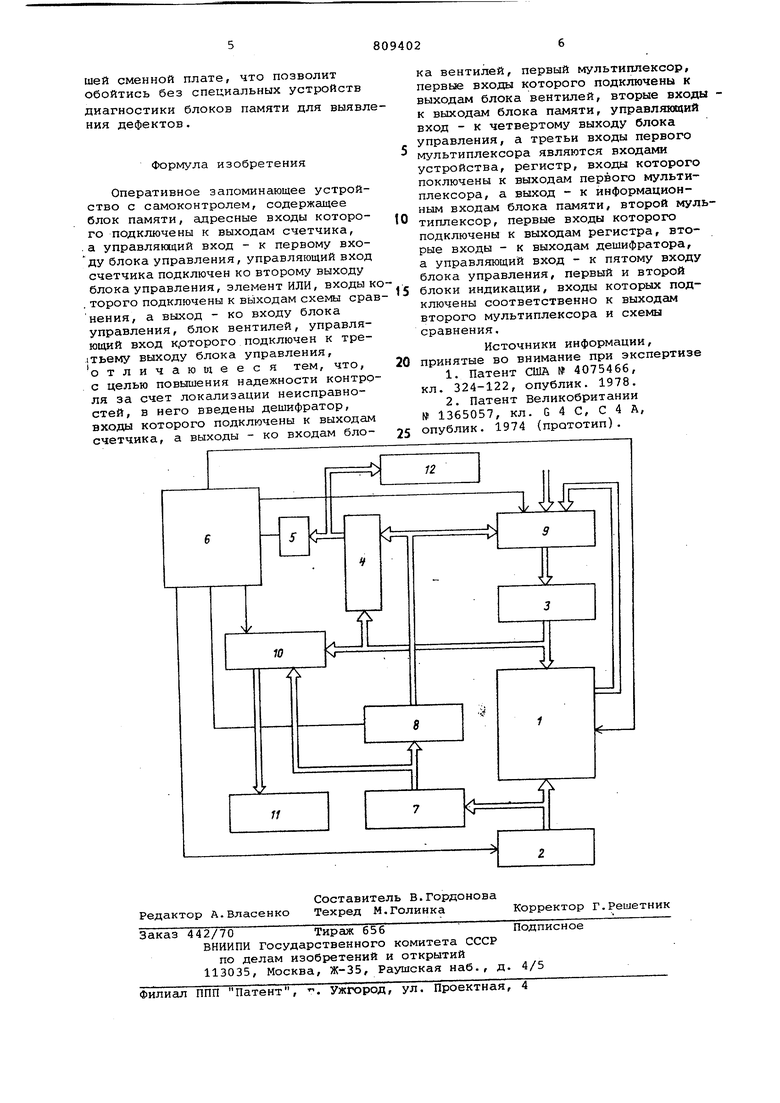

На чертеже приведена блок-схема оперативного запоминающего устройства с самоконтролем.

Оно содержит блок 1 памяти, счетчик 2, регистр 3, схему 4 сравнения элемент ИЛИ 5, блок 6 управления, дешифратор 7, блок 8 вентилей, первый и второй мультиплексоры 9 и 10, первый и второй блоки 11 и 12 индикации.

. Устройство работает следующим образом.

В режиме работы с внешними устройствами информация для записи в блок

Iпамяти поступает через мультиплексор 9 и регистр 3. При выводе иформации она может быть считана из регистра 3, куда передается из блока 1 памяти через мультиплексор 9. Как записываемая, так и считываемая информация индицируются блоком

IIиндикации.

В режиме контроля блока 1 памяти блок б управления запрещает обмен информацие11 между блоком 1 памяти и внешними устройствами и переключается на управление работой встроенных аппаратных средств контроля.

Сущность контроля состоит в том, что в каждую ячейку памяти записывается номер функциональной группы (номер одной сменной платы или ее части, содержащей по одной микросхеме в каждом разряде) , в которой, она находится. После такой записи во вс ячейки памяти осуществляется последовательное считывание состояния всех ячеек и сравнение его с требуемьлм значением, которое выводится на индикацию.

В случае несовпадения индицируется номер функциональной группы, в котором содержится неисправная ячейка. Несовпадение на определенно разряде указывает на неисправный разряд соответствующей функциональной группы. Таким образом локализуется неисправная сменная плата, а в случае, если функциональная группа содержит по одной микросхеме в каждом разряде, можно указать неисправную микросхему памяти. С целью более полной проверки ячеек памти описанный процесс повторяется с записью в память инверсных значений номеров функциональных групп.

В режиме контроля устройство работает следующим образом.

Блок 6 управления последовательно изменяет .состояние счетчика 2

и обеспечивает запись в ячейке блока 1 памяти кода, поступающего с дешифратора 7 через блок 8 вентилей, мультиплексор 9 и регистр 3. Дешифратор 7 преобразует код адреса ячейки в код номера функциональной группы, в которой находится данная ячейка. Блок 8 вентилей передает код с выходов дешифратора 7 ,на вход мультиплексора 9 без изменения. После

заполнения всех ячеек блока 1 памяти блок б управления устанавливает мультиплексор 10 на передачу информации с дешифратора 7, устанавливает режим считывания и начинает последовательно изменять состояние 5 Счетчика 2. Считываемая из блока 1 памяти информация поступает в регистр 3 и каждый раз поразрядно сравнивается схемой 4 сравнивания с требуемой информацией, поступающей с 0 дешифратора 7 через блок 8 вентилей. Элемент ИЛИ 5 в случае несоответствия сравниваемых кодов фиксирует это и блок б управления прекращает считывание информации из 5 блока 1 памяти. При -этом на блоке. 11 индикации индицируется номер неисправной функциональной группы, а на блоке 12 - неисправные разряды.

После фиксации индицируемой информации опрос блока 1 памяти продолжают . После окончания опроса блок 6 управления устанавливает блок 8 вентилей на инвертирование кода номера функциональной группы, поступающего с выходов дешифратора 7, и описанный выше процесс повторяется.

Локализация места неисправности осуществляется путем последовательной адресации ячеек блока памяти 0 и записи в каждую из них номера

функциональной группы (сменной платы или ее части, содержащей по одной микросхеме в каждом разряде), в которой соответствующая ячейка 5 находится. После этого осуществляется считывание содержимого блока памяти и сравнение содержимого каждой ячейки с номером функциональной группы, в которой она находится. В 0 случае несовпадения индицируется номер функциональной группы и разряды, на которых обнаружено несоответствие. То же повторяется с записью инвертированной информации. Это позволяет повысить контролирующую способность средств встроенного контроля, обеспечивает возможность локализации неисправностей до уровня сменной платы и неисправной микросхемы памяти с выводом диагностической информации на индикацию.

Это дает воз1уюжность своевременно осуществлять замену отказавших сменных плат памяти на исправные, а также оперативно производить замену неисправных микросхем в отказавшей сменной плате, что позволит обойтись без специальных устройств

диагностики блоков памяти для выявления дефектов.

Формула изобретения

Оперативное запоминающее устройство с самоконтролем, содержащее блок памяти, адресные входы которого подключены к выходам счетчика, а управляющий вход - к первому входу блока управления, управляющий вход счетчика подключен ко второму выходу блока управления, элемент ИЛИ, входы к. торого подключены к вьаходам схемы сранения, а выход - ко входу блока управления, блок вентилей, управляющий вход крторого подключен к тре;тьему выходу блока управления, отличающееся тем, что, с целью повышения надежности контроля за счет локализации неисправностей, в него введены дешифратор, входы которого подключены к выходам счетчика, а выходы - ко входам блока вентилей, первый мультиплексор, первые входы которого подключены к выходам блока вентилей, вторые входы к выходам блока памяти, управляющий вход - к четвертому выходу блока управления, а третьи входы первого мультиплексора являются входами устройства, регистр, входы которого поключены к выходам первого мультиплексора, а выход - к информационным входам блока памяти, второй муль0типлексор, первые входы которого подключены к выходам регистра, вторые входы - к выходам дешифратора, а управляющий вход - к пятому входу блока управления, первый и второй

5 блоки индикации, входы которых подключены соответственно к выходам второго мультиплексора и схемы сравнения.

Источники информации,

0 принятые во внимание при экспертизе

1.Патент США 4075466, кл. 324-122, опублик. 1978.

2.Патент Великобритании № 1365057, кл. G 4 С, С 4 А,

5 опублик. 1974 (прототип).

12

N/

10

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1982 |

|

SU1051586A1 |

| Устройство для контроля блоковпОлупРОВОдНиКОВОй пАМяТи | 1979 |

|

SU799021A1 |

| Устройство для контроля блоков полупроводниковой памяти | 1979 |

|

SU875469A2 |

| Устройство для автоматического установления соединений и обмена сообщениями | 1989 |

|

SU1737760A1 |

| Коммутатор | 1989 |

|

SU1716622A2 |

| Устройство для контроля и диагностики цифровых блоков | 1985 |

|

SU1312580A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1120338A1 |

| Устройство для контроля оперативной памяти | 1985 |

|

SU1302325A1 |

Авторы

Даты

1981-02-28—Публикация

1979-06-15—Подача