записываются в контрольные разряды блоков памяти. При чтении аналогично формируются сигналы контрольного слова в формирователях 12-14, которые сравниваются в блоках 15-17 с сигналами четности, считанными из контрольных разрядов блоков Ц.,-,, памяти. Дешифратор 19 определяет номер отказавшего блока памяти, В устройстве исправляются в одном блоке

1

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам.

Цель изобретения - повьшение достоверности контроля устройства.

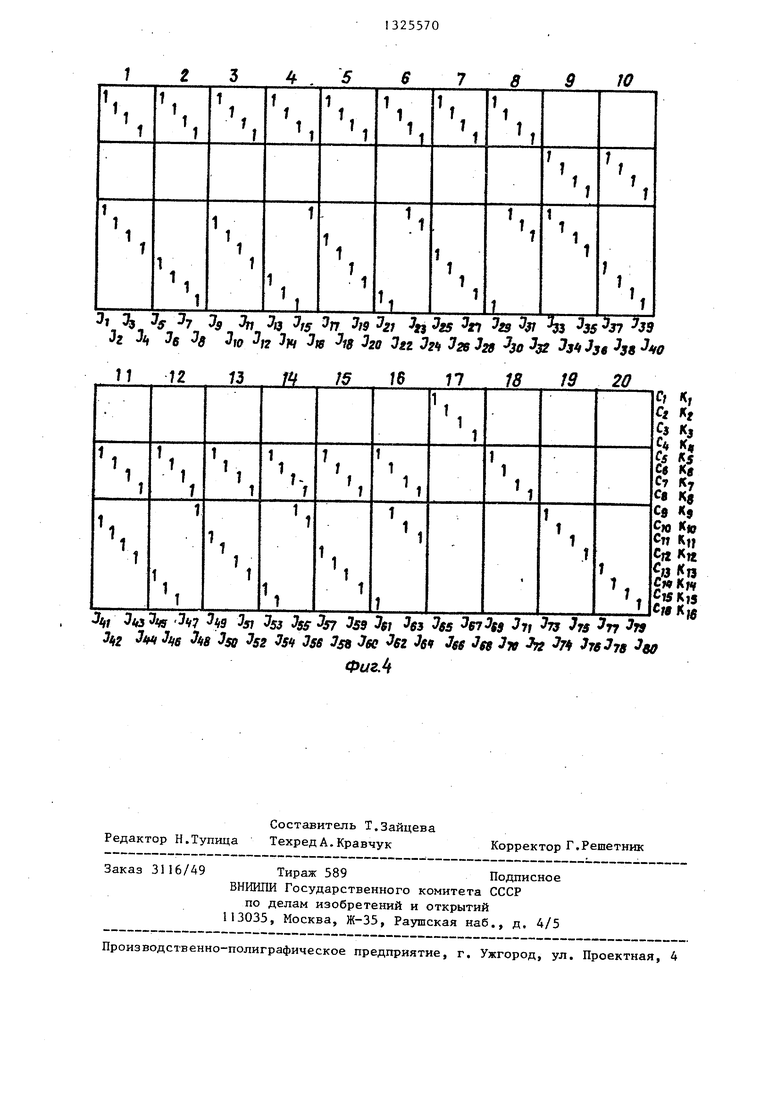

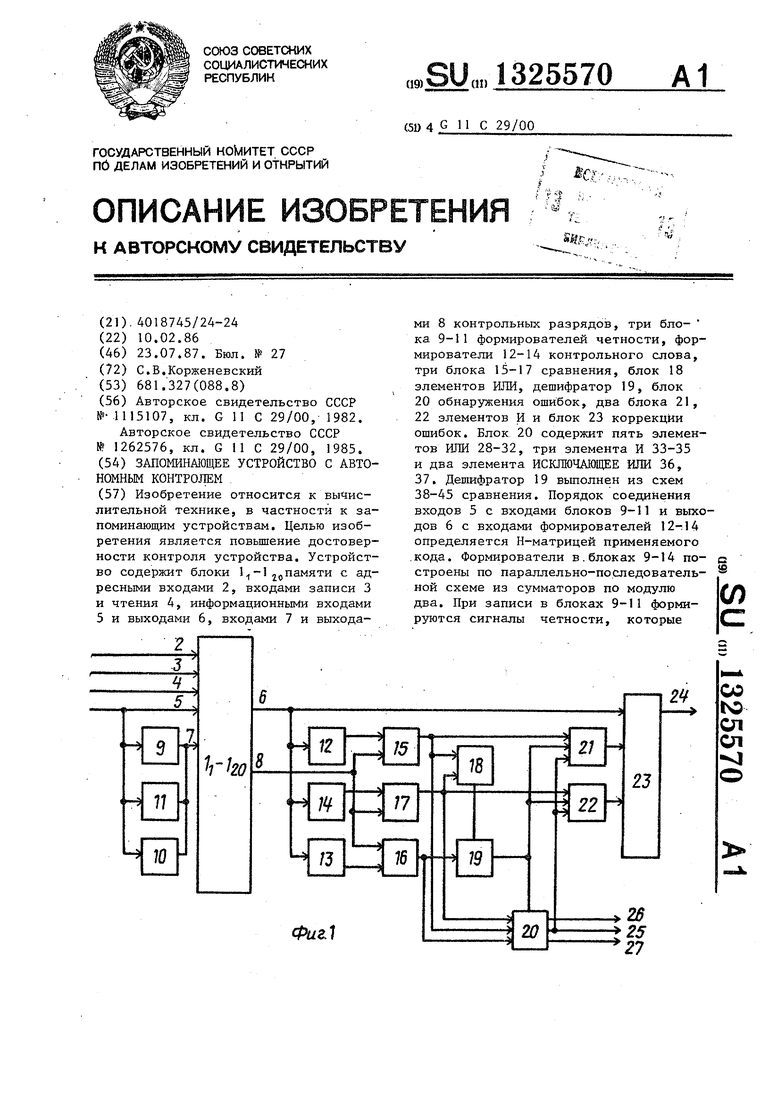

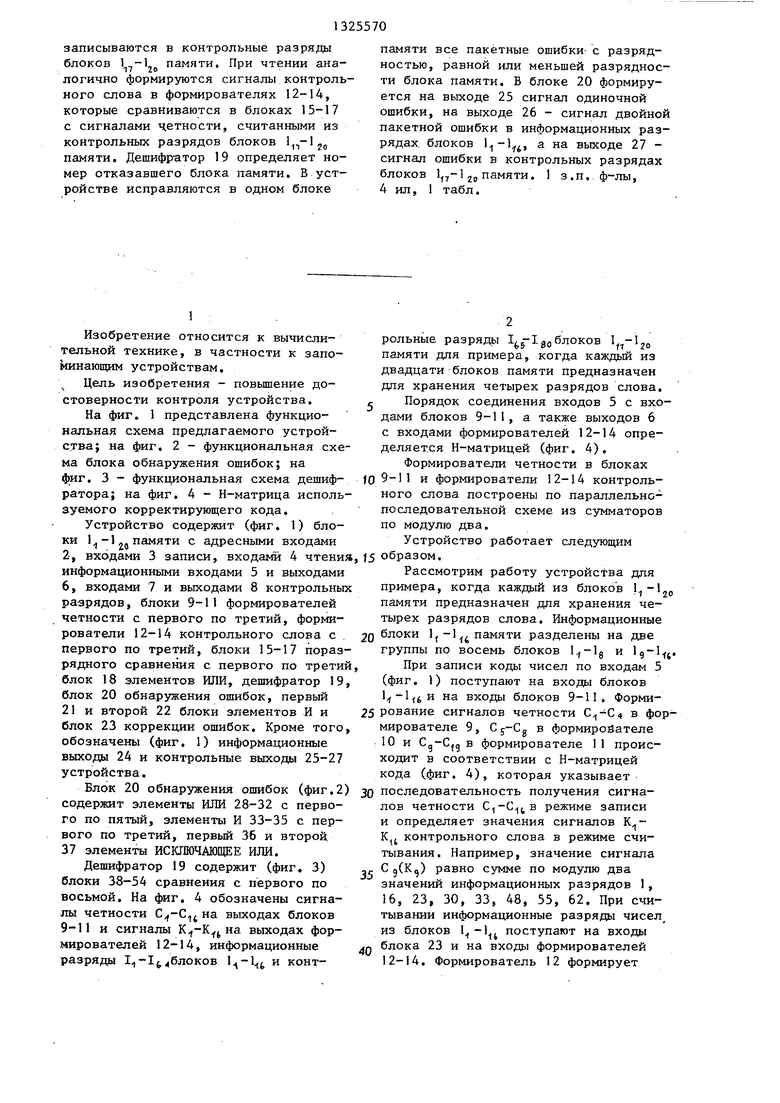

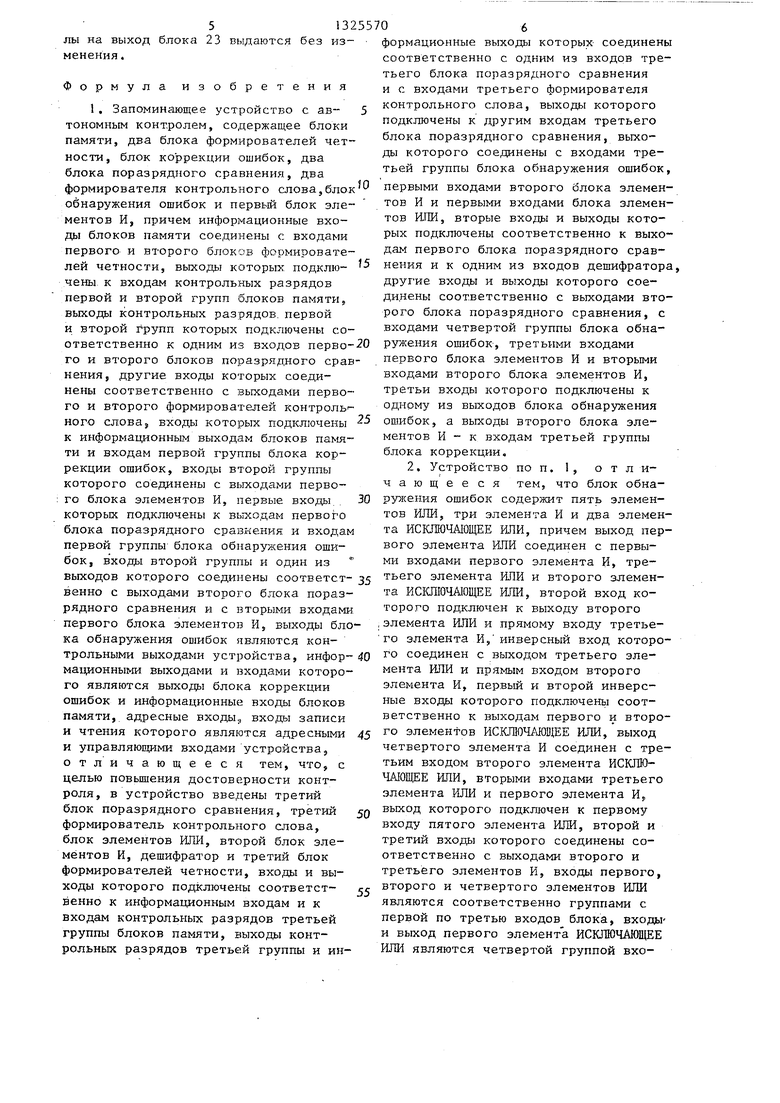

На фиг. 1 представлена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока обнаружения ошибок; на фиг. 3 - функциональная схема дешиф- ратора; на фиг. 4 - Н-матрица используемого корректирующего кода.

Устройство содержит (фиг. 1) блоки .jпамяти с адресными входами 2, входами 3 записи, входами 4 чтения информационными входами 5 и выходами 6, входами 7 и выходами 8 контрольных разрядов, блоки 9-11 формирователей четности с первого по третий, формирователи 12-14 контрольного слова с . первого по третий, блоки 15-17 поразрядного сравнения с первого по третий блок 18 элементов ИЛИ, дешифратор 19, блок 20 обнаружения ошибок, первый 21 и второй 22 блоки элементов И и блок 23 коррекции ошибок. Кроме того, обозначены (фиг. 1) информационные выходы 24 и контрольные выхода 25-27 устройства.

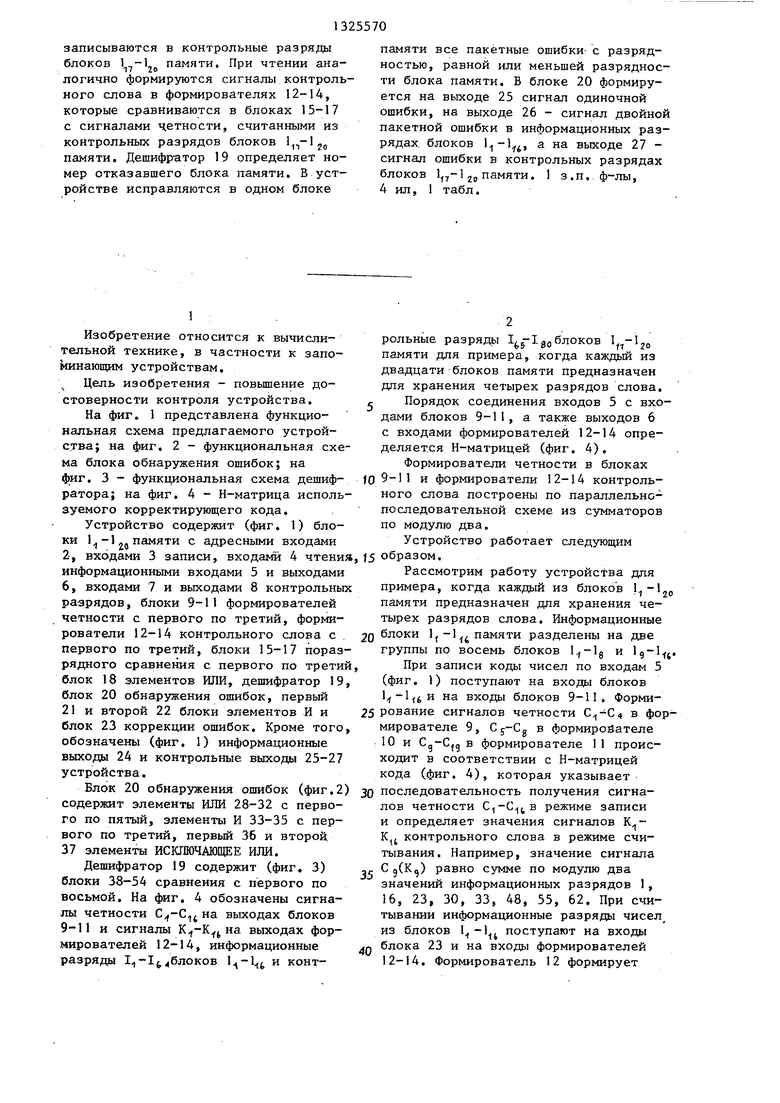

Блок 20 обнаружения ошибок (фиг.2) содержит элементы ИЛИ 28-32 с первого по пятый, элементы И 33-35 с первого по третий, первый 36 и второй 37 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ.

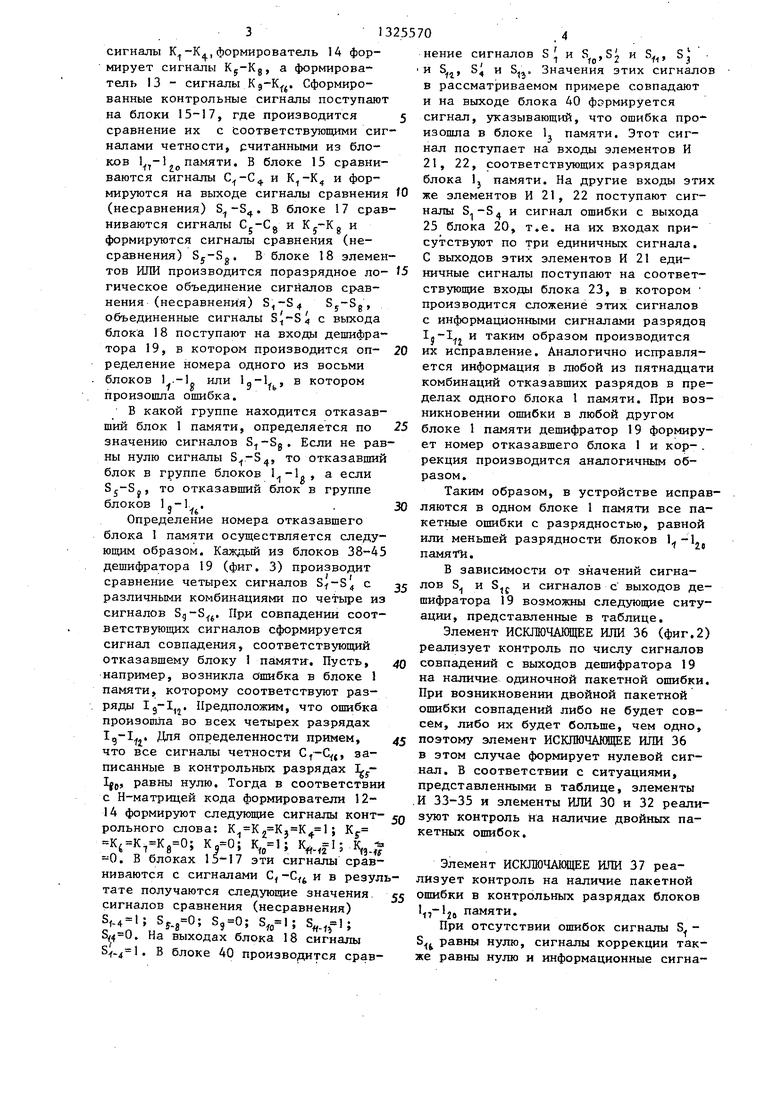

Дешифратор 19 содержит (фиг. 3) блоки 38-54 сравнения с первого по восьмой. На фиг. 4 обозначены сигналы четности ,j на выходах блоков 9- 11 и сигналы выходах формирователей 12-14, информационные разряды 1 -1 блоков конт

памяти все пакетные ошибки- с разрядностью, равной или меньшей разрядности блока памяти, В блоке 20 формируется на выходе 25 сигнал одиночной ошибки, на выходе 26 - сигнал двойной пакетной ошибки в информационных разрядах, блоков , а на выходе 27 - сигнал ошибки в контрольных разрядах блоков 25 памяти. 1 з.п. ф-лы, 4 ил, 1 табл.

0

5 0 5

о

п

5

рольные разряды I j-Igg блоков памяти для примера, когда каждый из двадцати блоков памяти предназначен для хранения четырех разрядов слова.

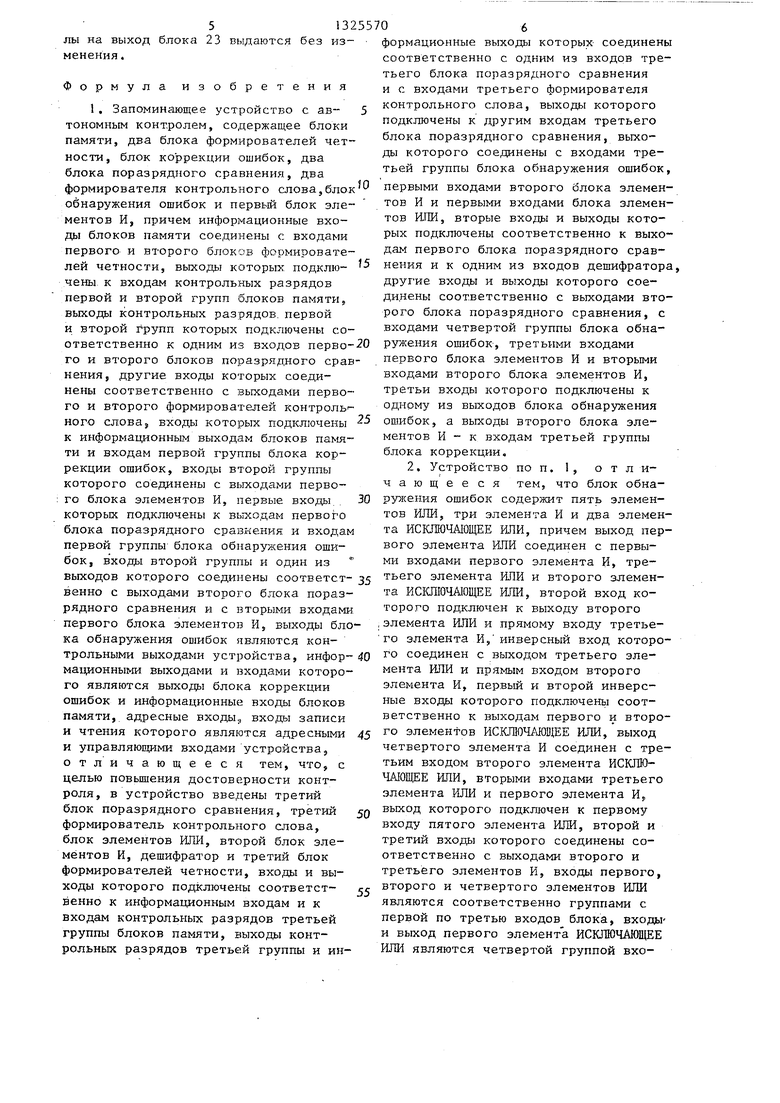

Порядок соединения входов 5 с входами блоков 9-11, а также выходов 6 с входами формирователей 12-14 определяется Н-матрицей (фиг. 4).

Формирователи четности в блоках 9-11 и формирователи 12-14 контрольного слова построены по параллельно- последовательной схеме из сумматоров по модулю два.

Устройство работает следующим образом.

Рассмотрим работу устройства для примера, когда каждый из блоков памяти предназначен для хранения четырех разрядов слова. Информационные блоки памяти разделены на две группы по восемь блоков и

При записи коды чисел по входам 5 (фиг. 1) поступают на входы блоков Ц-1,4 и на входы блоков 9-11, Формирование сигналов четности в формирователе 9, Cj-Cg в формирователе 10 и в формирователе 11 происходит в соответствии с Н-матрицей кода (фиг. 4), которая указывает последовательность получения сигналов четности режиме записи и определяет значения сигналов K.J контрольного слова в режиме считывания. Например, значение сигнала Cj(Kq) равно сумме по модулю два значений информационных разрядов 1, 16, 23, 30, 33, 48, 55, 62. При считывании информационные разряды чисел, из блоков 1 -1 поступают на входы блока 23 и на входы формирователей 12-14. Формирователь 12 формирует

сигналы ,формирователь 14 формирует сигналы Kj-Kg, а формирователь 13 - сигналы Kg-К, Сформированные контрольные сигналы поступают на блоки 15-17, где производится сравнение их с соответствующими сигналами четности, считанными из блоков памяти. В блоке 15 сравниваются сигналы и и формируются на выходе сигналы сравнения (несравнения) . В блоке 17 сравниваются сигналы Cj-Cg н Kj-Kg и формируются сигналы сравнения (несравнения)

В блоке 18 элеменнение сигналов S и S ,5 и S, Sj и Sjj, S и S, Значения этих сигналов в рассматриваемом примере совпадают и на выходе блока 40 формируется сигнал, указывающий, что ошибка про изошла в блоке 1, памяти. Этот сигнал поступает на входы элементов И 21, 22, соответствующих разрядам блока Ij памяти. На другие входы этих же элементов И 21, 22 поступают сигналы S,-S и сигнал ошибки с выхода 25 блока 20, т.е. на их входах присутствуют по три единичных сигнала, С выходов этих элементов И 21 едитов ИЛИ производится поразрядное ло- 5 ничные сигналы поступают на соответгическое объединение сигналов ср-ав- нения (несравнения) S,-S4 Sj-Sg, объединенные сигналы с выхода блока 18 поступают на входы дешифратора 19, в котором производится оп- 20 ределение номера одного из восьми

блоков , или 1д-Ь , в КОТОРОМ

произошла ошибка.

В какой группе находится отказавший блок 1 памяти, определяется по 25 значению сигналов . Если не равны нулю сигналы , то отказавший блок в группе блоков Ц-L, а если , то отказавший блок в группе блоков -.,. 30

Определение номера отказавшего блока 1 памяти осзпцествляется следующим образом. Каждый из блоков 38-43 дешифратора 19 (фиг. 3) производит сравнение четырех сигналов , с 5 различными комбинациями по четьфе из сигналов Sg -S. При совпадении соответствующих сигналов сформируется сигнал совпадения, соответствующий отказавшему блоку 1 памяти. Пусть, 40 например, возникла ошибка в блоке 1 памяти, которому соответствуют разряды . Предположим, что ошибка произошла во всех четырех разрядах

45

ствующие входы блока 23, в котором производится сложение этих сигналов с информационными сигнсшами разрядов

Г-и

и таким образом производится

l-lzo

Ig-I . Дпя определенности примем, что все сигналы четности , записанные в контрольных разрядах Ijj, равны нулю. Тогда в соответствии с Н-матрицей кода формирователи 12- 14 формируют следующие сигналы конт- 50 зуют контроль на наличие двойных паих исправление. Аналогично исправляется информация в любой из пятнадцати комбинаций отказавших разрядов в пределах одного блока 1 памяти. При возникновении ошибки в любой другом блоке 1 памяти дешифратор 19 формирует номер отказавшего блока I и кор- . рекция производится аналогичным образом.

Таким образом, в устройстве исправ ляются в одном блоке 1 памяти все пакетные ошибки с разрядностью, равной или меньшей разрядности блоков памяти.

В зависимости от значений сигналов S и и сигналов с выходов дешифратора 19 возможны следующие ситуации, представленные в таблице.

Элемент ИСКЛЮЧАШЩЕ ИЛИ 36 (фиг.2) реализует контроль по числу сигналов совпадений с выходов дешифратора 19 на наличие одиночной пакетной ошибки. При возникновении двойной пакетной ошибки совпадений либо не будет совсем, либо их будет больше, чем одно, поэтому элемент ИСКЛЮЧАКЩЕЕ ИЛИ 36 в этом случае формирует нулевой сигнал. В соответствии с ситуациями, представленными в таблице, элементы .И 33-35 и элементы ИЛИ 30 и 32 реалирольного слова: , ; Kj. K.r -VfT -0. В блоках 15-17 эти сигналы сравниваются с сигналами С, -С и в результате получаются следующие значения. 55 сигналов сравнения (несравнения) S,., l; Sy. S., l; . На выходах блока 18 сигналы 1 . В блоке 40 производится сравкетных ошибок.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 37 реализует контроль на наличие пакетной ошибки в контрольных разрядах блоков

памяти.

При отсутствии ошибок сигналы S. - 8 равны нулю, сигналы коррекции также равны нулю и информационные сигнанение сигналов S и S ,5 и S, Sj и Sjj, S и S, Значения этих сигналов в рассматриваемом примере совпадают и на выходе блока 40 формируется сигнал, указывающий, что ошибка про изошла в блоке 1, памяти. Этот сигнал поступает на входы элементов И 21, 22, соответствующих разрядам блока Ij памяти. На другие входы этих же элементов И 21, 22 поступают сигналы S,-S и сигнал ошибки с выхода 25 блока 20, т.е. на их входах присутствуют по три единичных сигнала, С выходов этих элементов И 21 едиствующие входы блока 23, в котором производится сложение этих сигналов с информационными сигнсшами разрядов

Г-и

и таким образом производится

l-lzo

зуют контроль на наличие двойных паих исправление. Аналогично исправляется информация в любой из пятнадцати комбинаций отказавших разрядов в пределах одного блока 1 памяти. При возникновении ошибки в любой другом блоке 1 памяти дешифратор 19 формирует номер отказавшего блока I и кор- . рекция производится аналогичным образом.

Таким образом, в устройстве исправляются в одном блоке 1 памяти все пакетные ошибки с разрядностью, равной или меньшей разрядности блоков памяти.

В зависимости от значений сигналов S и и сигналов с выходов дешифратора 19 возможны следующие ситуации, представленные в таблице.

Элемент ИСКЛЮЧАШЩЕ ИЛИ 36 (фиг.2) реализует контроль по числу сигналов совпадений с выходов дешифратора 19 на наличие одиночной пакетной ошибки. При возникновении двойной пакетной ошибки совпадений либо не будет совсем, либо их будет больше, чем одно, поэтому элемент ИСКЛЮЧАКЩЕЕ ИЛИ 36 в этом случае формирует нулевой сигнал. В соответствии с ситуациями, представленными в таблице, элементы .И 33-35 и элементы ИЛИ 30 и 32 реаликетных ошибок.

Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 37 реализует контроль на наличие пакетной ошибки в контрольных разрядах блоков

памяти.

При отсутствии ошибок сигналы S. - 8 равны нулю, сигналы коррекции также равны нулю и информационные сигна

j

выход блока 23 выдаются без из- я.

мула изобретения

Запоминающее устройство с ав- 5 ым контролем, содержащее блоки , два блока формирователей четблок коррекции ошибок, два поразрядного сравнения, два

Ш

фо со ть и ко по бл ды ть

п т т н .в п в т о м

формирователя контрольного слова,блок

обнаружения ошибок и первый блок элементов И, причем информационные входы блоков памяти соединены с входами первого и второго блоков формирователей четности, выходы которых нодклю- чены, к входам контрольных разрядов первой и второй групп блоков памяти, выходы контрольных разрядов, первой и второй групп которых подключены соответственно к одним из входов первого и второго блоков поразрядного сравнения, другие входы которых соединены соответственно с выходами первого и второго формирователей контроль - ного слова, входы которых подключены к информационным выходам блоков памяти и входам первой группы блока коррекции ошибок, входы второй группы которого соединены с выходами первого блока элементов И, первые входы , которых подключены к выходам первого блока поразрядного сравнения и входам первой группы блока обнаружения ошибок, в ходдз второй группы И один из выходов которого соединены соответст- венно с выходами второго блока поразрядного сравнения и с вторыми входами первого блока элементов И, выходы блока обнаружения ошибок являются контрольными выходами устройства, информационными выходами и входами которого являются выходы блока коррекции ошибок и информационные входы блоков памяти, адресные входы,, входы записи и чтения которого являются адресными и управляющими входами устройства, отличающееся тем, что, с целью повьшения достоверности контроля, в устройство введены третий блок поразрядного сравнения, третий формирователь контрольного слова, блок элементов Ш1И, второй блок элементов И, дешифратор и третий блок формирователей четности, входы и выходы которого подключены соответст- венно к информационным входам и к входам контрольных разрядов третьей группы блоков памяти, выходы контрольных разрядов третьей группы и ин

0 0 5 0 5 0

формационные выходы которых соединены соответственно с одним из входов третьего блока поразрядного сравнения и с входами третьего формирователя контрольного слова, выходы которого подключены к другим входам третьего блока поразрядного сравнения, выходы которого соединены с входами третьей группы блока обнаружения ошибок,

первыми входами второго блока элементов И и первыми входами блока элементов ИПИ, вторые входы и выходы которых подключены соответственно к выходам первого блока поразрядного сравнения и к одним из входов дешифратора, другие входы и выходы которого соединены соответственно с выходами второго блока поразрядного сравнения, с .входами четвертой группы блока обнаружения ошибок, третьими входами первого блока элементов И и вторыми входами второго блока элементов И, третьи входы которого подключены к одному из выходов блока обнаружения ошибок, а выходы второго блока элементов И - к входам третьей группы блока коррекции.

2. Устройство по п. 1, о т л и- чающее ся тем, что блок обнаружения ошибок содержит пять элементов ИЛИ, три элемента И и два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, причем выход первого элемента ИПИ соединен с первыми входами первого элемента И, третьего элемента ИЛИ и второго элемента ИСКЛЮЧАЮЩЕЕ ИЖ, второй вход которого подключен к выходу второго ,элемента ИЛИ и прямому входу третье- го элемента И, инверсный вход которого соединен с выходом третьего элемента ИЛИ и npHiyfljiM входом второго элемента И, первый и второй инверсные входы которого подключен ; соответственно к выходам первого и второго элементов ИС.КЛЮЧ/уЮЩЕЕ ИЛИ, выход четвертого элемента И соединен с третьим входом второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, вторыми входами третьего элемента ИЛИ и первого элемента Ир выход которого подключен к первому входу пятого элемента РИШ, второй и третий входы которого соединены соответственно с выходами второго и третьего элементов И, входы первого, второго и четвертого элементов ИЛИ являются соответственно группами с первой по третью входов блока, входы- и выход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются четвертой группой вхо713255708

дов и одним из выходов блока, други- ды пятого элемента ИЛИ и второго эле- ми выходами которого являются выхо- мента ИСКЛЮЧАЮ1ЦЕЕ ИЛИ.

О

О

О

ная ошибка или ошибка В контрольных разряД

Ошибка в КОНТ-. рольных разрядах

Ошибка в контрольных разрядах 1, . 5

1 5 7 S УО 15 % /5 г % З/ « j J5

г J Je Jfo Лг Jw J % 02it Угв 28 Jj Jj« Jje Jye П 1Z 13 т W 6 77 f5 / 2

W 57 % % % W % SS 57% Jtf % J w 77 Ли Лв 3sQ 3s2 J5« J5 58 бС 62 Js Jgg JfS Jyff - 00

Фиг,

Редактор Н.Тупица

Составитель Т.Зайцева Техред А. Кравчук

Заказ 3116/49 Тираж 589Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

8

W

Корректор Г,Решетник

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1987 |

|

SU1474746A2 |

| Запоминающее устройство с автономным контролем | 1985 |

|

SU1262576A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

| Модульное запоминающее устройство с коррекцией ошибок | 1985 |

|

SU1320848A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1096697A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302329A1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1091228A1 |

| Устройство для обнаружения и ис-пРАВлЕНия ОшибОК B блОКАХ ВычиСли-ТЕльНОй МАшиНы | 1979 |

|

SU840912A1 |

| Запоминающее устройство с авто-НОМНыМ КОНТРОлЕМ | 1979 |

|

SU809403A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Целью изобретения является повьшение достоверности контроля устройства. Устройство содержит блоки - naMHTVL с адресными входами 2, входами записи 3 и чтения 4, информационными входами 5 и выходами 6, входами 7 и выходами 8 контрольных разрядов, три бло- ка 9-11 формирователей четности, формирователи 12-14 контрольного слова, три блока 15-17 сравнения, блок 18 элементов ИЛИ, дешифратор 19, блок 20 обнаружения ошибок, два блока 21, 22 элементов И и блок 23 коррекции ошибок. Блок 20 содержит пять элементов ИЛИ 28-32, три элемента И 33-35 и два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 36, 37. Дешифратор 19 выполнен из схем 38-45 сравнения. Порядок соединения входов 5 с входами блоков 9-11 и выходов 6 с входами формирователей 12-14 определяется Н-матрицей применяемого .кода. Формирователи в.блоках 9-14 построены по параллельно-последовательной схеме из сумматоров по модулю два. При записи в блоках 9-11 формируются сигналы четности, которые i (Л Фиг. со ю ел ел

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1115107A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с автономным контролем | 1985 |

|

SU1262576A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-07-23—Публикация

1986-02-10—Подача