(54) ДЕШИФРИРУЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1981 |

|

SU1013942A1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПРОЦЕССОМ ДУГОВОЙ СВАРКИ НЕПЛАВЯЩИМСЯ ЭЛЕКТРОДОМ В СРЕДЕ ЗАЩИТНЫХ ГАЗОВ | 1988 |

|

SU1683244A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ ЭЛЕКТРОПРИВОДАМИ, ЭЛЕКТРОННЫМИ КЛЮЧАМИ И СИГНАЛИЗАЦИЕЙ | 2000 |

|

RU2174700C1 |

| Устройство для обмена данными в вычислительной системе | 1984 |

|

SU1251090A1 |

| Устройство управления установкой контроля и вырубки плоских мембран | 1985 |

|

SU1274923A1 |

| Устройство для передачи команд управления | 1977 |

|

SU690526A1 |

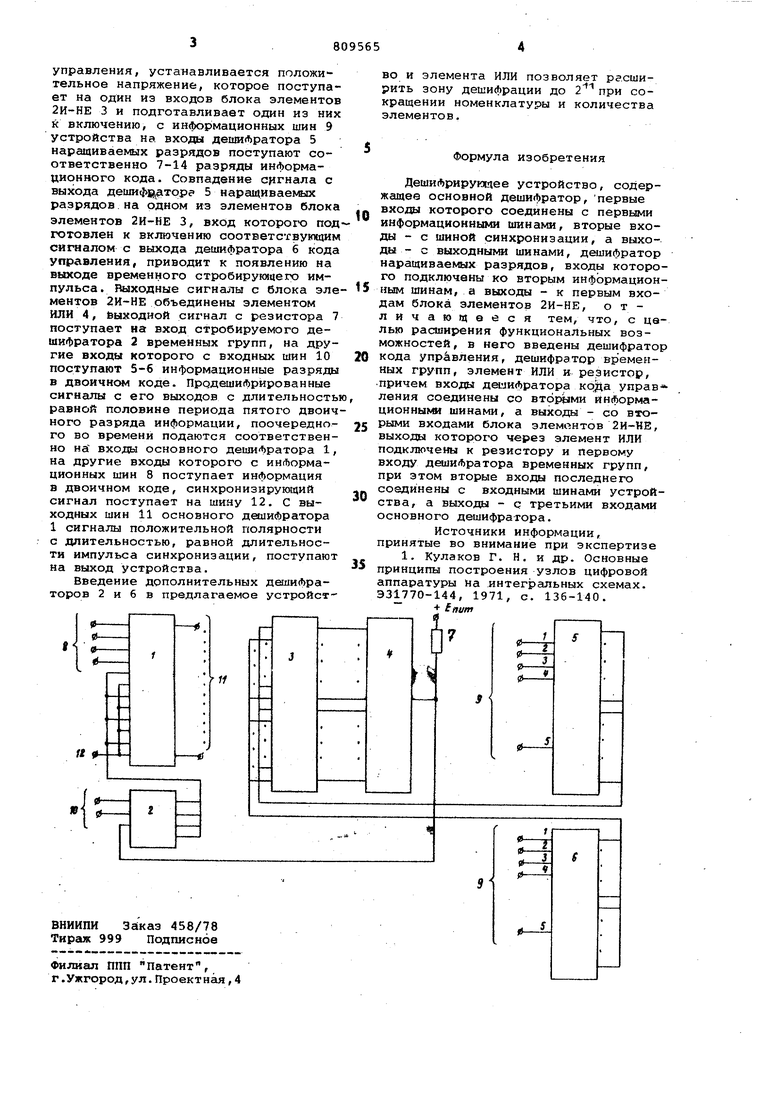

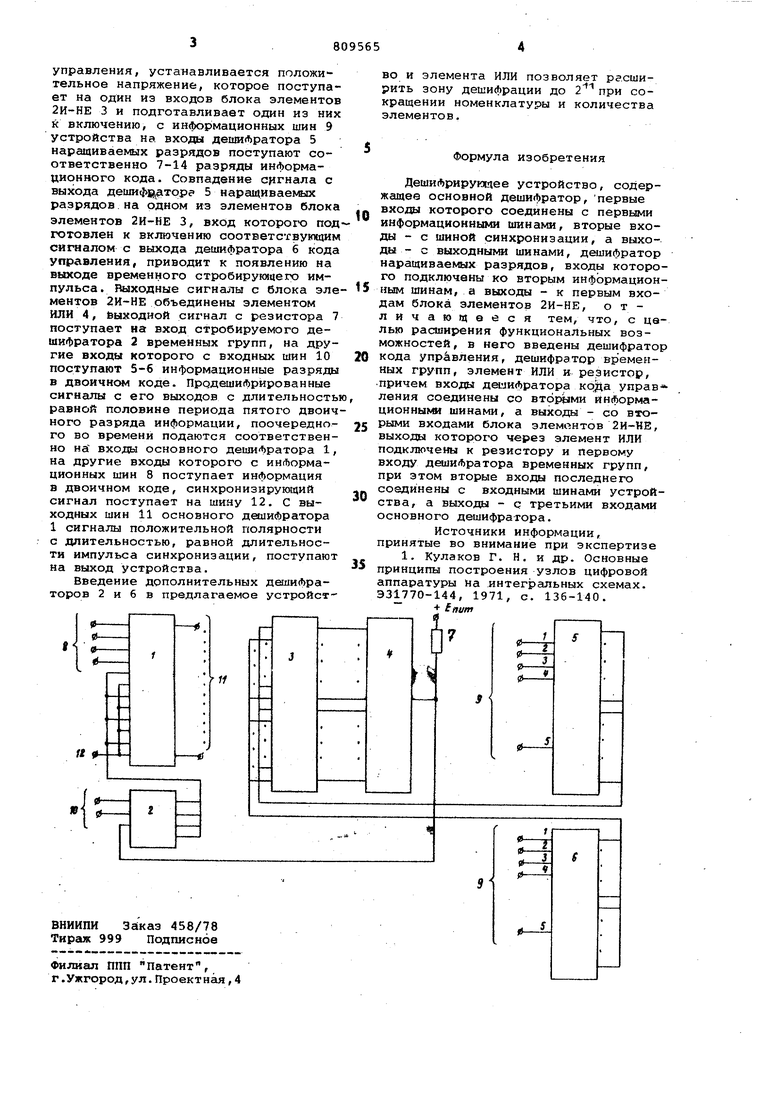

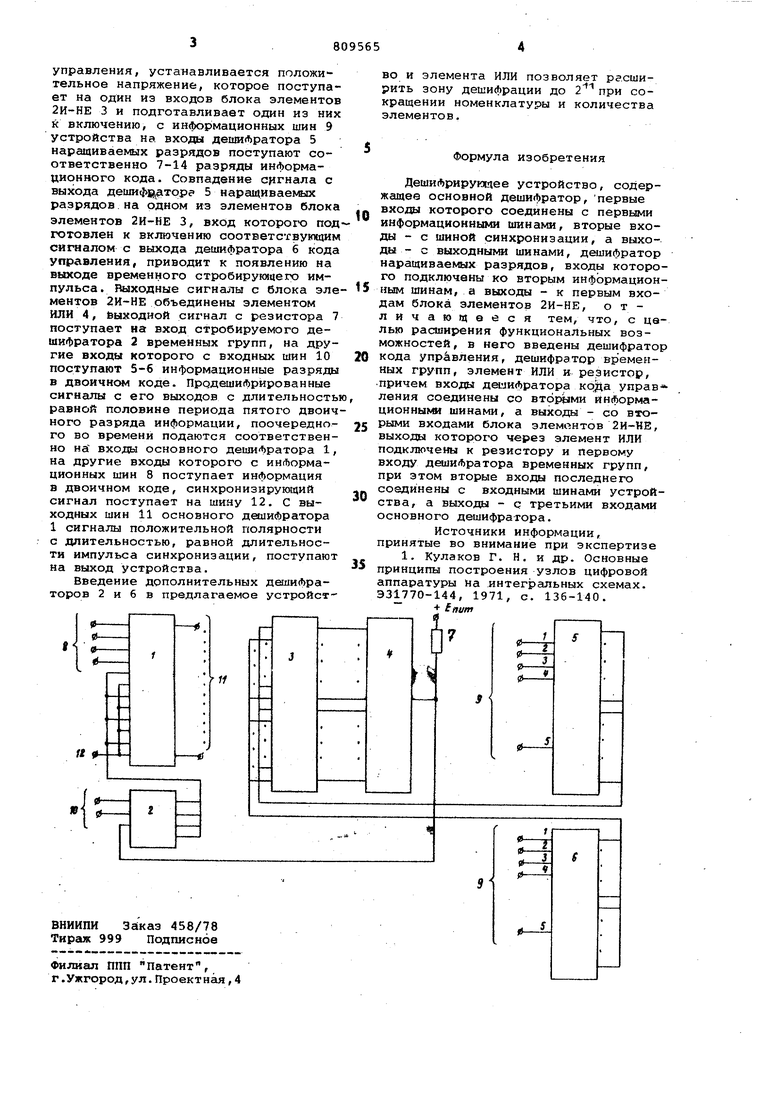

Изобретение относится к области вычислительной техники и может быть использовано в качестве формирователя многоразрядного адресного поля при обра щении к устройствам оперативной посто янной и перепрограммируемой памяти. Известны дешиЛрирующие устройства, содержащие основнрй дешифратор, дешиф ратор наращиваемых разрядов, блок, элементов 2И-НЕ и инверторы 1, Недостатком этого устройства является невозможность получения выходных сигналов в требуемых, произвольно выбранных и временных окнах в пределах всей зоны дешигбрации. Цель изобретения - расширение функ циональных возможностей. С этой целью в дшиифрируюгчее уст ройство, содержащее основной дешифратор, первые входы которого соединены с первыми информационными шинами, вторые входы - с шиной синхронизации, а выходы - с выходными шинами, дешифратор наращиваемых разрядов, входы которого подключены ко вторым информационным шинам, а выходил - к первым входам блока элементов 2И-НЕ, введены дешифратор кода управления, д€а1Шфратор временных групп, элемент ИЛИ и резистор, причем входы дешифратора кода управления соединены со вторыми ингЪормационными шинами, а выходы - со вторыми входами блока элементов 2И-НЕ выходы которого через элемент ИЛИ подключены к резистору и первому входу деа1И)ратора временных групп, при этом вторые входы последнего соединены с входными шинами устройства, а выходы - с третьими входами основного дешифратора. . На чертеже представлена функциональная схема устройства. В устройство входит дешиЛратор 1, соединенный с дешифратором 2 временных групп, блок элементов 2И-НЕ 3, элемент ИЛИ 4, дешифратор 5 HapaiUJSваемых разрядов, дешифратор 6 кода управления, резистор 7, информационные шины 8 и 9, входные шины 10, выходные шины 11 и шина 12 синхрони3 ации. Устройство работает следуготкм образом. С информационных шин 9 устройства на входы дешифратора 6 кода управления поступают соответственно 1-5 разряды кода управления. В зависимости от установленного значения кода управления на шинах 9 устройства на одном из выходов дешифратора 6 кода

управления, устанавливается положительное напряжение, которое поступает на один из входов блока элементов 2И-НЕ 3 и подготавливает один из них к включению, с информационных шин 9 устройства на входы дешифратора 5 наращиваемых разрядов поступают соответственно 7-14 разряды информационного кода, Совпадение сигнала с выхода дешифраторе 5 HapauiiHBaei iix разрядов.на одном из элементов блока элементов 2И-НЕ 3, вход которого подготовлен к включению соответствующим сигналом с выхода дешифратора 6 кода управления, приводит к появлению на выходе временного стробирукицего импульса . Выходные сигналы с блока элементов 2И-НЕ объединены элементом ИЛИ 4, Ьыходной сигнал с резистора 7 поступает на вход стробируемого дешифратора 2 временных групп, на другие входы которого с входных шин 10 поступают 5-6 информационные разряды в двоичном коде. Продешифрированные сигнгшы с его выходов с длительность равной половине периода пятого двоичного разряда информации, поочередного во времени подаются соответственно на входы основного дешифратора 1, на другие входы которого с инЛормационных шин 8 поступает информация в двоичном коде, синхронизирующий сигнал поступает на шияу 12, С выходных шин 11 основного д«ии ратора 1 сигналы положительной полярности с длительностью, равной длительности импульса синхронизации, поступают на выход устройства.

Введение дополнительных дешифраторов 2 и 6 в предлагаемое устройство и элемента ИЛИ позволяет расширить зону дешифрации до 2 при сокращении номенклатуры и количества элементов.

Формула изобретения

ДешиЛрируииее устройство, содержащее основной дешифратор, первые входал которого соединены с первыми информационными шинами, вторые входы - с шиной синхронизации, а выходы - с выходными шинами, дешифратор наращиваемых разрядов, входы которого подключены ко вторым информационным шинам, а выходы - к первым входам блока элементов 2И-НЕ, отличающееся тем, что, с целью расширения функциональных возможностей , в него введены дешифратор кода управления, дешифратор временных групп, элемент ИЛИ и резистор, причем входы дааифратора Kq;tia управ ления соединены со вторыми йнформациoнны вI шинами, а выходы - со вторыми входами блока элементов 2И-НЕ, выходы которого через элемент ИЛИ подключены к резистору и первому входу даииЛратора временных групп, при этом вторые входаа последнего соединены с входными шинами устройства, а выходы - q третьими входами основного дешифратора.

Источники информации, принятые во внимание при экспертизе

11

Г

Авторы

Даты

1981-02-28—Публикация

1979-01-09—Подача