1

Изобретение относится к вычислительной технике, а более конкретно к специализированным вычислительным машинам и предназначено для использования в составе универсальных ЭВМ, решающих логические защачи и производящие обработку массивов информации, а также в качестве учебных и справочных машин при обучении логике и построении силлогических, умозаключений.

Известна силлогистическая машина l, состоящая из шифраторов посылок (в виде таблиц), логических схем (в виде переключателей и коммутаций), дешифратора заключения (в виде коммутаций между ламелями переключателей) и блока отображения словес ного типа заключения (в виде ламп с номерами, которым по таблице соответствует словесные выражения типа заключения) , способная анализировать 16 силлогизмов с фундаментальными типами посылек,из которых только шесть являются информативными В остальных десяти, машина может дать заключения об отношении между крайними терминами силлогизма.

Силлогистическая машина Э. Беркли обладает рядом недостатков. В некоторых случаях она не дает информативного ответа. Например, ясно, что силлогизм Ни одно А не есть В Все В есть С Некоторые С не есть А является информативным. В то же время силлогистическая машина-прототип,

- не сумев построить этот силлогизм, выдает ответ: невозможно никакое заключение относительно А и С. Это происходит из-за ограниченности ее функциональных возможностей.

Доведение числа фундаментальных

5 типов посылок до 8, широко известных в настоящее время (в машине-прототипе используется только 6) , и использование современной технической базы, например электронных логических

0 элементов в микроминиатюрном исполнении, в принципе создает предпосылки для создания силлогистической машины, использующей технические решения, зало;; енные в машине-прото5 типе, однако, в этом случае она будет достаточно громоздкой и сложной. Кроме того, как показывает анализ существует большое количество силлогизмов (V 10) с нефундаментальными

0 типами посылок, как правило, трудно или вообще не выразимыми в естествен ном (человеческом языке, но встречаю щимися при решении логических задач или при обработке информации на ЭВМ Соответственно их реализация на машинах, таких, как машина Э. Беркли или использующих подобные технические решения, в принципе неосуществима из-за сверхогромной сложности и громоздкости, даже при использовании современной технической базы. Целью изобретения является расширение функциональных возможностей из вестной силлогистической машины за счет построения и проверки силлогизмов и автоматического анализа взаимо отношения между терминами и построения по двум посылкам заключения. Поставленная цель достигается за счет того, что в силлогистическую машину, содержащую шифраторы типа посылок, устройство управления, дешифраторы типа заключения и блок отображения введен блок силлогистического умножения, выходы дешифратора типа заключения соединены со входами блока отображения, причем блок силлогистического умножения содержит первый и второй регистры типа посылок, первый и второй блоки сравнения, семь дешифраторов, первый и второй двоичные счетчики, первую и вторую группы элементов И, два блока матриц элементов И, три двухвходовых элемента И, два коммут тора, элемент ИЛИ-ПЕ, четыре элемен та ИЛИ и регистр типа заключения. Выходы i -го шифратора типа посылок связаны с соответственными входами I -го регистра типа посылок, выходы I -го регистра типа посылок связаны с первой группой входов -i -го блока сравнения, вторая группа входов которого подключена к выходам i -го дешифратора, выходы которого связаны с соответствующими выходами i -го двоичного счетчика ( ) 1,2}. Управляющий вход первого счетчика соединен с выходом блока управления, а вы ходы 1 -го блока сравнения подключены соответственно к ) - м входам перво го двухвходового элемента И, выход которого соединен с первыми входами элементов И первой и второй групп и с первыми входами j -х дешифраторов (J 3,4,5,б). Второй и третий входы третьего дешифратора подключены к выходам первого и второго элементов И первой группы. Второй и третий входы четвертого дешифратора соединены с выходами третьего и чет вертого элементов И второй группы. Второй и третий входы пятого дешифра тора соединены с выходами первого и второго элементов И второй группы. Второй и третий входы шестого дешифратора соединены с выходами третьего и четвертого элементов И второй группы. Выходы третьего и шестого дешифраторов подсоединены ко входам первого блока матриц элементов И, выходы четвертого и пятого дешифраторов ко входам второго блока матриц элементов И. Первые управляющие выходы первого и второго блока матриц элементов И подключены к первому и второму входам второго элемента И, вторые управляющие выходы первого и второго блока матриц элементов И - к первому и вторюму входам третьего элемента И. информационные выходы первого блока матриц элементов И связаны со входами первого коммутатора, информационные выходы второго блока матрриц элементов И - со входами второго комг утатора, а дополнительные выходы j -X дешифраторов подсоединены ко входам элемента ИЛИ-НЕ. Первый, второй и третий информационные входы первого и второго блока матриц элементов И соединены с первой группой входов первого элемента ИЛИ. Первая группа выходов первого и второго коммутаторов соединена со второй группой входов первого элемента ИЛИ, третий, четвертый и пятый выходы первого и второго блока матриц элементов И соединены с первой группой входов второго элемента ИЛИ. Вторые группы выходов первого и второго коммутаторов подключены ко второй группе входов второго элемента ИЛИ. Второй, пятый и шестой выходы первого и второго блоков матриц элементов И соединены с первой группой входов третьего элемента ИЛИ. Третья группа выходов первого и второго KONwyтаторов соединена со второй группой входов третьего элемента ИЛИ. Седьмой и восьмой выходы первого и второго блока матриц элементов И соединены с первой группой входов четвертого элемента ИЛИ. Четвертая группа выходов первого и второго коммутаторов соединена со второй группой входов четвертого элемента ИЛИ. Выходы первого, второго, третьего и четвертого элементов ИЛИ связаны со входами седьмого дешифратора, выходы которого связаны с первой группой входов регистра типа заключения, вторая группа входов которого соединена с выходом элемента ИЛИ-НЕ. Второй управляющий выход первого блока матриц элементов И соединен с дополнительным входом первого и второго коммутаторов, а выходы второго и третьего элементов И подключены к первому и второму дополнительным входам регистра типа заключения. Принципиальное отличие машины от машины э; Беркли (наличие блока силлогистического умножения) приводит к положительному эффекту, состоящему в том, что, если для построения последней конструктор должен априорно знать типы выводов (заключений) силлогизмов, обусловленных, всеми возможнымисочетаниями типов посылок (как фундаментальными, так и Мефундаментальными), а их число .измеряется миллиардами ( , то предложенная машина автоматически вырабатывает все возможные типы заключений в зависимости от двух 16тиразрядных кодов посылок, не требуя этих знаний от конструктора; Кроме того она значительно проще известной для случая всевозможных типов посылок .

Перевод типа посылок с естественного языка в 16-ти разрядный двоичный код осуществляет либо ЭВМ, если силлогистическая машина работает в составе ЭВМ, либо сам человек (по особым несложным правилам с использованием диаграмм Венна), если силлогистическая машина работает с человеком (справочный или учебный вариант использования.

Преимущественно машины обеспечивается наличием блока силлогистического умножения, содержащего в своем составе регистры, cxeiubi сравнения, дешифраторы, счетчики, блоки матриц элементов И, логические блоки, элементы И, ИЛИ, ИЛИ-НЕ с соответствующими связями между ними.

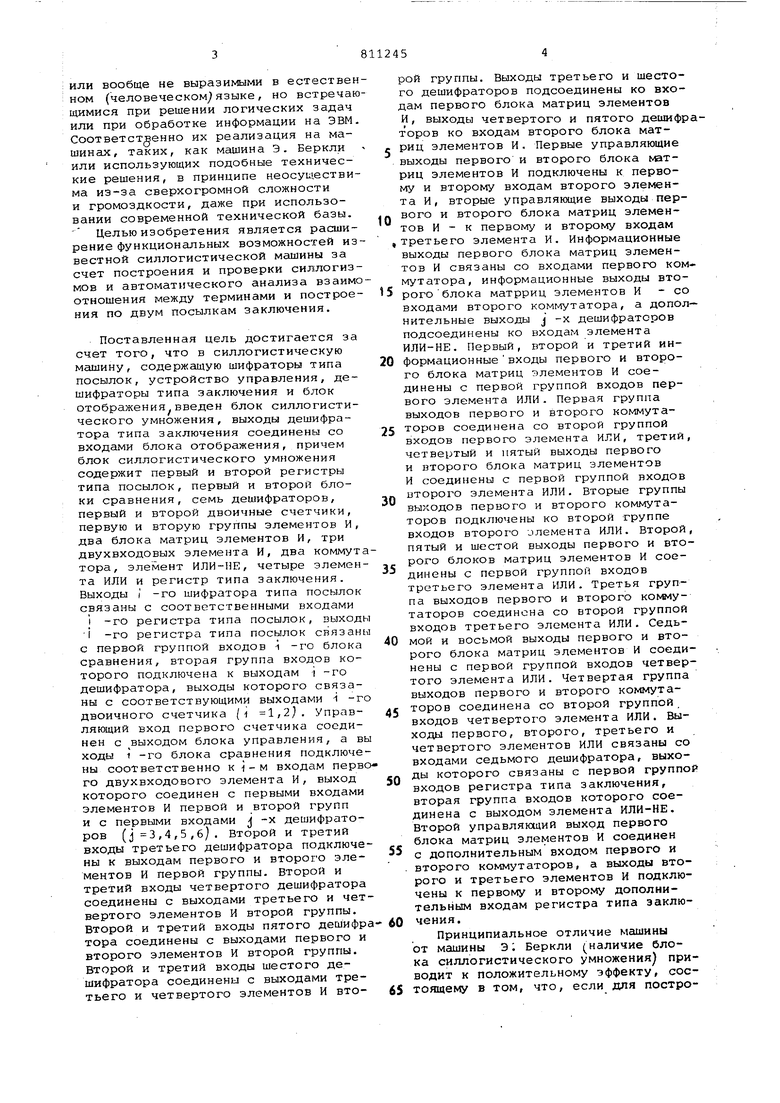

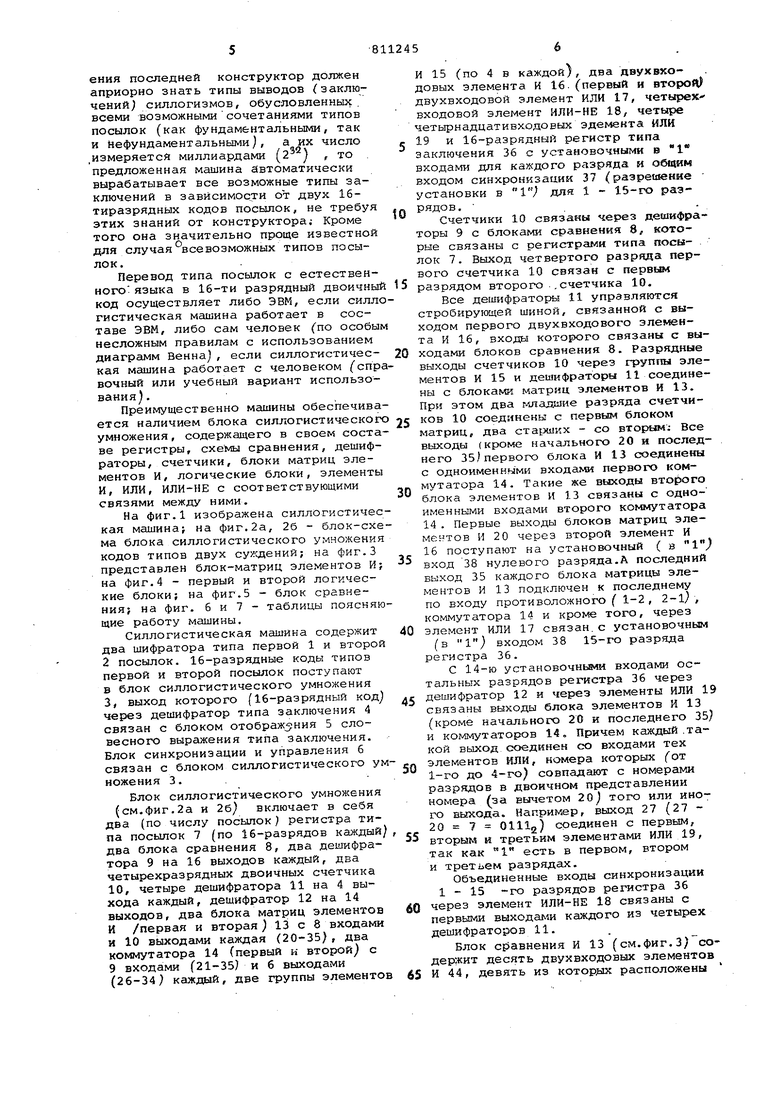

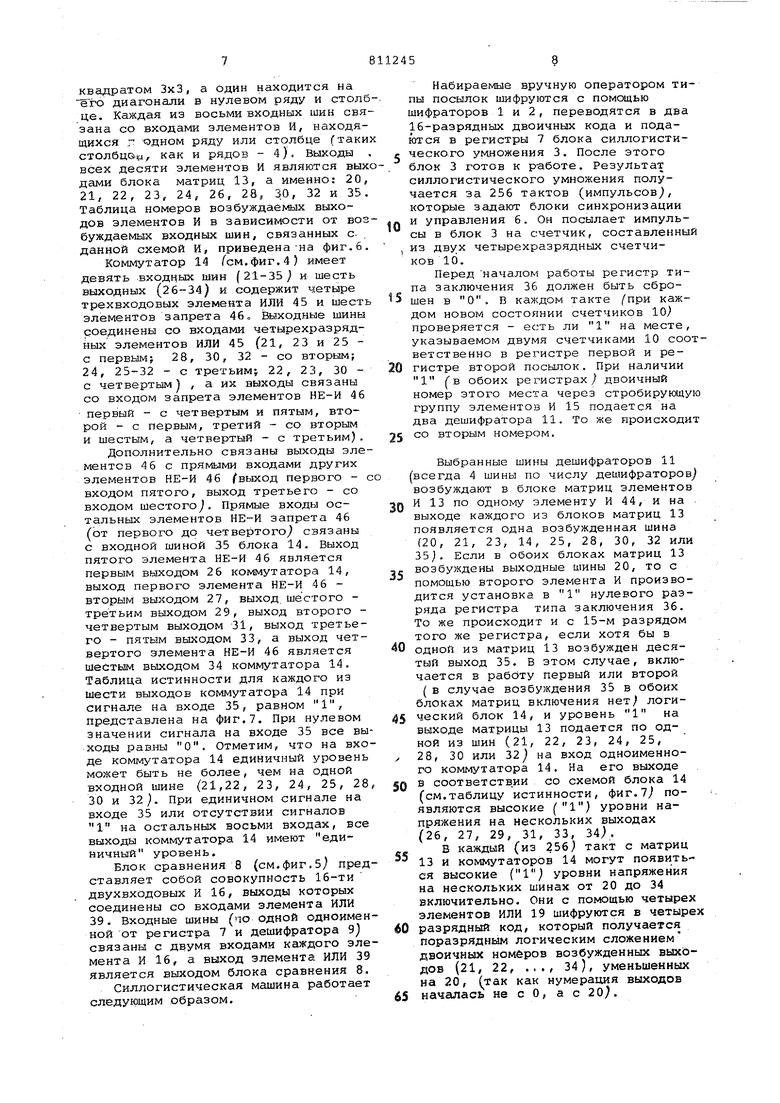

На фиг.1 изображена силлогистическая машина; на фиг.2а, 26 - блок-схема блока силлогистического умножения кодов типов двух сухэдений; на фиг.З представлен блок-матриц элементов И; на фиг.4 - первый и второй логические блоки; на фиг.5 - блок сравнения; на фиг. б и 7 - таблицы поясняющие работу машины.

Силлогистическая машина содержит два шифратора типа первой 1 и второй 2 посылок. 16-разрядные коды типов первой и второй посылок поступают в блок силлогистического умножения 3, выход которого (16-разрядный код) через дешифратор типа заключения 4 связан с блоком отображения 5 словесного выражения типа заключения. Блок синхронизации и управления 6 связан с блоком силлогистического умножения 3. .

Блок силлогистического умножения (см.фиг.2а и 2б) включает в себя два (по числу посылок) регистра типа посылок 7 (по 16-разрядов каждый) два блока сравнения 8, два дешифратора 9 на 16 выходов каждый, два четырехразрядных двоичных счетчика 10, четыре дешифратора 11 на 4 выхода каждый, дешифратор 12 на 14 выходов, два блока матриц элементов И /первая и вторая) 13 с 8 входами и 10 выходами каждая (20-35), два коммутатора 14 (первый и второй) с 9 входами (21-35 и б выходами (26-34) каждый, две группы элементов

и 15 (по 4 в каждой), два двухвходовых элемента И 16.(первый и второ двухвходовой элемент ИЛИ 17, четырех входовой элемент ИЛИ-НЕ 18, четыре четырнадцативходовых эдемекта ИЛИ

19и 16-разрядный регистр типа заключения 36 с установочными в 1 входами для каждого разряда и общим входом синхронизации 37 (разрешение установки в l для 1 - 15-го разрядов.

o

Счетчики 10 связаны через дешифраторы 9 с блоками сравнения 8, которые связаны с регистрами типа посылок 7. Выход четвертого разряда первого счетчика 10 связан с первым

5 разрядом второго . .счетчика 10.

Все дешифраторы 11 управляются стробирующей шиной, связанной с выходом первого двухвходового элемента И 16, входы которого связаны с вы0ходами блоков сравнения 8. Разрядные выходы счетчиков 10 через групгш элементов И 15 и дешифраторы 11 соединены с блоками матриц элементов И 13. При этом два шaдшиe разряда счетчиков 10 соединены с первым блоком

5 матриц, два - со вторым; Все выходы (кроме начального 20 и последнего 35,первого блока И 13 соединены с одноименными входами первого коммутатора 14. Такие же выходы ъторого

0 блока элементов И 13 связаны с одноименными входами второго коммутатора 14 . Первые выходы блоков матриц элементов И 20 через второй элемент И 16 поступают на установочный ( в 1

5 вход 38 нулевого разряда.А последний выход 35 каждого блока матрицы элементов И 13 подключен к последнему по входу противоложного ( 1-2, 2-1) , коммутатора 14 и кроме того, через

0 элемент ИЛИ 17 связан.с установочным

(в 1) входом 38 15-го разряда регистра 36.

С 14-ю установочньвди входами остальных разрядов регистра 36 через дешифратор 12 и через элементы ИЛИ 19

5 связаны выходы блока элементов И 13 (кроме начального 20 и последнего 35) и коммутаторов 14. Причем каждый.такой выход соединен со входами тех элементов ИЛИ, номера которых (от:

0 1-го до 4-го) совпадают с номерами разрядов в двоичном представлении номера (за вычетом 20) того или иного выхода. Например, выход 27 (27 20 7 Olllg) соединен с первым,

5 вторым и третьим элементами ИЛИ 19, так как 1 есть в первом, втором

и третьем разрядах.

Объединенные входы синхронизации 1-15 -го разрядов регистра 36 через элемент ИЛИ-НЕ 18 связаны с

0 первыми выходами каждого из четырех дешифраторов 11.

Блок сравнения И 13 (см.фиг.З) содер:кит десять двухвходовых элементов И 44, девять из которых расположены

5

квадратом 3x3, а один находится на его диагонали в нулевом ряду и столб-. це. Каждая из восьми входных шин связана со входами элементов И, находяихся ,г одном ряду или столбце (таких столбцов,- как и рядов - 4), Выходы , всех десяти элементов И являются выхог1ми блока матриц 13, а именно: 20, 21, 22, 23, 24, 26, 28, 30, 32 и 35. аблица номеров возбуждаемых выхоов элементов И в зависимости от возбуждаемых входных шин, связанных с. анной схемой И, приведена-на фиг.6.

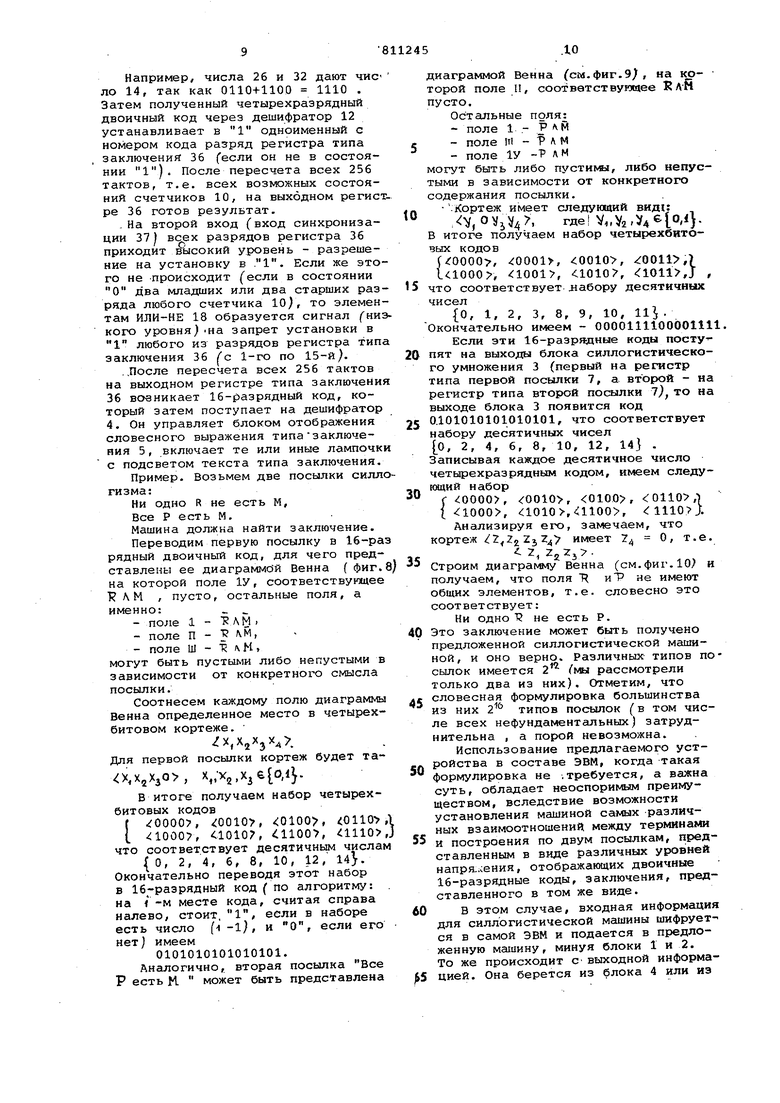

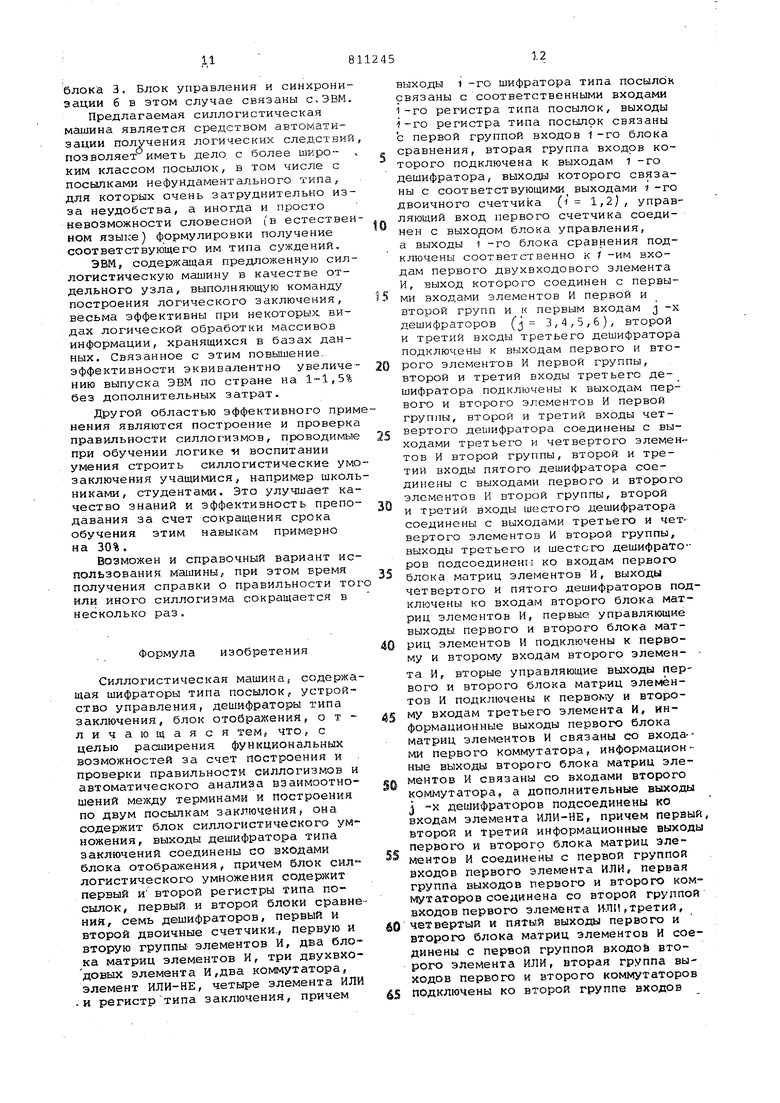

Коммутатор 14 . фиг. 4) имеет девять входных шик (21-35) и шесть выходных (26-34 и содержит четыре трехвходовых элемента ИЛИ 45 и шесть элементов запрета 46, Выходные шины соединены со входами четырехразрядных элементов ИЛИ 45 (21, 23 и 25 с первым; 28, 30, 32 - со вторьам; 24, 25-32 - с тpeтьим 22, 23, 30 с четвертым J , а их выходы связаны со входом запрета элементов НЕ-И 46 первый - с четвертым и пятым, второй - с первым, третий - со вторым и шестым, а четвертый - с третьим).

Дополнительно связаны выходы элементов 46с прямыми входами других элементов НЕ-И 46 выход первого - со входом пятого, выход третьего - со входом шестогоJ. Прямые входы остальных элементов НЕ-И запрета 46 (от первого до четвертого связаны с входной шиной 35 блока 14. Выход пятого элемента НЕ-И 46 является первым выходом 26 коммутатора 14, выход первого элемента НЕ-И 46 вторым выходом 27, выход шестого третьим выходом 29, выход второго четвертым выходом 31, выход третьего - пятым выходом 33, а выход четвертого элемента НЕ-И 46 является естым выходом 34 коммутатора 14. Таблица истинности для каждого из шести выходов коммутатора 14 при сигнале на входе 35, равном 1, представлена на фиг.7. При нулевом значении сигнала на входе 35 все выходы равны О, Отметим, что на входе коммутатора 14 единичный уровень может быть не более, чем на одной входной шине (21,22, 23, 24, 25, 28, 30 и 32). При единичном сигнале на входе 35 или отсутствии сигналов 1 на остальных восьми входах, все выходы коммутатора 14 имеют единичный уровень.

Блок сравнения 8 (см.фиг.5) представляет собой совокупность 16-ти двухвходовых и 16, выходы которых соединены со входами элемента ИЛИ 39. Входные шины (по одной одноименной от регистра 7 и дешифратора 9} связаны с двумя входами каждого элемента И 16, а выход элемента ИЛИ 39 является выходом блока сравнения 8.

Силлогистическая машина работает следу1рщим образом.

Набираемые вручную оператором типы посылок шифруются с помощью ифраторов 1 и 2, переводятся в два 16-раэрядных двоичных кода и подаются в регистры 7 блока силлогистического у «1ножения 3. После этого блок 3 готов к работе. Результат силлогистического умножения получается за 256 тактов (импульсов), которые задают блоки синхронизации

И управления 6. Он посылает импульсы в блок 3 на счетчик, составленный из двух четырехразрядньдх счетчиков 10.

Перед началом работы регистр типа заключения 36 должен быть сброшен в О, в каждом такте (при каждом новом состоянии счетчиков 10) проверяется - есть ли 1 на месте, указываемом двумя счетчиками 10 соответственно в регистре первой и регистре второй посылок. При наличии 1 (в обоих регистрах) двоичный номер этого места через стробирующую группу элементов И 15 подается на два дешифратора 11. То же происходит

со вторым номером.

Выбранные шины дешифраторов 11 всегда 4 шины по числу дешифраторов) возбуждают в блоке матриц элементов И 13 по Одному элементу И 44, и на выходе каждого из блоков матриц 13 появляется одна возбужденная шина (20, 21, 23, 14, 25, 28, 30, 32 или 35. Если в обоих блоках матриц 13

возбуждены выходные шины 20, то с

помощью второго элемента И производится установка в 1 нулевого разряда регистра типа заключения 36. То же происходит и с 15-м разрядом того же регистра, если хотя бы в

одной из матриц 13 возбужден десятый выход 35. В этом случае, включается в работу первый или второй ( в случае возбуждения 35 в обоих блоках матриц включения нет) логический блок 14, и уровень 1 на выходе матрицы 13 подается по одной из шин (21, 22, 23, 24, 25,

28, 30 или 32 на вход одноименного коммутатора 14. На его выходе

в соответствии со схемой блока 14 (см.таблицу истинности, фиг.7) появляются высокие (1) уровни напряжения на нескольких выходах (26, 27, 29, 31, 33, 34).

В каждый (из 256) такт с матриц

13 и коммутаторов 14 могут появиться высокие (1) уровни напряжения на нескольких шинах от 20 до 34 включительно. Они с помощью четырех элементов ИЛИ 19 шифруются в четырех

разрядный код, который получается поразрядным логическим сложением двоичных номбров возбужденных выходов (21, 22, ..., 34), уменьшенных на 20, (так как нумерация выходов

началась не с О, а с 20).

Например, числа 26 и 32 дают чис ло 14, так как 0110+1100 1110 . Затем полученный четырехразрядный двоичный код через дешифратор 12 устанавливает в 1 одноименный с номером кода разряд регистра типа заключения 36 Сесли он не в состоянии 1). После пересчета всех 256 тактов, т.е. всех возможных состояний счетчиков 10, на выходном регистре 36 готов результат.

. На второй вход (вход синхронизации 37 J всех разрядов регистра 36 приходит высокий уровень - разрешение на установку в 1. Если же этого не -происходит (если в состоянии О два младших или два старших разряда любого счетчика 10), то элементам ИЛИ-НЕ 18 образуется сигнал (низкого уровня на запрет установки в 1 любого из разрядов регистра типа заключения 36 (с 1-го по 15-й).

..После пересчета всех 256 тактов на выходном регистре типа заключения 36 возникает 16-разрядный код, который затем поступает на дешифратор 4. Он управляет блоком отображения словесного выражения типазаключения 5, включает те или иные лампочки с подсветом текста типа заключения.

Пример. Возьмем две посылки силлогизма:

Ни одно R не есть М, Все Р есть М.

Машина должка найти заключение. Переводим первую посылку в 16-раз рядный двоичный код, для чего представлены ее диаграммой Венна (фиг.8 на которой поле 1У, соответствуквдее 1 Л М , пусто, остальные поля, а именно:

-поле 1 - RAM .

-поле п - Р М,

-поле Ш - TR лМ,

могут быть пустыми либо непустыми в зависимости от конкретного смысла посылки.

Соотнесем каждому полю диаграммы Венна определенное место в четырехбитовом кортеже.

/X,X2XjX.

Для первой посылки кортеж будет таXX x XjO, .

в итоге получаем набор четырехбитовых кодов

f - 00007, jooio, :о1оо, ioiio,

{. 10007, 10107, illOO, 1110,J что соответствует десятичнцм числам

(О, 2,4, 6, 8, 10, 12, 14. Окончательно переводя этот набор в 16-раэрядный код ( по алгоритму: . на -М месте кода, считая справа налево, стоит, 1, еели в наборе есть число i -1), и О, если его нет) имеем

0101010101010101. Аналогично, вторая посылка Все Р есть К может быть представлена

диаграммой Венна (см.фиг.9), на которой поле П, COOT ват ствукидее К ЛИ

пусто.

Остальные поля:

-поле 1 - Р M

-поле iTi -ТАМ

-поле 1У -Р л М

могут быть либо пустимы, либо непустыми в зависимости от конкретного содержания посылки.

Кортеж имеет следующий види

o

XV, OVjV4. Д V,,V2V4 1o,l}. в итоге получаем набор четырехбитовых кодов

U0000, 0001, 0010, 0011,7 U1000, 1001, 1010, 1011,J ,

5 что соответствует дабору десятичных чисел

(О, 1, 2, 3, 8, 9, 10, 11 . Окончательно имеем - 0000111100001111.

Если эти 16-разрядные коды посту0пят на выходы блока силлогистического умножения 3 (первый на регистр типа первой посылки 7, а второй - на регистр типа второй посылки 7), то на выходе блока 3 появится код 0.101010101010101, что соответствует

5 набору десятичных чисел О, 2, 4, 6, 8, 10, 12, 14} . Записывая каждое десятичное число четырехразрядным кодом, имеем следующий набор

0

( ;оооо, гоо1о, 0100, :oiio,i

1 1000, 1010,-illOO, :illO).

Анализируя его, замечаем, что кортеж 2зг имеет 2 О, т.е.

2, ZjZj.

5

Строим диагра1УВи1у Венна (см.фиг.Ю и получаем, что поля R иР не имеют общих элементов, т.е. словесно это соответствует:

Ни одно Т не есть Р.

0 Это заключение может быть получено предложенной силлогистической машиной, и оно верно. Различных типов посылок имеется 2 мы рассмотрели только два из них). Отметим, что словесная формулировка большинства

5 из них 2 типов посылок (в том числе всех нефундаментальных) затруднительна I а порой невозможна.

Использование предлагаемого устройства в составе ЭВМ, когда такая

0 формулировка Не .требуется, а важна суть, обладает неоспоримым преимуществом, вследствие возможности установления машиной самых различных взаимоотношений между терминами

5 и построения по двум посылкам, представленным в виде различных уровней напря..;ения, отображающих двоичные 16-разрядные коды, заключения, представленного в том же виде.

В этом случае, входная информация

0 для силлогистической машины шифрует ся в самой ЭВМ и подается в предложенную машину, минуя блоки 1 и 2. То же происходит С выходной информацией. Она берется из блока 4 или из

S блока 3. Блок управления и синхрони зации 6 в этом случае связаны с.ЭВМ Предлагаемая силлогистическая машина является средством автоматизации получения логических следстви позволяет иметь дело с более широким классом посылок, в том числе с посылками нефундаменталького типа, для которых очень затруднительно из за неудобства, а иногда и просто невозможности словесной (в ном языке) формулировки получение соответствующего им типа суждений. ЭВМ, содержащая предложенную сил логистическую машину в качестве отдельного узла, выполняющую команду построения логического заключения, весьма эффективны при некоторых видах логической обработки массивов информации, хранящихся в базах данных. Связанное с этим повышение, эффективности эквивалентно увеличе нию выпуска ЭВМ по стране на 1-1,5% без дополнительных затрат. Другой областью эффективного при нения являются построение и проверк правильности силлогизмов, проводимы при обучении логике м воспитании умения строить силлогистические ум заключения учащимися, например школ никами, студентами. Это улучшает ка чество знаний и эффективность препо давания за счет сокращения срока обучения этим навыкам примерно на 30%. Возможен и справочный вариант ис пользования мс1шиныг при этом время получения справки о правильности то или иного силлогизма сокращается в несколько раз. Формула изобретения Силлогистическая машинаf содержа щая шифраторы типа посылок, устройство управления, дешифраторы типа заключения, блок отображения о т личающаяся теМе что, с целью расширения функциональных возможностей за счет построения и проверки правильности силлогизмов и автоматического анализа вэаимоотношений между терминами и построений по двум посылкам заключения, она содержит блок силлогистического умножения, выходы дешифратора типа заключений соединены со входами блока отобр 1жения, причем блок силлогистического умножения содержит первый и второй регистры типа, посылок, первый и второй блоки сравне ний, семь дешифраторов, первый и второй двоичные счетчики., первую и вторую группы элементов И, два блока матриц элементов И, три двухвходовых элемента И,два коммутатора, элемент ИЛИ-НЕ, четыре элемента ИЛИ -И регистр типа заключения, причем выходы 1 -го шифратора типа посылок связаны с соответственными входами 1-го регистра типа посылок, выходы -) -го регистра типа посылок связаны с первой группой входов 1 -го блока сравнения, вторая группа входов которого подключена к выходам i -го дешифратора, выходы которого связаны с соответствующими выходами i-го двоичного счетчика (i 1,2), управляющий вход первого счетчика соединен с выхором блока управления, а выходы 1 -го блока сравнения подключены соответственно к 7 -им входам первого двухвходового элемента И, выход которого соединен с первыми входами элементов И первой и второй групп и к первым входам j -х дешифраторов (j 3,4,5,6), второй и третий входы третьего дешифратора подключены к выходам первого и второго элементов И первой группы, второй и третий входы третьего дешифратора подключены к выходам первого и второго элементов И первой группы, второй и третий входы четвертого дешифратора соединены с выходами третьего и четвертого элементов И второй группы, второй и третий входы пятого дешифратора соединены с выходами первого и второго элементов И второй группы, второй и третий входы шестого дешифратора соединены с выходами третьего и четвертого элементов И второй группы, выходы третьего и шестого дешифраторов подсоединена ко входам первого блока матриц элементов И, выходы четвертого и пятого дешифраторов подключены ко входам второго блока матриц элементов И, первые управляющие выходы первого и второго блока матриц элементов И подключены к первому и второму входам второго элемен- та И, вторые управляющие выходы первого и второго блока матриц элементов И подключены к nepaoNiy и второму входам третьего элемента И, информационные выходы первого блока матриц элементов И связаны со входа- ми первого коммутатора, информационные выходы второго блока матриц элементов И связаны со входами второго коммутатора, а дополнительные выходы j -X дешифраторов подсоединены ко входам элемента ИЛИ-НЕ причем первый, второй и третий информационные выходы первого и второго блока матриц элементов И соединены с первой группой входов первого элемента ИЛИ, первая группа выходов nepsoro и второго коммутаторов соединена со второй группой входов первого элемента ИЛИ,третий, четвертый и пятый выходы первого и второго блока матриц элементов И соединены с первой группой входой второго элемента ИЛИ, вторая группа выходов первого и второго коммутаторов подключены ко второй группе входов

второго элемента ИЛИ, второй, пятый, шестой выходы первого и,второгоблоков матриц элементов И соединены с первой группой входов третьего элемента ИЛИ, третья группа выходов первого и второго коммутаторов соединены со второй группой входов третьего элемента ИЛИ, седьмой и восьмой выходы первого и второго блока матриц элементов И соединены с первой группой входов четвертого элемента ИЛИ, четвертая группа выходов первого и второго.коммутаторов соединена со бторой группой входов четвертого элемента ИЛИ, выходы первого, второго, третьего и четвертого элемента ИЛИ связаны со входами

седьмого дешифратора, выходы которого связаны с первой; группой входов регистра типа заключения, вторая группа входов которого соединена с выходом элемента ИЛИ-НЕ, а вто- рой управляющий выход первого блока матриц элементов И соединен с дополнительными входами первого и второго коммутаторов, выходы второго и третьего элементов И подключены к первому и второму дополнительным вхо0дам регистра типа заключения. Источники информации, принятые во внимание при экспертизе

1. Э. Беркли. Символическая логика и разумные машины. М., Мир, 1961,

5 стр. 127-13Ь ( пpoтoтип.

| название | год | авторы | номер документа |

|---|---|---|---|

| Силлогистическая машина | 1981 |

|

SU1013961A2 |

| Множительно-сдвиговое устройство | 1978 |

|

SU805307A1 |

| Устройство для обучения основам вычислительнй техники | 1981 |

|

SU1005156A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1982 |

|

SU1133593A1 |

| Устройство для преобразования временных интервалов в двоичный код | 1980 |

|

SU945980A1 |

| Устройство для определения времени проведения технического обслуживания системы | 1987 |

|

SU1571633A1 |

| Устройство управления установкой контроля и вырубки плоских мембран | 1985 |

|

SU1274923A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1246091A1 |

| ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С АППАРАТНО-ПРОГРАММНОЙ РЕАЛИЗАЦИЕЙ ФУНКЦИЙ ОТКАЗОУСТОЙЧИВОСТИ И ДИНАМИЧЕСКОЙ РЕКОНФИГУРАЦИИ | 2010 |

|

RU2455681C1 |

| Специализированный процессор обработки данных | 1982 |

|

SU1062715A1 |

фиг }

фууу уууууууфууи

у у у V VVV

Фиг. Za

Фиг 25

риг.

Авторы

Даты

1981-03-07—Публикация

1977-12-20—Подача