1

Изобретение относится к вычислительной технике и может быть использовано в системах контроля цифровых узлов ЭВМ.

Известно устройство для защиты выходного формирователя логических уровней микросхем типа ТТЛ 1, содержащее элемент защиты по току - ограничительное сопротивление в коллекторной цепи транзистора, формирующего уровень логической единицы микросхемы.

Недостатком устройства является отсутствие защиты выходного формирователя при длительном воздействии перегрузки по току (более одной секунды), в результате чего формирователь выходит из строя.

Наиболее близким по технической сущности к изобретению является устройство для защиты усилителя-формирователя по току, обеспечивающее защиту выходных цепей усилителя от короткого замыкания 2.

Это устройство содержит чувствительный элемент, реагирующий на приращение выходного тока формирователя и триггер Шмидта, образующие схему контроля выхода формирователя по току, и усилительформирователь, включающий транформаторы и тиристорную схему защиты с механической разблокировкой. Формирователь имеет информационный вход от источника

2

сигналов и управляющий вход от триггера Шмидта.

Однако такое устройство не позволяет обеспечить защиту усилителя-формирователя от попадания напряжения выше и ниже допустимого на его выход и быструю разблокировку защиты после срабатывания, что делает невозможным его использование в системах контроля цифровых узлов, работающих на высоких частотах выдачи входных воздействий от источников сигналов и в условиях попадания различных напряжений на выход формирователя.

Целью изобретения является повышение надежности и быстродействия работы устройства защиты формирователя выходных логических уровней систем контроля цифровых узлов.

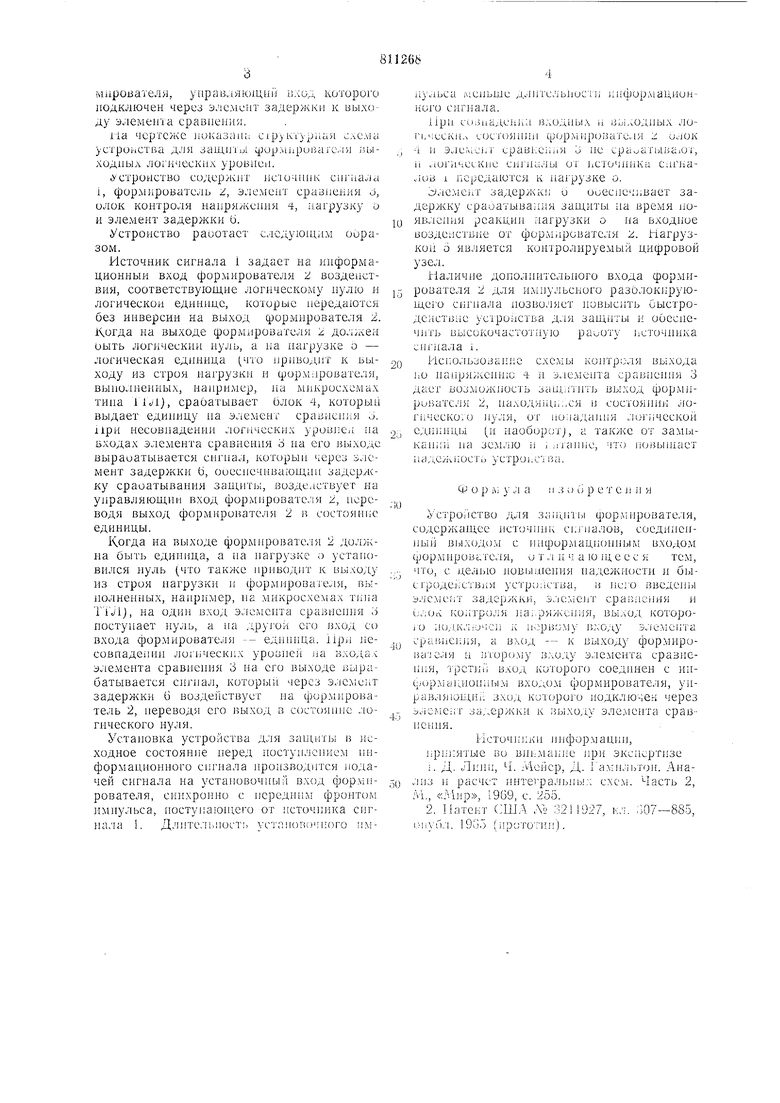

Поставленная цель достигается тем, что в устройство для защиты формирователя, содержащее источник сигналов, соединенный выходом с информационным входом формирователя, введены элемент задержки, элемент сравнения и блок контроля напряжения, выход которого подключен к первому входу элемента сравнения, а вход - к выходу формирователя и второму входу элемента сравнения, третий вход которого соединен с информационным входом формирователя, управляющий вход которого подключен через элемент задержки к выходу элемента сравнения. ria чертеже показана структурная схе.ма устройства для защнты формпрователя выходных логических уровнен. Устройство содержит нсточник снгнала 1, формирователь 2, элемент сравнения б, олок контроля нанряжения 4, нагрузку D и элемент задержки б. Устройство раоотает следующим образом. Источник сигнала 1 задает на информационный вход формирователя 2 воздействия, соответствующие логическому нулю и логической еднннце, которые нередаются без инверсии на выход формирователя 2. Когда на выходе формирователя 2 должен оыть логический иуль, а на нагрузке о - логическая единица (что нриводнт к выходу нз строя нагрузки и формирователя, вынолиенных, нанрнмер, на микросхемах типа 11Л), срабатывает блок 4, который выдает единицу на элемент сравнения ;j. При несовнадении логических ypoBHeii на входах элемента сравнения 6 на его выходе выраоатывается сигнал, который через элемент задержки Ь, оОесиечивающиН задержку сраоатывания защиты, воздействует на унравляющиИ вход формирователя 2, нереводя выход формирователя 2 в состоян С единицы. Когда на выходе формирователя 2 быть единица, а па нагрузке 5 установился нуль (что также приводит к выходу из строя нагрузки и формирователя, выиолненных, например, на микросхемах типа ТТЛ), на один вход элемента сравнення о ностунает нуль, а на другой его вход со входа формирователя - единица. При несовнадении логических уровней на входах элемента сравнення 3 на его выходе вырабатывается сигнал, который через элемент задержки 6 воздействует на формирователь 2, переводя его выход в состояние логического нуля. Установка устройства для защиты в исходное состояние неред поступлением информационного снгнала производится подачей сигнала на установочный вход формпрователя, синхронно с передним фронтом импульса, поступающего от источника сигнала 1. Длптельпость установочного ммпульса меньше длительности ннфор.мациониого снгнала. При сов11адепии в.кодных л выходных логических состояннн формировате чя 2 блок 4 и элемент сравнения о не сраиатывают, п о1огические сигналы от источника ciirnaлов i нередаются к нагрузке 5. Элемент задержкн б обеспечивает задержку срабатывания защиты на время появления реакции иагрузки о на входное воздействие от формирователя 2. Нагрузкой о является контролируемый цифровой узел. Наличие донолнительного входа формирователя 2 для имнульсного разблокирующего снгнала позволяет новысить быстродействие устройства для защиты и обеснечить высокочастотную работу источника сигнала 1. Использование схемы контроля выхода по нанряжению 4 и элемента сравнения 3 дает возможность защитить выход формирователя 2, находящи 1ся в состоянии логического нуля, от попадания логической единнцы (и наоборот), а также от замыканий на землю и питание, что повышает надежиость устройства. Форы у л а изобретения Устройство для защпты формирователя, содержащее источник сигналов, соединенный выходом с информационным входом формирователя, отличающееся тем, что, с целью новышения надежности и быстродействия устройства, в него введены элемент задержки, элемент сравнения и илок контроля напряжения, выход которого подключен к первому входу элемента сравнення, а вход - к выходу формирователя и второму входу элемента сравнения, третий вход которого соединен с информационным входом формирователя, унравляющий вход которого нодключен через элемент задержки к выходу элемента сравнения.: Источники информации, принятые во вниманне нри экспертизе 1.Д. Линн, Ч. Мейер, Д. Гамильтон. Анализ и расчет интегральных схе.м. Часть 2, М., «Мир, 1969, с. 255. 2.Патепт США Л 3211927, кл. 307-885, опубл. 1965 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство тестового контроля логических узлов | 1988 |

|

SU1564623A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1709318A1 |

| Устройство для контроля логического состояния элементов цифровых объектов | 1984 |

|

SU1252793A1 |

| Устройство для контроля функционирования логических блоков | 1986 |

|

SU1327107A1 |

| Логический анализатор | 1986 |

|

SU1410033A1 |

| Устройство для управления вентильным преобразователем | 1980 |

|

SU1146781A1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОГО КОНТРОЛЯ ПАРАМЕТРОВ НАПРЯЖЕНИЯ | 1990 |

|

RU2018147C1 |

| Устройство для сопряжения электронной вычислительной машины с объектом контроля | 1974 |

|

SU595720A1 |

| Противоугонное устройство для транспортного средства | 1989 |

|

SU1632837A1 |

| Устройство для управления разрядником электроимпульсной установки | 1990 |

|

SU1778752A1 |

Авторы

Даты

1981-03-07—Публикация

1978-10-05—Подача