1

Изобретение отноеитея к вычислительной технике и может быть использовано в системах, предназначенных для функционального контроля и диагностики неиснравностей различных цифровых объектов в процессе их производства и эксплуатации.

Известно устройство 1, содержащее блок управления, блок обмена информацией с процессором, регистр - для запоминания логических значений входных сигналов, формирователи, анализатор, входной коммутатор, содержапций элементы коммутации каналов связи с выходами объекта.

Недостатком устройства являетея точности допускового контроля выходных сигналов объекта из-за погрешности, вносимой электронными ключами входного коммутатора.

Известное устройство 2, имеет универсальные каналы связи с объектом, блок управления и блок обмена информацией с процессором. Недостатком устройства являетея отсутствие допускового контроля выходных сигналов объекта и большие затраты аппаратуры. Техническим решением наиболее близким к данному изобретению является уетройетво . В состав этого устройства входят регистр данных, регистр управления, регистр результатов, блок еинхронизации, генератор базовых сигналов, первый коммутатор, кана2

лы связи, каждый из которых содержит триггер данных, триггер управления, формирователь, схему сравнення, коммутируюш,ий элемент. Выход блока синхронизации соединен с

первыми входамн регистров данных и управления и первого коммутатора, второй вход которого еоединен с первым выходом генератора базовых сигналов, второй выход которого соедпнен е первым входом формирователя,

второй вход формирователя соединен с выходом триггера данных, а выход - через коммутирующий элемент е соответствующим каналом связи устройства с объектом, к которому подключен также первый вход схемы сравнеПИЯ.

Выход триггера управления подключен ко входу коммутирующего элемента, еннхровходы триггеров унравлення и данных соедннены с первым выходом регистра управления, информационные входы триггеров управления и данных и второй вход регистра уиравления соединены с выходом регистра данных, второй вход которого и вход н выход блока синхроннзации соединены со входами и выходами устройства.

Недостатком устройства - прототипа являются большие затраты аппаратуры в каналах связп с объектом. Многие объекты контроля имеют значительное число внешних выводов

(до 200-300), что требует такого же числа

каналов связи с ооъсктом у устроиства солря «еи11я. При большом числе каналов указапlibiii недостаток особенно ощутн.м п приводит к тому, что объем аниаратуры в устройстве сопряжения с объектом намного нревышает величину аипаратных затрат во всех остальных устройствах системы контроля, участзующих в функциональном контроле объекта, в том числе н в иснользуемой в ее составе ЭВМ.

Предлагаемое устройство сопряжения с объектом в зиачительиой стененн устраняет даннъи недостаток устройства - нротот1И:а.

Целью нзобретения является нрощенне устройства. Поставленная цель достигается тем, что Б устройство введены дешифратор и второй коММутатор, а в калсдый канал элемент il-ПЕ, ирнчем выход первого коммутатора соединен со вторым входом схемы сравнепия, выход которой связан с нервым входом элемента 11-ПИ, второй вход которого соединен со вторым выходо.м решстра управления, а выход - с первыми входами регистра результата и второго коммутатора, вторые входы которых н первый вход дешифратора соединены с выходом блока синхронизации, второй вход дешифратора соедннеи с выходом регистра данных, выходы регистра результата соедииены через дешифратор и второй коммутатор с выходами устройства.

Даппая цель достигается такпм построением устройства, при котород сравпение входных и выходных иотенциалов объекта с границамн областей «1 и «О осуществляется с помощью одной и той же схемы сравнения в каждом канале евязи с объектом. Доиолпптелъное сокращение аинаратуры обеспечивается за счет того, что функции логического анализа реакции объекта нереданы процессору, а само устройство обеспечивает лишь определепие логических значений сигналов на каналах и факта отклонения нотенциалов на каналах за границы областей «1 н «О, iipiiчем определение логических значений выходных сигналов объекта и задание ему входных сигналов оргаинзоваиы как последовательпонараллелъные нроцедуры.

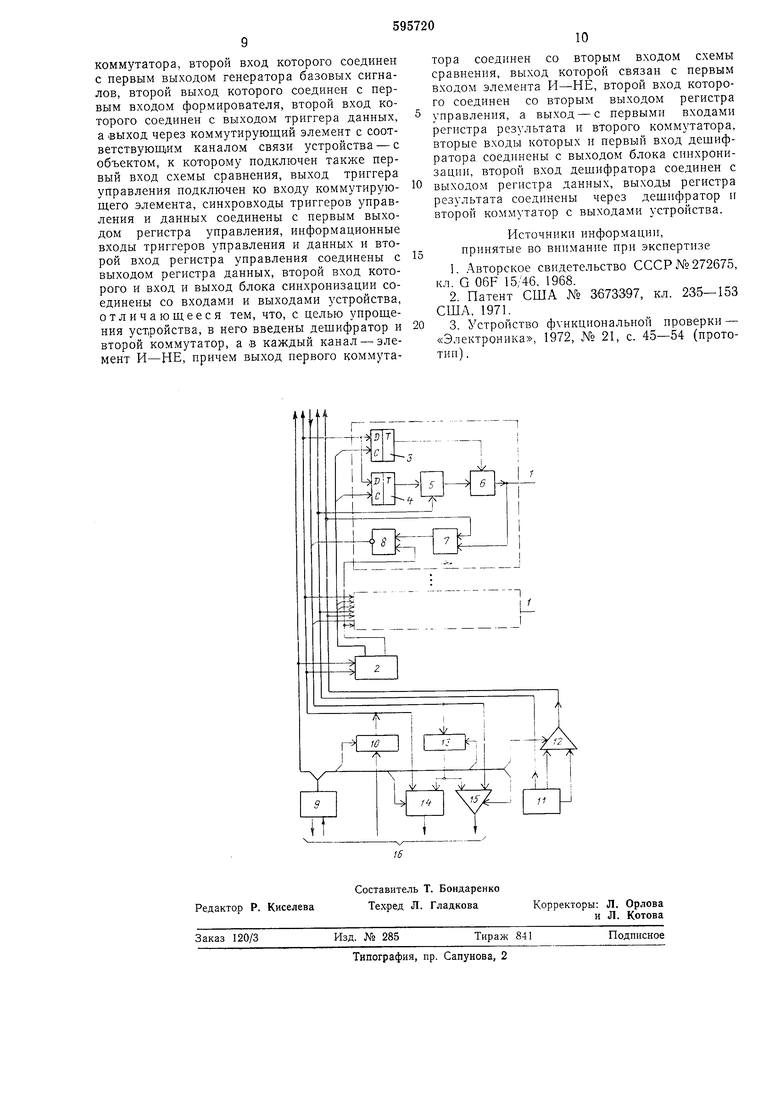

Сущность нзобретения поясняется чертежом, на котором представлена фуикционалъная блок-схема устройства.

Устройство содержнт каналы 1 связи с объектом контроля, регистр 2 унравления, триггер 3 управлеиия, триггер 4 данных, формирователь 5, коммутирующий элемент G, схему сравнения 7, элемент I-i--ПЕ 8, блок 9 сиихроннзации, регистр 10 данных, генератор II базовых сигналов, коммутатор 12, региетр 13 результатов, дешифратор 14, коммутатор 15, )5ходы - выходы 16 устройства.

В состав устройства входит регистр 2 унравления каналами, и оборудование каналов, которое включает следующие элементы, индивидуальные для каждого канала: триггер унравления 3, который служит для запоминания бита даипых, определяющего фуикц1ио

каиала в процессе коптроля объекта («1 каиал слул-сит для воздействия на вход объекта, «О - для опроса состояиия вы.хода объекта); триггер даниых 4, предпазначеииый для зано.мипания логического зиачення сигнала, нрикладываемого ко входу объекта контроля; формпрователь 5, обеспечивающий подачу па канал потенциала «1 или «О в незавнспмостп от состоянпя триггера даиных 4, коммутнрующий элемент 6, который служит для отключения выхода формирователя 5 от канала ири состояиии «1 триггера управлепия 3 (т. е. в том случае, когда канал подключей к выходу объекта контроля); схему 7 еравнения сигналов на канале с границами областей потенциалов, установленными для логических значений «1 п «О на выходах объекта коптроля; элемепт И-ПЕ, иредпазначенный для нередачи выходного сигнала схемы 7 в другне блоки устройства; блок синхропнзацнн 9, регистр данных 10, включающий счетчик адресов блоков каналов и буфериый ниформационный регистр для передачи данных в блоки каналов; генератор базовых сигналов 11, который задает опорные уровни напряжений формирователям 5, определяющие сигиалы «1 и «О на входах объекта коптроля, п эталонные уровни паиряжений схемам сравиеиия 7, иредставляющие собой границы областей потенциалов, воспринимаемых как сигиалы «1 п «О на выходах объекта; первый коммутатор 12, с помощью которого обеспечивается подключение ко входам схем сравнепия 7 одного или другого выхода генератора И; регистр результатов 13, предназначеппый для запоминания результатов сравнения, выиолияемого схемами 7; дешифратор 14, который фиксирует отклонение потенциалов иа каиалах за пределы допустимых для сигналов «1 п «О областей; второй коммутатор 15, е иомощью которого производитея передача в процессор системы контроля либЪ еоетояния региетра результатов 13, либо логических зиачеиий выходных сигналов объекта коитроля, иол)чаемых на выходах схем сравнения 7. Для обеснечеиия связи устройства с процессором системы контроля входы и выходы блока синхронизации 9, входы регистра данных 10, выходы дешифратора 14 и второго коммутатора 15 еоединеиы с внешними входами и выходами 16 устройства.

Связи перечислепных выше блоков устройетва с капалами унифицированы и осуществляютея е помогцью системы шин. Выходы блока синхронизации 9 предетавляют собой управляющие шины, нредпазначенные для нередачи в блоки каналов сигналов разрешения приема даииых. Выходы регистра данных 10 являются адресными пл-ишмп, с номощью которых задается адрес участвующего в операЦ1И-1 канала, п шина.ми выдачи данных в каналы. Входы регистра результата 13 являются шинами приема данных пз каналов. Выходы генератора базовых сигналов 11 и первого коммутатора 12 нредставляют собой щины

опорных потенциалов формпроватслей 5 и схем сравнения 7 всех каналов.

В описываемом варианте устройства шины выдачи данных и Н1ины приема данных рассчитаны на параллельную передачу ниформацпи, имеющей формат, равный одному байту (восемь двоичных разрядов) и, таким образом, включают по восемь отдельных линий. В составе устройства может входить п блоков каналов связи, в зависимости от числа висшних выводов у объекта контроля. Каждый блок обеспечивает 8 каналов связи с объектом.

При этом для обмена данными с каждым каналом используется одна из шин выдачи. соответствующая этому каналу, и одна из шин приема. Информационный буферный регистр, входящий в состав регистра данных 10. и регистр результатов 13 имеют по восемь разрядов.

Предлагаемое устройство работает cлeдvю Ш.НМ образом.

Программное управление УСТПОЙСТВОМ при контроле цифровых объектов осуш.ествляется со стороны процессора системы контроля. Основными операциями устройства являются:

-прнем от процессора данных, определяющих ФУНКЦИИ каждого канала, запоминание этих данных в триггерах управления 3 и собственно коммутация пепей в соответствии с этими данными. Эта операция предшествует процессу контроля объекта и предназначетта для подключения с помощью коммл-тирующих элементов б выходов формирователей 5 к тем каналам, которые связаны со входами объекта и их отключения от тех каналов, которые связаны с выходами объекта:

-прием от процессора данных, определяющих логическтте значения входор. объект. в текущем тякте его контроля, запоминание их в триггерах 4 и приложение ко входам объекта потенциалов, соответствмотцих заданным логическим значениям входов:

-сравнение с помотцью схем 7 сиптялов на выходах объекта с границами областей «1 и «О для определения логических значений выходных сигналов объекта в текущем такте контроля, пепеп;ачя логических значений выходов объекта в процессор, сигнализация процессору об отклонении потенциалов на выходах объекта за пределы границ областей «1 и «О.

Для выполнения любой из указанных операций процессор, через с,оответствуюш,ие входы 16 задает блоку синхронизации 9 код операции ц момент начала операции. Адрес участвующего в операции блока каналов либо задается ня входах устройства, связанных с регистром 10. и в начале операции принимается в счетчик адресов, входящий в этот регистр, либо образл ется плтем увеличения на единицу состояния счетчика.

В операциях, предусматривающих данных от процессора, этц данные задаются на входах устройства, связанных с тем же р ГПСТрОз 10. ПТгЬорМ. 1ГО 1Ч-ТЙ бфер

этого рогУ1стпа и .ачи дпииых оказываются дост пиымн любомл блоку каналов. В операциях передачу данных в процессор данные блока кяуалон. вьбранного Лpeco т, установле П1ым на адресных шиттах, передаются через шппн приема даниых и второй комлтутатор 15 нп СР-ЯЗЯННЫГ- с процессором р,ыход;,т ттро: 1с вя. В олификации

По ппсмЯ11пп персллч. лянпых иа эти выходы ос чцегття тся с регистра ро:пм,тята 13 тяк чероз ко: М татор 15.

В описывае ом варианте устройства сопряжения с объектом контроля внутренний обмен лянными (чорез местные цинтл) п внешний обмен ( входы и выхолы 16) ОСУигествля тся после.товательно - параллельно. Единицей датных. пepeлaвae тoй параллельно, являс ся байт.

При Р-ЫПО НС Ч ОггеРОитЙ, в KOTOpI,TX ЧПств от блоки ктирлов. за1 п-тч блок селоктиp eтcя с .ыо а троса, устяновлеиного па адресных . Этот адрес анализируется деитифраторами, входящими в состав регистра

т равлент|51 блоков каналов, о.чиако только в одном б токе, в . к кoтopo тy производптся обряшецпе. заданному адресу будет соответгтвор.ять такое значеттпе сигпала летписЬраторп. пптт птopo т ия, выходы регистрч 2. связя1трт1тг ео в одрми 3, 4, обеопечтряотгя Р пг тачп сттгтгл.топ блока стптХПОТТЧЗПП 9. п ИЯ ЭЛГ е1ТЯ МTlR

8 i.i.Tc пгпял ;1. азроитпюпии вт, выходных гигтяО, c-е enipiipTii 7 ця иттт11,7 тпттых в Р гттстг рег- .тьтятр 13.

Спявиени 7 сигнялов Р кя.иялях с

текдщим зпячeт;иe т стгияло тта выходе псрворо комм тятпгя 15 осутчестгляется иеттреРыв1 О и не спт-тхро1птзиг 1лется гигчaля тт б.точя, 9. Остя ч-ттт,то кянп.топ МОГУТ бьть вьт.зря-т оотретгтвО1Т111мп сигттяля П тот-о блот.гя, тт | тупртотпттлпт Tjcpr3 реГТУГТР . p,vnT,T ТРИГРСПОТ я IT 4 ВУ тбРЯТТИОГО блОКЯ ,Г1Й из ТТ1Х Опг ляТИТЧ ЯВЛЯотся яттньту ря Р рутстря 10 в тРтгерьт

ПРЯРЛОП1Я 3. ПРЧ Зто-Т. еглУТ в Н КОТОРЫЙ

Tpyirrep 3 прпи яет Я «1. то КО ЛМУТИР ЧОптий 6 .пуочяет к КЯКЯЛУ выход Лор ттровят ЛЯ .5, Рглтт пртт-ттмяется «О, то

форлтрпряте я 5 окязывяется отключенпы т от кяттяля. ДРУГОЙ опяряцией является приест из регистра 10 лирических знячрнттй рАопов обт- ктя тгоитро.тя р. данных 4 При тплт, оглт в трттррер 4 прщпп яется

... то (1 пр тировятель 5 перетяет ття кятта.т потеи тиял «l--. отичм утз вултходов генеряторя базовых сттгцалов 11. Если пртуиимается «0--. то Лор.тшователт 5 передает на кячял потет тиял «0, получае-.тьту с

ДРЛТОГО РеНСРЯТОРЯ 11.

Определени .топтчески знячгиий ВЫУОТИЫХ

стугналов объекта контроля и fhop tиpoвяииe

результата сравнения потенпткялов уья КПУУЯлах пропсходит следующим образом. Области

потенциалов, восцринимаемых как сигналы

«1 и «О на каналах, задаются двумя границами: нижней граинцей области «1 и верхней границей области «О. Сигнал на канале считается «1, если его иотенциал вьпис нижней гранинтзт «, и считается «О, если ои ниже верхней грани 1ы «О. Если нотенциал канала ниже нижней границы «I н выше верхней границы «О, то логическое значение сигнала считается иеоиределеииым. Границы областей «1 и «О задаются сравнения с выхода иервого коммутатора 12. Пои этом выходной сигиал каждой схемы 7 образуется в соответствии со следующим иравнлом: если иотенииал канала вынге нотеициа.та выхода коммутатора 12, то выход схемы 7 имеет значенне «1, в противном случае выход схемы 7 нмест зиаченне «О.

В начале онерации сравнения нотенцналов на каналах блок синхронизации 9 обеспечивает с коммутатора 12 иодключение ко входам ехем 7 того выхода генератора 11. который задает инжнюю границу области «1. Так как в выбпанггом блоке каналов входы элементов И-НЕ 8, связанные с выходом регистра уиравлеиня 2. имеют значение «1. выходные сигналы ехем 7 этого блока через элементы 8 ностлнают (в инвертированном виде) на шины ппиема данных в регистр результатов 13. Выходной сигнал со схемы 7 постунает но соответстплдотцей этой схеме тинне на вход соотр-етствлнотцего разряда регнстра результата .Я. По с.тед -тотцо г. сигият блока синхронизаннн 9 еостояггие тин нриема данных записывается в триггеры разря.топ регистра. Далее с номощью коммутатора 12 на входы схем еравнения 7 нодается иотснцргал с того выхода генератопа П. который задает верхнюю границу области «О. После этого новые значения выходных снгиа.ггов схем 7, цостуиаюнпте на входы регистра результатов 13, онратниваются очередным еигиалом блока еиихронизап.ин. Причем, еслн на вход ратрЯчга с РЬТХОДЯ соответетп юттим ехемы сравнення пост пает снгнал «I, то этот разряд сбрасывается в «О, еели снгнал «О, то нредьпуитее состояние разряда сохраняется неизменным. В результате, в контте операции i-ый разряд регистра 13 оказывается в состоянии «1, если цотен1нал соответствующего этому разряду канала выходит за границы областей «1 ц «О, н в «О, еслн цотенциал находится в области «1 или «О.

Если в оиерацци требуется лчитывать состояиие всех каналов, то дешифратор 14 выдает сигнал «1 на соответствующий выход устройства, связанный с процессором, только если хотя бы один разряд регистра 13 имеет значение «1. Если все разряды имеют значения «О, то дешифратор вырабатывает сигналы «О.

Еслц в оиерации сравнения сигналов до.тжны участвовать лишь некоторые каналы, то процессор залает устройству байт маски, который принимается в регистр 10, Каждый разряд байта маски соответствует оцределенном , иричем еслн состояние некоторого капала не должно учнтываться в операции, то в соот1зстствуюи1;ем ему разряде маски указыпастся «О (канал маскируется), в иротивном с.лучае в этом разряде указывается «1. Байт маеки подается па входы дешифратора 14 с выходов регистра 10. При этом, если хотя бы о.ч.ни разряд регистра 13, соответствующий незпмаекнропаиному каналу, имеет состояние «1 то выход дегннфратора 14 имеет значение «1, в противном значение этого п гхода «О. Выход )paтopa 14 через соогпетствуюишй выход входов и выходов 16 устройства сня.заи с процессором. Состояние «1 этого выхода рассматривается как особый результат онерации устройства сопряжения с обьектом контроля rt вызывает HpepijiBanHc или остаиов программы ироверки об)екта.

Так как дс) н после вытолттеиия операции сравнеппя иог-огипалоп иа каиалах на выходе коммутатора 12 поддерживается иотенциал верхней границ, области «О, то для тех каналов, логические значения которых определены, эти зиачеиня (в инвертированном виде) присутствуют иа выходах элемеитов И-НЕ 8 н МОГУТ быть иереданы в процессор (через второй коммлтатор 15) после операции сравпения.

Преимунгеством предлагаемого устройства еопря кетт тя с обт ектолт контроля ио сравиеттию с яипло -1чгтт,1-Т1г лттройствамн, ирименяеДП птп .цпя целей ф 1ткт1иона,тьного контроля цифровг.тх объектов (в том чнелс с опггсанным выше прототипом), является существенно меиьшнй объем аппаратуры.

По ерапнепию е устройством-прототипом в каждо т канале нрсдла аемого гтройстр.а чнело трпггероп меиьи1ст1о до ДВУХ (вместо пяти), схем срапнетптя иотегигиалор до одной (вместо ) и вместо схемы «искпючителт,ное ИЛИ введен одии двухвходной элемеит И- -НЕ, Это зпячтттелг тю сокращает стоимость Устройства. особе1гно при большом число катталов, теоб одимом при контроле больтнннства лз,тов и блоков средств вычислительной техники и автомятикгг. Вместе с тем, в еоетаве системы контроля устройство обеспечивает вьгно.тнеиие всех тех же флнкций, которыс реализуются нанболсе еовсрН1енными известнымгт устройствами аналогичного назначения.

ФормЛл а изобретения

Устройство для сопряжения электронной вычттслите.тьной ашитгы с объектом контроля, содержащее регистр данных, регистр результатов, блок синхронизации, генератор базовых еигиалов, первый коммутатор, регистр

управления, каналы связи, каждый из которых содержит триггер тайных, триггер управления, формпрозателг,. схему сравнения и коммутирующ.ий элемеит, причем выход блока синхроиизации соединен с первыми входами регистров данных ;: управления н первого

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство контроля для управляющих вычислительных систем | 1983 |

|

SU1101829A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Процессор ввода-вывода | 1989 |

|

SU1797722A3 |

| Устройство для контроля | 1985 |

|

SU1293739A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Устройство для контроля и восстановления вычислительного процесса | 1988 |

|

SU1605233A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Двухканальное устройство для контроля и восстановления процессорных систем | 1986 |

|

SU1397917A1 |

Авторы

Даты

1978-02-28—Публикация

1974-12-25—Подача