(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ НАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля электрического монтажа | 1985 |

|

SU1345212A1 |

| АВТОМАТИЗИРОВАННАЯ СИСТЕМА КОНТРОЛЯ ПАРАМЕТРОВ ЭЛЕКТРОННЫХ СХЕМ | 1991 |

|

RU2106677C1 |

| Устройство для контроля электрического монтажа | 1985 |

|

SU1390616A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1151991A1 |

| Автоматизированная система контроля параметров электронных схем | 1987 |

|

SU1500996A1 |

| Устройство для контроля постоянной памяти | 1987 |

|

SU1411838A2 |

| Устройство для контроля блоков памяти | 1981 |

|

SU1023398A1 |

| Автоматизированная система контроля параметров электронных схем | 1981 |

|

SU1010602A1 |

| Устройство для контроля электрического монтажа | 1983 |

|

SU1138809A1 |

I

Изобретение относится к вычислительной технике, в частности к технике запоминающих -устройств, и может быть использовано для проверки и контроля блоков постоянной памяти, а также для контр.оля логических элементов и блоков.

Известно устройство для контроля постоянной памяти, содержащее адресный блок, блок ввода информации, блок синхронизации, блок управления, схему сравнения 1.

Недостатком этого устройства является то, что при его помощи можно контролировать блоки памяти на последнем этапе изготовления по функционированию из-за отсутствия блоков измерения электрических параметров и стимулирующих воздействий.

Наиболее близким по технической сущности к предлагаемому -является устройство для контроля логических узлов, содержащее адресный коммутатор, блок анализа неисправностей и логической обработки, блок оперативной памяти, блок управления, блок генерации стимулирующих воздействий, блок памяти неисправностей, блок выявления неисправностей 2.

Недостаток устройства - его низкое быстродействие, что в свою очередь повыщает трудоемкость контроля из-за сложности процесса программирования.

Цель изобретения - повыщение быстродействия устройства для контроля блоков памяти.

Поставленная цель достигается тем, что в устройство для контроля блоков памяти, содержащее первый формирователь импульсов, выход которого подключен к первому

входу коммутатора, первый выход коммутатора является выходом устройства, блок сравнения, пульт управления, выход которого подключен к первому входу блока управления, и блок измерения параметров сигналов, дополнительно введены блок регистров, выход которого подключен к первому входу первого формирователя импульсов и к первому входу блока измерений параметров сигналов, а его первый вход подключен к выходу пульта управления, адресный блок, первый вход которого подключен

к выходу пульта управления, второй вход - к первому выходу блока управления, первый выход - ко второму входу коммутатора, второй выход - ко второму входу блока управления, а третий выход - к первому входу схемы сравнения, блок синхронизации, первый вход которого подключен ко второму выходу первого формирователя импульсов и к первому выходу блока измерения параметров сигналов, второй вход - ко второму выходу блока управления, первый выход - ко второму входу блока регистров, второй выход - к третьему входу блока управления, а третий выход - к первому входу блока измерения параметров сигналов и ко второму входу первого формирователя импульсов, преобразователь кодов, первый вход которого подключен к четвертому выходу адресного блока, второй выход - к четвертому выходу блока синхронизации, третий вход - ко второму выходу блока измерения параметров сигналов, первый выход - к третьему входу блока синхронизации, а второй выход - к четвертому входу блока управления, дешифратор, первый вход которого подключен к пятому выходу блока синхронизации, шифратор, первый вход которого подключен к первому выходу дешифратора, а его выход подключен к третьим входам первого формирователя импульсов, блока измерения параметров сигналов, второй формирователь импульсов, выход которого подключен ко второму входу дешифратора, блок усилителей, первый вход которого подключен к выходу пульта управления, а его выход подключен к третьему входу дешифратора, блок задания режимов, первый вход которого подключен к выходу блока сравнения, второй вход - к третьему . выходу блока управления, п.ервый выход - к пятому входу блока управления, а второй выход - ко входу второго формирователя импульсов, к четвертому входу дешифратора и ко второму входу блока усилителей, а также третий формирователь импульсов, вход которого подключен к третьему выходу преобразователя кодов, а его выход является выходом устройства, четвертый вход блока измерения параметров сигналов подключен ко второму выходу коммутатора.

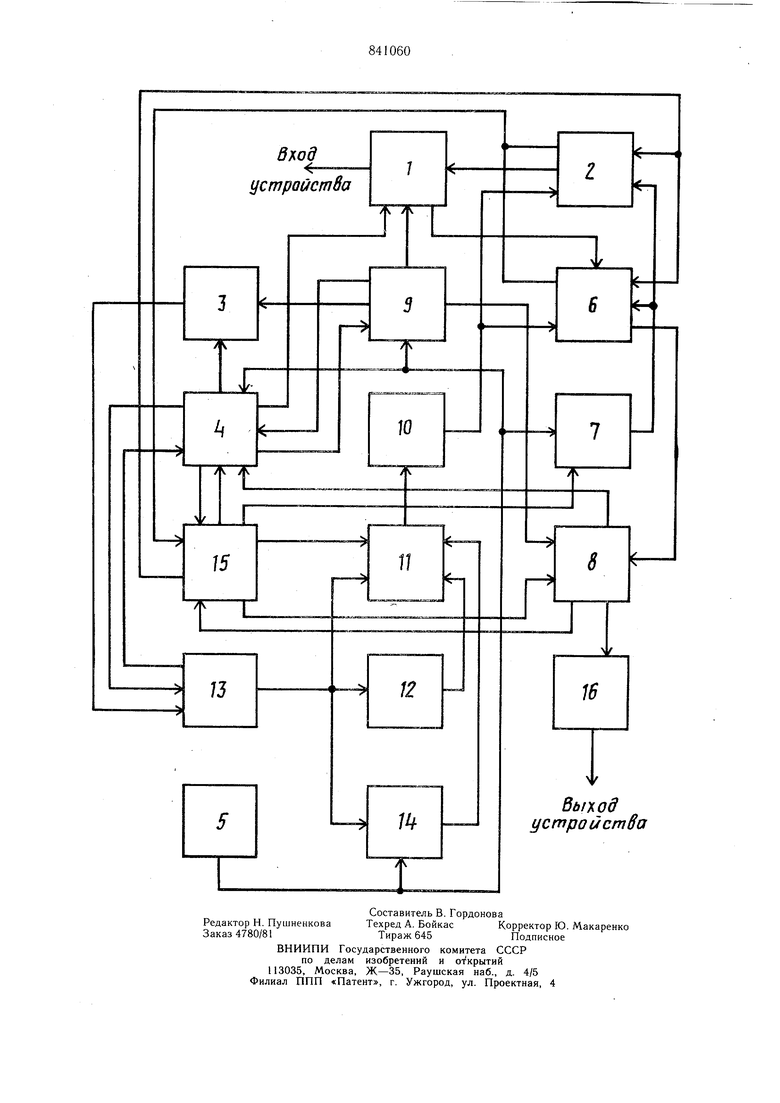

На чертеже представлена функциональная схема устройства.

Устройство содержит коммутатор 1 для контроля блоков памяти, первый формирователь 2 импульсов блок 3 сравнения, блок 4 управления, пульт 5 управления, блок 6 измерения параметров сигналов, блок 7 регистров, преобразователь 8 кодов, адресный блок 9, шифратор 10, дешифратор 11, второй формирователь 12 импульсов, блок 13 задания режимов, блок 14 усилителя, блок 15 синхронизации и третий формирователь 16 импульсов.

Устройство работает следуюш,им образом.

Перед началом работы с пульта 5 управления в блок 7 регистров вводятся данные в двоичном коде в соответствии с электрическими параметрами, которые должны обеспечить первый формирователь 2 в виде стимулирующих воздействий и блок 6 измерений параметров сигналов в процессе автоматического контроля проверяемых изделий.

Объект контроля (ОК) подключается к коммутатору 1, управление которым осуществляют адресный блок 9 контролируемых точек и блок 4 управления. На подключенные точки коммутатора поступают стиo мулирующие воздействия с первого формирователя 2 и ответная реакция ОК на воздействия, которая контролируется блоком 6 измерения параметров сигналов.

Проверка ОК начинается от пускового импульса с пульта 5 управления, поступающего в блок 4 управления.

При этом формируется первая команда, по которой подключаются заданные точки и включается блок 15 синхронизации, вырабатывающий импульсы, определяющие последовательность операций. Формат команды и количество операционных тактов определяется текущим видом измерения, установленным блоком 13 задания режимов. Переход к следующему виду контроля управляется блоком 3 сравнения, который контролирует

5 адрес перехода к следующему виду и конечный адрес проверки. Заданные адреса перехода и останова хранятся в регистрах блока 4 управления. Управление первым формирователем 2 и блоком 6 измерения параметров сигналов осуществляется щифратором 10, формирующим кодовую комбинацию для настройки и включения. Выбор соответствующего кода команды в щифраторе 10 производится дешифратором 11 в соответствии с видом измерения, установленном

5 в блоке 13 и операцией блока 15 синхронизации. При вводе данных первый формирователь 2 и блок 6 измерения параметров сигналов из блока 7 регистров автоматически выбирается диапазон формируемых напряжений в блоке 2 и коэффициент усиления блока 6, что обеспечивает защиту объекта контроля от включения повышенных напряжений и достижение достаточной точности при измерении электрических параметров. Сигналы на выбор соответствую, щего адреса кода, диапазона и усиления в шифраторе 11 формируют второй формирователь 12 и блок 14 усилителей. Результат измерения, а также сигналы готовности блока 6 измерения параметров сигналов и первого формирователя 2 поступают в блок 15

0 синхронизации.

При измерении по сигналу «Норма производится прерывание генерации тактов в блоке 15 синхронизации и вырабатывается сигнал, который поступает в блок 4 управления для включения следующей команды.

При отклонении -от нормы измеритель вырабатывает сигнал «Брак, включающий через блок 15 синхронизации преобразователь 8 кодов, который преобразует двоичный код адреса точек и величины измеряемых параметров в двоичнодесятичный код, поступающий в третий формирователь 16, формирующий знак для регистрации в протоколе и индикации.

Введение дополнительных блоков и связей позволяет повысить бь1стродействие предлагаемого устройства по сравнению с известными что, в свою очередь, повышает надежность и уменьшает трудоемкость процесса контроля, а также снижает себестоимость затрат на проверку и контроль проверяемых изделий.

Формула изобретения

Устройство для контроля блоков памяти, содержащее первый формирователь импульсов, первый выход которого подключен к первому входу коммутатора, первый выход коммутатора является выходом устройства, блок сравнения, пульт управления, выход которого подключен к первому входу блока управления, блок измерения параметров сигналов, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены блок регистров, выход которого подключен к первому входу первого формирователя импульсов и к первому входу блока измерений параметров сигналов, а его первый вход подключен к выходу пульта управления, адресный блок, первый вход которого подключен к выходу пульта управления, второй вход - к первому в.ыходу блока управления, первый выход - ко второму входу коммутатора, второй выход - ко второму входу блока управления, а третий выход - к первому входу схемы сравнения, блок синхронизации, первый вход которого подключен ко второму выходу первого формирователя импульсов и к первому выходу блока измерения параметров сигналов, второй вход - ко второму выходу блока управления, первый выход - ко второму входу блока регистров, второй выход - к третьему входу блока управления, а третий выход - к первому входу блока измерения параметров сигналов и ко второму входу первого формирователя импульсов, преобразователь кодов, первый вход которого подключен к четвертому выходу адресного блока, второй вход - к четвертому выходу блока синхронизации, третий вход - ко второму выходу блока измерения параметров сигналов, первый выход - к третьему входу блока

синхронизации, а второй выход - к четвертому входу блока управления, дешифратор, первый вход которого подключен к пятому выходу блока синхронизации, шифратор, первый вход которого подключен к

5 первому выходу дешифратора, а его выход подключен к третьим входам первого фор.мирователя импульсов, блока измерения параметров сигналов, второй формирователь импульсов, выход которого подключен ко второму входу дешифратора, блок усилителей, первый вход которого подключен к выходу пульта управления, а его выход подключен к третьему входу дешифратора, блок задания режимов, первый вход которого подключен к выходу блока сравнения, второй вход - к третьему выходу блока управления, первый выход - к пятому входу блока управления, а йторой выход - ко входу второго формирователя импульсов, к четвертому входу дешифратора и ко второму входу блока усилителей, а также третий формирователь импульсов, вход которого подключен к третьему выходу преобразователя кодов, а его выход является выходом устройства, четвертый вход блока измерения параметров сигналов подключен ко второму выходу коммутатора.

5Источники информации,

принятые во внимание при экспертизе

Р № 469971, кл. G 06 F 11/00, 1975 (прототип).

Авторы

Даты

1981-06-23—Публикация

1979-09-21—Подача