Изобретение относится к области вычислительной техники, в частности к запоминающим устройствам с последовательной выборкой информации. Известно запоминающее устройство с выборкой информации в последовательном коде, содержащее регистр сдв га, входы которого соединены с соответствующими логическими шинами, адресные шины, элементы И и элемент ИЛИ, причем первые входы элементов И соединены с соответствующими выходами регистра сдвига, вторые - с соответствующими адресными шинами, а выходы - со входами элемента ИЛИ Щ Недостатком этого устройства явля ется большое количество запоминающих элементов, необходимых для хранения информации. Наиболее близким к предлагаемому техническим решением является запоминающее устройство, содержащее регистр сдвига, шины управления, элементы И по количеству разрядов регистра сдвига и зяенент ИЛИ, причем выходы разрядов регистра сдвига соединены с информационными входами элементов И, управляющие входы которых подключены к соответствующим адресным шинам, а выходы соединены со входами элемента ИЛИ, информационные входы регистра сдвига подключены к соответствующим шинам логического нуля и единицы, вход разрешения записи регистра сдвига соединен с шиной Обращение, а выход последнего разряда регистра сдвига, подключен ко входу его первого разряда 21. Недостатком известного устройства является его сложность при хранении больших массивов информации, так как количество разрядов регистра сдвига равняется количеству хранимых чисел. Цель изобретения - повышение информационной емкости устройства. Поставленная цель достигается тем, что запоминающее устройство, содержащее накопитель, выполненный на

390

кольцевом сдвиговом регистре, содержащем П запоминающих элементов(П-1) запоминающих элементов которого соединены последовательно, а первые входы П запоминающих элементов соединены с шиной Обращение, вторые входы - с тактовой шиной, третьи входы с шиной установки в исходное состояние, четвертые входы - соответствующими шинами логического нуля и единицы, первые выходы П запоминающих Элементов соединены с первыми входами одних из элементов И группы, а вторые выходы - с первыми входами других элементов И группы, выходы которых подключены к соответствующим входам первого элемента ИЛИ, адресные шины, содержит группу элементов ИЛИ, второй, третий и четвертый элементы ИЛИ, первий, второй и третий элементы И и инвертор, при этом соответствующие входы элементов ИЛИ, группы второго и третьего- элементов ИЛИ соединены с соответствующими адресными шинами, а выходы вторых элементов ИЛИ группы - со вторыми входами соответствующих элементов И группы, выход второго элемента ИЛИ соединен со входом инвертора и первым входом второго элемента И, второй вход которого подключен к выходу первого запоминающего элемента, а выход - к первому входу четвертого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом инвертора, а второй - с выходом П-го запоминающего элемента, пятый вход которого соединен с выходом первого элемента И, первый вход которого подключен к выходу третьего элемента ИЛИ, а второй - к пятому входу первого запоминающего элемента, а пятый вход (п-1)-го запоминающего элемента соединен с выходом четвертого элемента ИЛИ

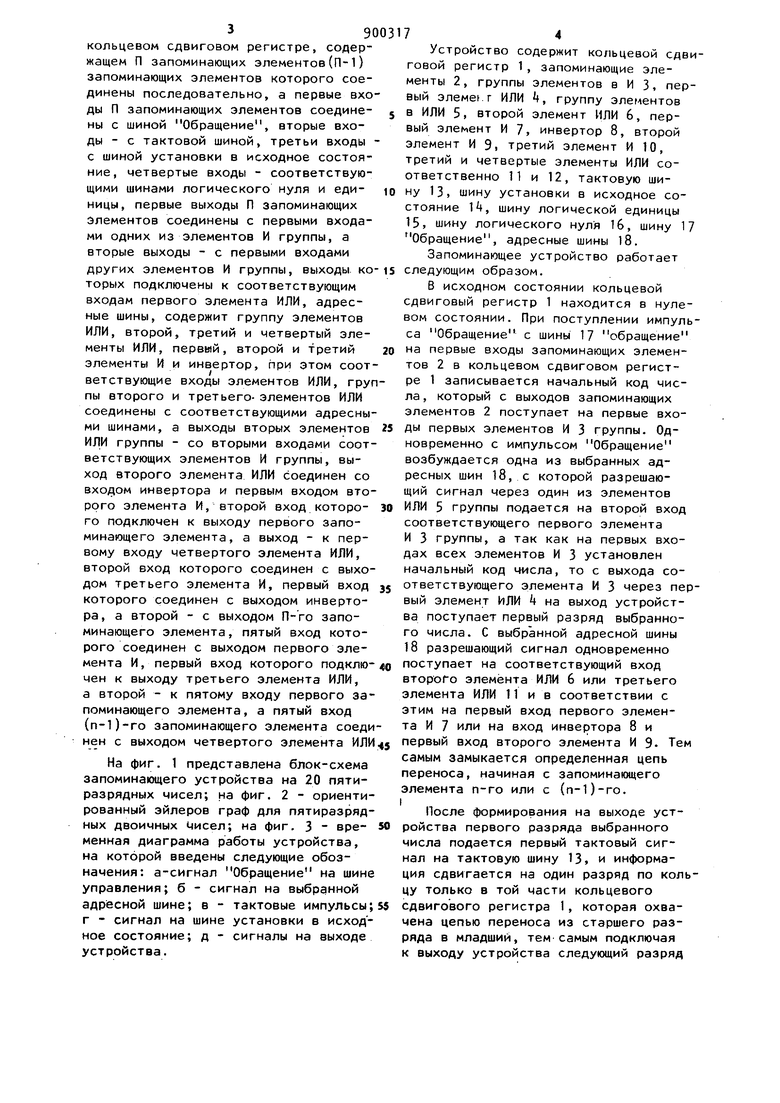

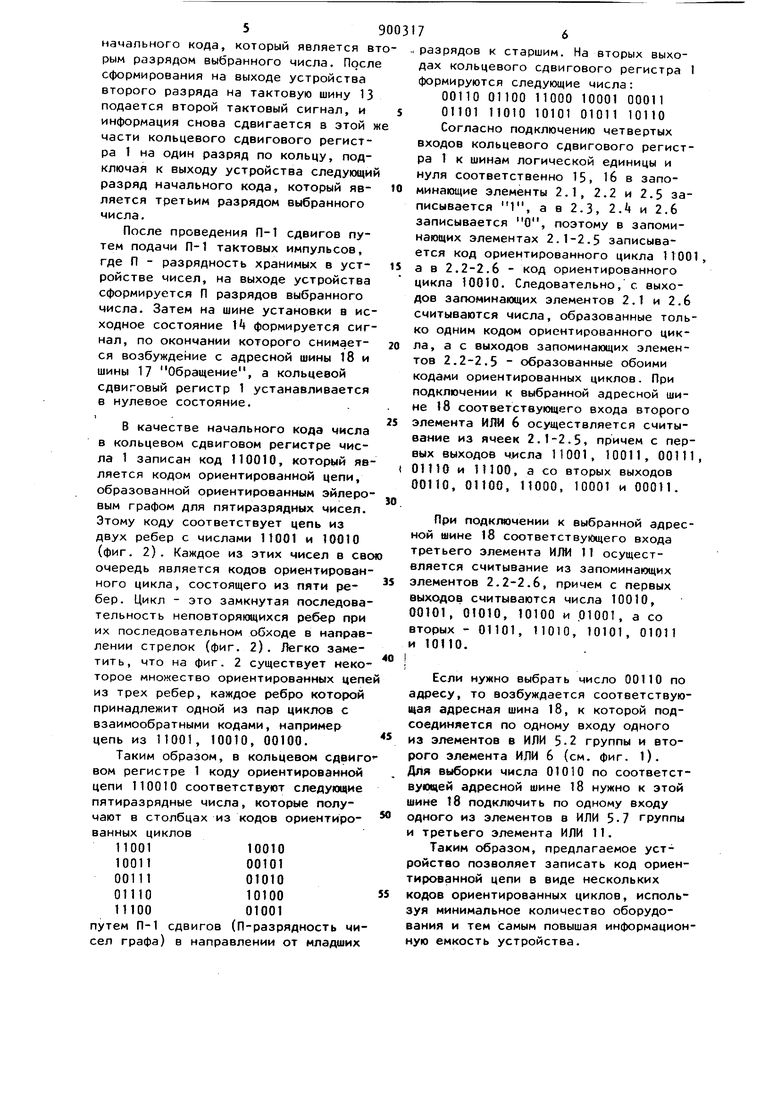

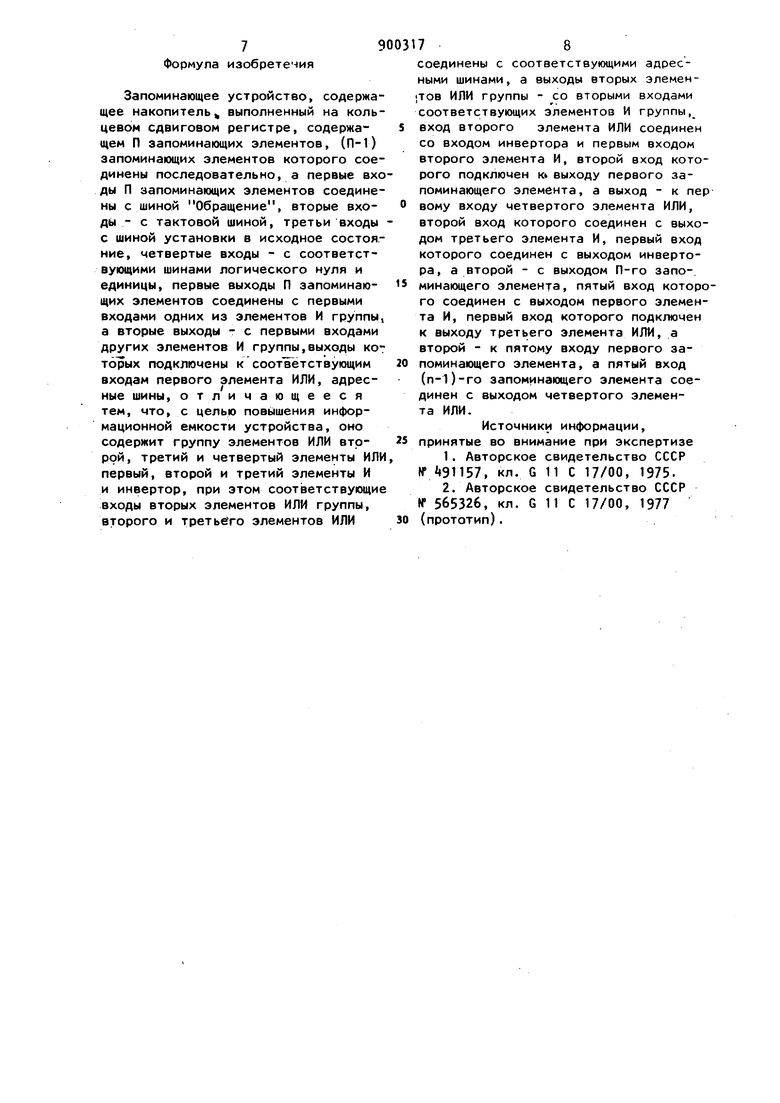

На фиг. 1 представлена блок-схема запоминающего устройства на 20 пятиразрядных чисел; на фиг. 2 - ориентированный эйлеров граф для пятиразрядных двоичных Чисел; на фиг. 3 - временная диаграмма работы устройства, на которой введены следующие обозначения: а-сигнал Обращение на шине управления; б - сигнал на выбранной адресной шине; в - тактовые импульсы; г - сигнал на шине установки в исходное состояние; д - сигналы на выходе устройства.

74

Устройство содержит кольцевой сдвговой регистр 1, запоминающие элементы 2, группы элементов в И 3, первый элемекг ИЛИ k, группу элементов в ИЛИ 5, второй элемент ИЛИ 6, первый элемент И 7, инвертор 8, второй элемент И 9, третий элемент И 10, третий и четвертые элементы ИЛИ соответственно 11 и 12, тактовую шину 13, шину установки в исходное состояние Ц, шину логической единицы 15, шину логического нуля 16, шину 1 Обращение, адресные шины 18.

Запоминающее устройство работает следующим образом.

В исходном состоянии кольцевой сдвиговый регистр 1 находится в нулевом состоянии. При поступлении импулса Обращение с шины 17 обращение на первые входы запоминающих элементов 2 в кольцевом сдвиговом регистре 1 записывается начальный код числа , который с выходов запоминающих элементов 2 поступает на первые входы первых элементов И 3 группы. Одновременно с импульсом Обращение возбуждается одна из выбранных адресных шин 18, с которой разрешающий сигнал через один из элементов ИЛИ 5 группы подается на второй вход соответствующего первого элемента И 3 группы, а так как на первых входах всех элементов И 3 установлен начальный код числа, то с выхода соответствующего элемента И 3 через певый элемент ИЛИ 4 на выход устройства поступает первый разряд выбранного числа. С выбранной адресной шины 18 разрешающий сигнал одновременно поступает на соответствующий вход второго элемента ИЛИ 6 или третьего элемента ИЛИ 11 и в соответствии с этим на первый вход первого элемента И 7 или на вход инвертора 8 и первый вход второго элемента И 9- Те самым замыкается определенная цепь переноса, начиная с запоминающего элемента п-го или с (n-l)-ro. г

После формирования на выходе устройства первого разряда выбранного числа подается первый тактовый сигнал на тактовую шину 13, и информация сдвигается на один разряд по колцу только в той части кольцевого сдвигового регистра 1, которая охвачена цепью переноса из старшего разряда в младший, тем самым подключая к выходу устройства следующий разряд 5 начального кода, который является в рым разрядом выбранного числа. Посл сформирования на выходе устройства второго разряда на тактовую шину 13 подается второй тактовый сигнал, и информация снова сдвигается в этой части кольцевого сдвигового регистра 1 на один разряд по кольцу, подключая к выходу устройства следующи разряд начального кода, который является третьим разрядом выбранного числа. После проведения П-1 сдвигов путем подачи П-1 тактовых импульсов, где П - разрядность хранимых в устройстве чисел, на выходе устройства сформируется П разрядов выбранного числа. Затем на шине установки в ис ходное состояние 1 формируется сиг нал, по окончании которого снимается возбуждение с адресной шины 18 и шины 17 Обращение, а кольцевой сдвиговый регистр 1 устанавливается в нулевое состояние, В качестве начального кода числа в кольцевом сдвиговом регистре числа 1 записан код 110010, который яв ляется кодом ориентированной цепи, образованной ориентированным эйлеро вым графом для пятиразрядных чисел. Этому коду соответствует цепь из двух ребер с числами П001 и 10010 (фиг, 2), Каждое из этих чисел в сво очередь является кодов ориентированного цикла, состоящего из пяти ребер. Цикл - это замкнутая последовательность неповторястцихся ребер при их последовательном обходе в направлении стрелок (фиг, 2), Легко заметить, что на фиг. 2 существует некоторое множество ориентированных цепе из трех ребер, каждое ребро которой принадлежит одной из пар циклов с взаимообратными кодами, например цепь из 11001, 10010, 00100, Таким образом, в кольцевом сдвиго вом регистре 1 коду ориентированной цепи 110010 соответствуют следующие пятиразрядные числа, которые получают в столбцах из кодов ориентиро ванных циклов 1100110010 1001100101 0011101010 ото10100 1110001001 путем П-1 сдвигов (П-разрядность чисел графа) в направлении от младших 76 разрядов к старшим. На вторых выходах кольцевого сдвигового регистра 1 формируются следующие числа: 00110 01100 11000 10001 00011 01101 11010 10101 01011 10110 Согласно подключению четвертых входов кольцевого сдвигового регистра 1 к шинам логической единицы и нуля соответственно 15, 16 в запоминающие элементы 2,1, 2,2 и 2,5 записывается 1, а в 2,3, 2, и 2,6 записывается О, поэтому в запоминающих элементах 2,1-2,5 записывается код ориентированного цикла 11001, а в 2,2-2,6 - код ориентированного цикла 10010, Следовательно, с выходов запоминающих элементов 2,1 и 2,6 считываются числа, образованные только одним кодом ориентированного цикла, а с выходов запоминающих элементов 2,2-2,5 - образованные обоими кодами ориентированных циклов. При подключении к выбранной адресной шине 18 соответствующего входа второго элемента ИЛИ 6 осуществляется считывание из ячеек 2,1-2,5, причем с первых выходов числа 11001, 10011, 00111, 01110 и 11100, а со вторых выходов 00110, 01100, 11000, 10001 и 00011. При подключении к выбранной адресной шине 18 соответствующего входа третьего элемента ИЛИ 11 осуществляется считывание из запоминающих элементов 2,2-2.6, причем с первых выходов считываются числа 10010, 00101, 01010, 10100 и 01001, а со вторых - 01101, 11010, 10101, 01011 и 10110. Если нужно выбрать число 00110 по адресу, то возбуждается соответствующая адресная шина 18, к которой подсоединяется по одному входу одного из элементов в ИЛИ 5,2 группы и второго элемента ИЛИ 6 (см. фиг, 1). Для выборки числа 01010 по соответствующей адресной шине 18 нужно к этой шине 18 подключить по одному входу одного из элементов в ИЛИ 5,7 группы и третьего элемента ИЛИ 11, Таким образом, предлагаемое устройство позволяет записать код ориентированной цепи в виде нескольких кодов ориентированных циклов, используя минимальное количество оборудования и тем самым повышая информационную емкость устройства.

Формула изобретечия

Запоминающее устройство, содержащее накопитель выполненный на кольцевом сдвиговом регистре, содержащем П запоминающих элементов, (П-1) запоминающих элементов которого соединены последовательно, а первые входы П запоминающих элементов соединены с шиной Обращение, вторые входы - с тактовой шиной, третьи входы с шиной установки в исходное состояние, четвертые входы - с соответствующими шинами логического нуля и единицы, первые выходы П запоминающих элементов соединены с первыми входами одних из элементов И группы, а вторые выходы - с первыми входами других элементов И группы,выходы кот тбрых подключены к соответствующим входам первого элемента ИЛИ, адресные шины, отличающееся тем, что, с целью повышения информационной емкости устройства, оно содержит группу элементов ИЛИ втррой, третий и четвертый элементы ИЛИ первый, второй и третий элементы И и инвертор, при этом соответствующие входы вторых элементов ИЛИ группы, второго и третьего элементов ИЛИ

соединены с соответствующими адресными шинами, а выходы вторых элементов ИЛИ группы - со вторыми входами

г .

соответствующих элементов И группы, вход второго элемента ИЛИ соединен со входом инвертора и первым входом второго элемента И, второй вход которого подключен к выходу первого запоминающего элемента, а выход - к пер вому входу четвертого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом инвертора, а второй - с выходом П-го запо-. минающего элемента, пятый вход которого соединен с выходом первого элемента И, первый вход которого подключен к выходу третьего элемента ИЛИ, а второй - к пятому входу первого запоминающего элемента, а пятый вход (n-l)-ro запоминающего элемента соединен с выходом четвертого элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР N tSns, кл. G 11 С 17/00, 1975.

2.Авторское свидетельство СССР № 565326, кл. G 11 С 17/00, 1977 (прототип).

Фи1.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU815769A2 |

| Постоянное запоминающее устройство | 1979 |

|

SU824312A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU822292A1 |

| Долговременное запоминающее устройство | 1979 |

|

SU847371A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU849303A1 |

| Запоминающее устройство | 1985 |

|

SU1280454A1 |

| Устройство для преобразования двоичного кода в код магнитного носителя | 1980 |

|

SU1148572A3 |

| Запоминающее устройство | 1979 |

|

SU842967A1 |

| Запоминающее устройство на сдвиго-ВыХ РЕгиСТРАХ | 1979 |

|

SU841052A1 |

.

г 9

Фиг.З

п

Авторы

Даты

1982-01-23—Публикация

1980-01-03—Подача