Изобретение относится к импульсной технике и можбт быть использовано для создания аналого-цифровых преобразователей параллельно-последовательного типа с повышенным быстродействием.

Известен способ параллельно-последовательного аналого-цифрового преобразования, заключающийся в том, что в первом такте входной аналоговый сигнал преобразуют путем сравнения с основны. ми эталонны /1И сигналами в сигналы двоичного кода, которые запоминают, а во втором и последующих тактах сигналы этого кода преобразуют в аналоговые сигналы обратной связи, которые затем масштабируют и суммируют, после чего из входного аналогового сигнала вычита ют общий аналоговый сигнал обратной связи, этот разностный сигнал усиливают и преобразуют, как в первом такте, в сигналы двоичного кода, которые также запоминают, l .

Однако в этом способе время преобра зования на каждом такте определяется ..

максимально-возможным; диапазоном изменения усиленного сигнала разности между преобразуемым сигналом и сигна.лом обратной связи, что приводит к уве.- личению среднего времени преобразования.

Целью изобретения является повышение быстроаействия аналого 1ифрового преобразования.

Достигается это тем, что в способе параллельно-последовательного преобразования, заключающемся в том, что в первом такте входной аналоговый сигнал преобразуют путем сравнения с основными эталонными сигналами в сигналы двоичного кода, которые запоминают, а во втором и последующих тактах этого кода преобразуют в аналоговые сигналы обратной связи, которые затем масштабируют суммируют, после чего из входного аналогового сигнала вычитают общий аналоговый сигнал обратной связи, этот раз КОСТНЫЙ сигнал усиливают и преобразуют как в первом такте, в сигналы двоичного

кода, которые также запоминают, в начале второго и послецующих тактов, изменяют весовые коэффициенты масштабирования аналоговых сигналов обратной свя зи, одновременно аналоговые сигналы обратной связи суммируют со вторым вспомогательным эталонным сигналом и изменяют на величину этого суммарного сигнала все основные эталонные сигналит, общий аналоговый сигнал обратной связи образуют путем суммирования сигналов обратной связи с первым вспомогательным эталонным сигналом, причем в начале третьего и последующих тактов изменяют вспомогательные эталонные сигналы.

В этом способе параллельно-последовательного аналого-цифрового преобразования за счет введения операций изменения весовык коэффициентов масштабирования аналоговых сигналов обратной связи и добавления вспомогательного сигнала, который суммируют с входным сигналом, причем одновременно смещают шкалы эталонных сигналов, уровень выходного сигнала после усиления разностного сигнала остается неизменным, если значение последнего пропорционально половине кванта шкалы данного такта преобразования, идя ост-альных значений разностного сигнала уровень усиленного сигнала может изменяться в пределах только половины возможного диапазона изменения. Таким образом, изменение усиленного сигнала при переходе к очередному гакту преобразования в два раза меньше аналогичного изменения усиленного сигнала в указанном известном способе.

При реализации этого cnoct a такое , техническое ремение приводит к пропорциопальному уменьшению времени выполнения в каждом такте аналого-«и4фового преобразования, т. е, к повышению его быстродействия, причем последнее достигается без изменения коэффициентов усиления аналоговых сигналов и без повышения точности выполнения операции сравнения аналоговых сигналов с эталонными.

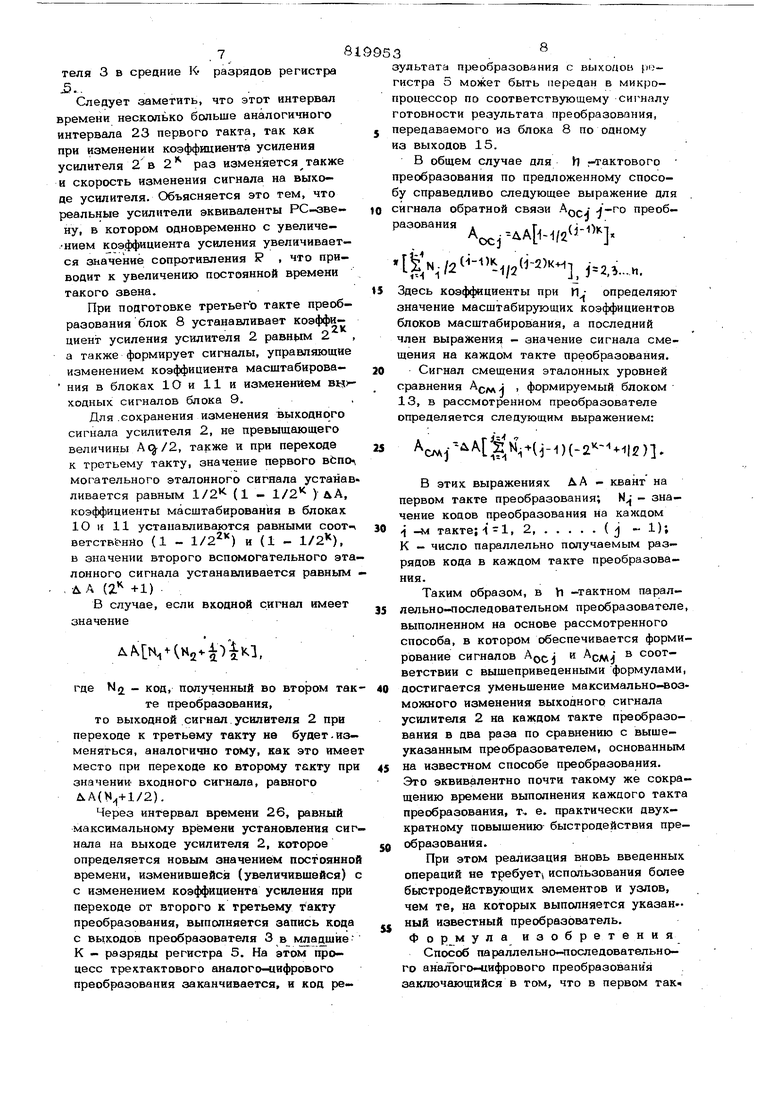

На фиг. 1 дана блок-схема трехтакт- аналого-цифрового преобразователя; на фиг. 2 - временная диаграмма -его работы.

Блок-схема содержит аналоговый вы- читатель 1, усилитель 2 с управляемым коэффициентом усиления, преобразователь считывания 3, блок эталонных сигналов 4, секционный регистр-счетчик 5, первый и второй цифроаналоговые преобраэователи (ЦАП) 6 и 7, блок управления 8,

блок 9 формирования вспомогательных эталонных сигналов, первый и второй блоки масштабирования 1О и 11, первый и второй аналоговые сумматоры 12 и 13, шину аналогового входа 14, интерфейсные входы-выходы 15 блока управления 8..

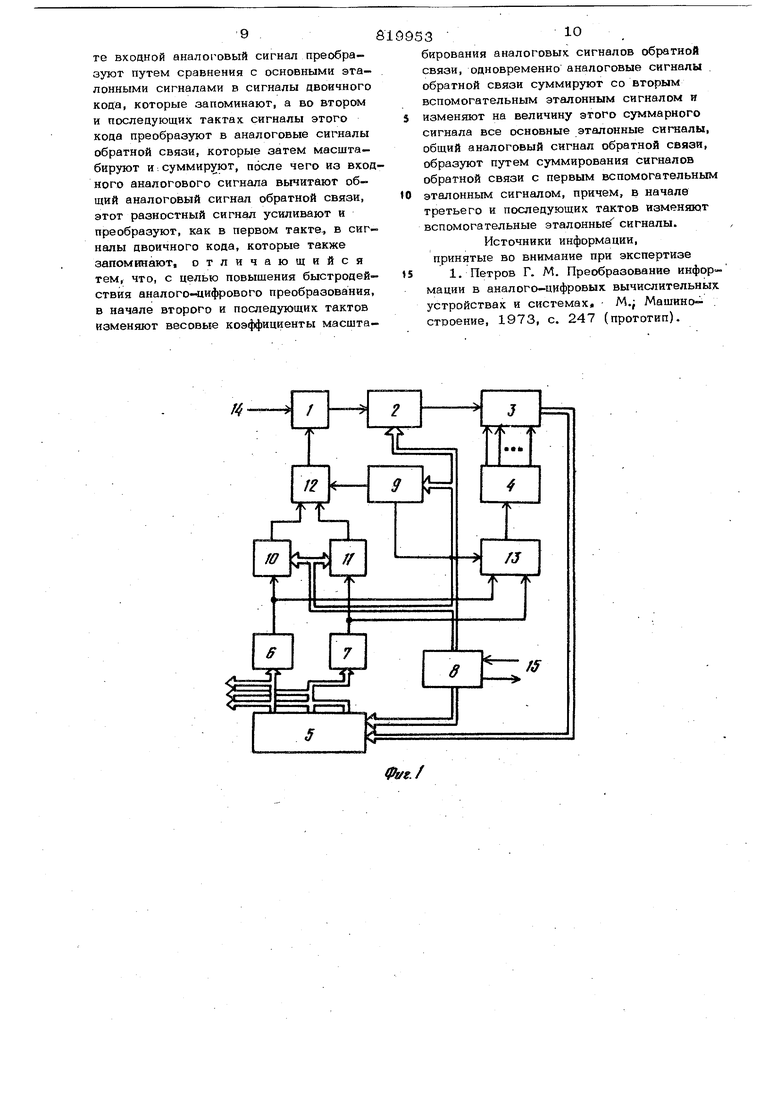

На фиг. 2 приняты следующие обозна ения: 16 - импульс исходного состояния, формируемый на одном из выходов блока управления, по которому начинается преобразование; 17 и 18 - сигналы на выходах первого и второго ЦАП 6 и 7; 18 - сигнал на выходе усилителя 2; 20 и 21 - начальный и конечный уровни выходного сигнала усилителя 2 на первом такте преобразования; 22 и 23 - конкретный и максимально-возможный интервалы времени, э течение которых происходит изменение сигнала на выходе усилителя 2; 24 - выходные импульсы блока 8, по которым выполняется считывание кода с выхода преобразователя 3 в регистр-счетчик 5; 25 и 26 максимально-Фозможные интервалы времени, в течение которых могут происходить изменения выходного сигнала усилителя во втором и третьем тактах преобразования; 27 - импульсы на интерфейсном вь1ходе 15 блока 8, по которым разрешается. передача кода результата преобразова ния.

Аналого-цифровое преобразование в этом преобразователе выполняется следующим образом. Сначала блок управления 8 вырабатывает импульс исходного состояния 16, которым гасятся счетчик 6 и блок формирования вспомогательных эталонных сигналов 9, а в усилителе 2 устанавливается наименьший коэффициент усиления К 1. Так как выходные сигналы ЦАП 6 и 7 в этот момент равны нулю и отсутствует сигнал на выходе блка 9, то входной,сигнал усилителя 2, поступающий с выхода аналогового вычитателя 1, равен входному аналоговому сигналу, подаваемому на первый вход вычитателя 1 по входной аналоговой шин 14. В результате этого на выходе усилителя 2 выходной сигнал начинает изменяться от предыдущего значения (уровень 20) и устанавливается через интервал времени 22 на уровне 21, который соответствует входному аналоговому сигналу.

Выходной сигнал усилителя 2 подаетс на вход преобразователя считывания 3, в котором преобразуется в сигналы парал.- лепьного двоичного кода. После истечения интервала времени 23 с момента появления сигнала 16, по сигналу 24, поступающему из блока 8, производится считывание этого двоичного кода и запис его в старшие разряды регистра-счетчика 5. Если значение коаа, считанного с выходов преобразователя 3, отличается от нулевого, то начинает изменяться выходной сигнал 17 первого ЦАП 6, который через некоторый момент времени устанав ливается на уровне, соответствующем с точностью данного такта преобразования, входнсялу аналоговому сигналу. Одновременно со считыванием К-разрядного кода в регистр-счетчик 5 блок 8 начинает подготавливать второй такт преобразования. При этом в усилителе 2 ус- .танавливается коэффициент усиления в 2 раз больший, чем в первом такте, открываются входы для считывания кода с выходов преобразователя 3 в средние разряды регистра-счетчика 5, коэффициен масштабирования в блоке 1О устанавлива ется равным (1 - 1/2 ), а в блоке 9 устанавливаются следующие значения вспомогательных сигналов: первого (для смещения выходного сигналаусипитеяя 2) и -ллЦ-иа)и второго (для смещения шкалы блока 4 и,--лА-2 - где Д. А г Aq- /2 - квант входного аналогового сигнала, Аа - диапазон измейения входного ана логового сигнала Начинает изменяться сигнал на выходе преобразователя 6, а за ним начинает изменяться и сигнал на выходе усилителя 2 При указанных выше значениях коэффициента масштабирования и первого дополнительного эталонного сигнала максималь но-возможное изменение сигнала на выходе усилителя 2 сокращается вдвое по сравнению с изменением аналогичного -. сигнала в преобразователе, выполненном на основе известного способа и содержащем аналоговый вычитатель, соединенный выходом через усилитель с управляемым коэффициентом усиления и преобразователь считывания с входами регистра, выходы которого через цифроаналоговый пре образователь соединены с первым входом аналогового вычитателя, второй вход которого соединен с шиной аналогового входа, причем выходы блока управления соединены с управляющими входами упомянутого усилителя и регистра. Действительно, предположим, что входной сигнал имеет значение А А (), где Н, , полученный в первом такте преобразования. Выходной сигнал блока о 10 Ащ.,| с учетом масштабирования будет равен Д А М (1 - ). Тогда для установившегося значения А у: (1, П) сигнала на выходе усилителя 2 при переходе от первого к второму такту преобразования и наличии сигнала обратной связи AQJ. - Ащ,- Ц можно написать следующее выражение: A,(I,ri)--(A,)(N,. Н/г дАЫ С -цзМ ААСА-ИгМ -2 - л. А (N 1-1/2). Таким образом, при указанных значениях входного аналогового сигнала и общего-сигнала обратней связи изменения сигнала на выходе усилителя 2 не происходит. В том случае, когда входной аналоговый сигнал отличается от значения Lt (N/t+1/2), т. е. находится в пределах от .A до ( N +1/2 )ДА или от () ДА до (N +1) ДА, то изменение выходного сигнала при переходе от первого к второму такту не будет превышать А у /2. При входном сигнале N лА или .+ l) Л А будет наибольшее изменение выходного сигнала усилителя 2. Это изме,нёние для АЙХ( будет равно (l.lDwakt-Ау(1,П)Аакс-(К 1-ЛдА ДА;2 - 1Ч-1/. т. е. практически в два раза меньше, чем в указанном преобразователе, основанном на известном способе. Уменьшегние диапазона изменения выходного сигнала приводит к эквивалентному уменьшению максимально-возможного времени установления сигнала на выходе усилителя Такту преобразования, следовательно повышается быстродействие преобразователя. Через интервал времени 25, определяемый временем установления сигнала на выходе усилителя 2 при переходе к второму такту при его максимально возможном изменении на А /2, производится считывание кода с выходов преобразователя 3 в средние К- разрядов регистра Следует заметить, что этот интервал времени несколько больше аналогичного интервала 23 первого такта, так как при изменении коэффициента усиления усилителя 2 в 2 раз изменяется также и скорость изменения сигнала на выходе усилителя. Объясняется это тем, что реальные усилители эквиваленты РС-звену, в котором одновременно с увеличением коэффициента усиления увеличивается значение сопротивления Р , что приводит к увеличению постоянной времени такого звена. При подготовке третьего такте преобразования блок 8 устанавливает коэффициент усиления усилителя 2 равным 2 а также формирует сигналы, управляющие изменением коэффициента масштабирования в блоках 1О и 11 и изменением вн ходных сигналов блока 9. Для .сохранения изменения выходного сигнала усилителя 2, не превышающего величины А (/2, также и при перекоде к третьему такту, значение первого вЬпо могательного эталонного сигнала устанав ливается равным 1/2 (1 - 1/2 ) ЛА, коэффициенты масштабирования в блоках Юн 11 устанавливаются равными соответств-рнно (1 - 1/2) и (1 - 1/2), в значении второго вспомогательного эта лонного сигнала устанавливается равным , Л А (г +1) в случае, если входной сигнал имеет значение ), где N{ .- код, полученный во втором та те преобразования, то выходной сигнал усилителя 2 при переходе к третьему такту не будет.изменяться, аналогично тому, как это имее место при переходе ко второму такту пр значении входного сигнала, равного /S.A(). Через интервал времени 26, равный максимальному времени установления си нала на выходе усилителя 2, которое определяется новым значением постоянно времени, изменившейся (увеличившейся) с изменением коэффициента усиления при переходе от второго к третьему такту преобразования, выполняется запись кода с выходов преобразователя 3 в младшиеК - разряды регистра 5. На этомГ п роцесс трехтактового аналого-41Ифрового преобразования заканчивается, и код реультата преобразования с выхоаов регистра 5 может быть передан в микророцессор по соответствующему сигналу отовности результата преобразования, ередаваемого из блока 8 по одному з выходов 15. В общем случае для И -тактового реобразования по предложенному спосоу справедливо следующее выражение для игнала обратной связи AQ.. .- -го преобазованияAocj- Al i/a - - 1|,(...и. Здесь коэффициенты при Ц определяют значение масштабирующих коэффициентов блоков масштабирования, а последний член выражения - значение сигнала смещения на каждом такте преобразования. Сигнал смещения эталонных уровней сравнения J , формируемый блоком 13, в рассмотренном преобразователе определяется следующим выражением: CMj Ч|i(jH)(.|2). В этих выражениях ЛА - квант на первом такте преобразования; - значение кодов преобразования на камсцом i -м такте; 1-1, 2,( j - 1); К - число параллельно получаемым разрядов кода в каждом такте преобразования. Таким образом, в h -тактном парал- лельно-последовательном преобразователе, выполненном на основе рассмотренного способа, в котором обеспечивается формирование сигналов и ,| в соответствии с вышеприведенными формулами, достигается уменьшение максимально-возможного изменения выходного сигнала усилителя 2 на каждом такте преобразования в два раза по сравнению с вышеуказанным преобразователем, основанным на известном способе преобразования. Это эквивалентно почти такому же сокращению времени выполнения каждого такта преобразования, т. е. практически двухкратному повышению- быстродействия пре- образования. При этом реализация вновь введенных операций не Tpe6yeTi использования более быстродействующих элементов и узлов, чем те, на которых выполняется указанный известный преобразователь. Формула изобретения Способ параллельно-последовательного аналого-цифрового преобразования заключающийся в том, что в первом такч re входной аналоговый сигнал преобразуют путем сравнения с основными эталонными сигналами в сигналы двоичного кода, которые запоминают, а во втором и последующих тактах сигналы этого кода преобразуют в аналоговые сигналы обратной связи, которые затем масштабируют и суммир; ют, после чего из вход ного аналогового сигнала вычитают общий аналоговый сигнал обратной связи, этот разностный сигнал усиливают и преобразуют, как в первом такте., в сигналы двоичного кода, которые также запоминают, отличающийся тем, что, с целью повышения быстродействия аналого-цифрового преобразования, в начале второго и последующих тактов изменяют весовые коэффициенты масшта310. бирования аналоговых сигналов обратной связи, одновременно аналоговые сигналы . обратной связи суммируют со вторым вспомогательным эталонным сигналом и изменяют на величину этого суммарного сигнала все основные эталонные сигналы, общий аналоговый сигнал обратной связи, образуют путем суммирования сигналов обратной связи с первым вспомогательным эталонным сигналом, причем, в начале третьего и последующих тактов изменяют вспомогательные эталонные сигналы. Источники информации, принятые во внимание при экспертизе 1. Петров Г. М. Преобразование информации в аналого-цифровых вычислительных устройствах и системах, М.; Машиностроение, 1973, с. 247 (прототип).

6

YJ

17

JL

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельно-последовательный аналого- цифровой преобразователь | 1978 |

|

SU790287A1 |

| Аналого-цифровой преобразователь двухтактного считывания | 1972 |

|

SU447828A1 |

| Устройство аналого-цифрового преобразования | 1991 |

|

SU1807559A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1277396A1 |

| СПОСОБ КОРРЕКЦИИ ПОГРЕШНОСТЕЙ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2399156C1 |

| Параллельно-последовательныйАНАлОгО-цифРОВОй пРЕОбРАзОВАТЕль | 1978 |

|

SU819952A1 |

| Система многоканального приема и преобразования в код аналоговых сигналов | 1978 |

|

SU758511A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1197079A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1320901A1 |

| Система адаптивного управления параметром технологического процесса | 1988 |

|

SU1620989A1 |

/3

n

4 21

Фог.

Авторы

Даты

1981-04-07—Публикация

1979-05-04—Подача