(54) ЛРИФМЕТИЧЕСКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционное устройство микропроцессора | 1979 |

|

SU1164719A1 |

| Микропроцессор с контролем | 1981 |

|

SU1016788A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Арифметическое устройство для базовой операции быстрого преобразования фурье | 1980 |

|

SU875387A1 |

| Управляемый арифметический модуль | 1979 |

|

SU832553A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| Устройство для формирования адресов процессора быстрого преобразования фурье | 1987 |

|

SU1499373A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

1

Изобретение относится к автоматике и вычислительной технике и предназначено для реализации логичеких и арифметических операций.

Известно устройство, содержащее блок логического умножения, первый и второй полусумматоры, триггер результата, блок контроля на нуль блок разделения и триггер переноса li .

Недостатком данного устройства является невысокое, быстродействие, обусловленное тем, что операции выполняются над операндом в последовательном коде.

Наиболее близким по технической сущности к предлагаемому является арифметическо-логическое устройство параллельного действия, содержащее накапливающий регистр, регистр cjfaгаемого, цепи передачи кода из регистра слагаемого в накапливающий регистр, блок формирования переносо и цепи выдачи кода, выполненные на триггерах с управляемым счетным входом и логических элементах И и ИЛИ 2 .

Недостатком этого устройства явлется малое быстродействие, обусловленное необходимостью выполнения

каждой операции дважды (один раз для выдачи результата, второй - для восстановления содержимого накапливающего регистра). Кроме этого, ограничены возможности устройства: нет операций счета (±1 к одному из операндов) , нет операций сдвига и не обеспечивается параллельная обработка адресов и данных.

0

Цель изобретения - повышение быстродействия и расширение функциональных во.зможностей устройства за счет увеличения числа выполняемых операций (операциисдвига над зна5чениями адресов).

Эта цель достигается тем, что устройство содержит комбинационный сумматор, второй, третий и четвертый коммутаторы, две группы элементов 0 и, причем управляющий вход устройства подключен к управляющему входу первого коммутатора, выход которого .является информационным выходбм ариф етическо-логического устройства,

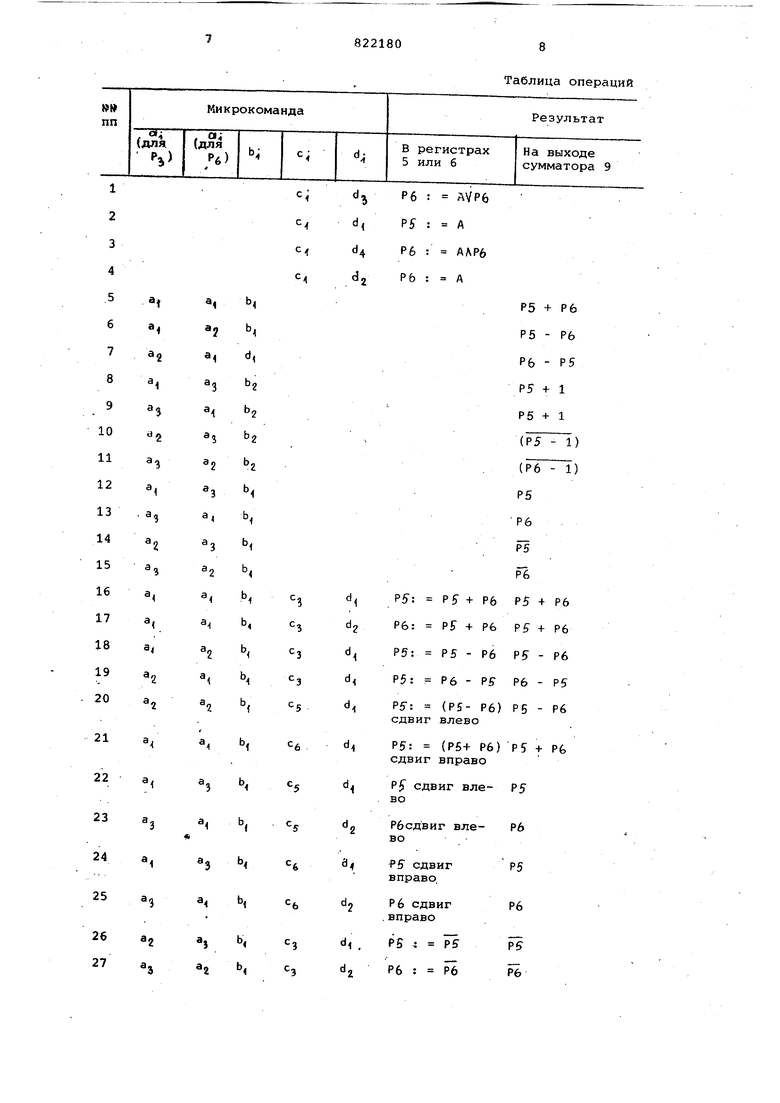

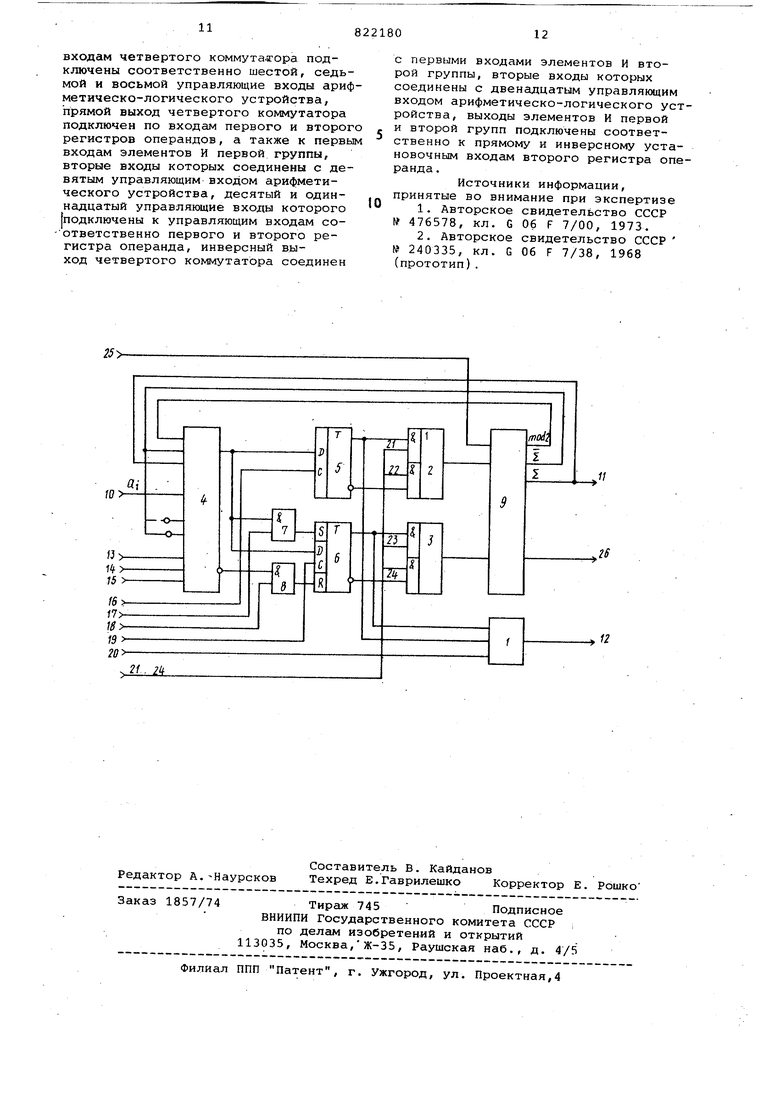

5 прямые выходы первого и второго регистров операндов подключены к первым соответственно второго и третьего коммутаторов, к первым управляющим входам которых подключены соQответственно второй н третий, а ко вторым - соответственно четвертый и пятый управляквдие входы арифметичес логического устройства,инверсные вы ходы первого и второго регистров оп рандов подключены ко вторым входам соответственно второго и третьего коммутаторов, выходы которых подклю ны соответственно к первому и второ информационным входам комбинационно сумматора, вход переноса которого с динен с входом переноса арифметичес логического устройства, выход перен са комбинационного сумматора подключен к выходу переноса арифметическо-логического устройства,, инфор мационный выход которого соединен с прямым выходом комбинационного сумматора и с первым информационным вх дом четвертого коммутатора, ко второму и третьему информационным входам которого подключены инверсны выход и выход суммы-по модулю два комбинационного сумматора, а к четвертому информационному входу подключен информационный вход арифметическо-логического устройства, к трем управляющим входам четвертого коммутатора подключены соответствен но шестой, седьмой и восьмой управляющие входы арифметическо-логического устройства, прямой выход четвертого коммутатора подключен по входам первого и второго регистров операндов, а также к первым входам элементов И первой группы, вторые входы которых соединены с девятым управляющим входом арифметическологического устройства, десятый и одиннадцатый управляющие входы которого подключены к управляющим входам соответственно первого и вто рого регистров операнда, инверсный выход четвертого коммутатора соединен с первыми входами элементов И второй группы, вторые входы которых соединены с двенадцатым управляющим входом арифметическо-логического устройства, выходы элементов И первой и второй групп подключены соответственно к прямому и инверсному установочным входам второго регистра операнда. На чертеже представлена схема устройства. Устройство содержит ком таторы 1-4, регистры 5 и 6 операндов, эле менты И 7 и 8, комбинационный сумматор 9, входную шину 10,-выходные шины 11 и 12, управляющие входы 13-24, вход 25 переноса, выход 26 . переноса. Коммутатор 1 коммутирует на выходную шину 12 содержимое одного из регистров 5 и 6 операндов. Коммутаторы 2 и 3 служат для выдачи операн . дов в прямом и обратном кодах на сумматор 9. Коммутатор 4 служит для подключения требуемой шины ко входа регистров 5 и 6 операндов. Регистры б операндов предназначеньл для ения операндов во время операций анения результата после операции у операциями). Регистры могут выполнены на 0-триггерах с реакна один из фронтов по входу С. енты И 7 и 8 служат для выполя совместно с коммутатором 4 аций логического сложения и логиого умножения. Комбинационный атор 9 формирует арифметическую у и сумму по модулю 2 регистров б операндов. стройство работает следующим обм.. ыполнение операций в устройстве ставляем в виде совокупности оопераций логическими выражения1), (2) и (3), в которых проыми буквами обозначены операнды, чными - микрооперации. АС )d,P5a)bi (P,a.)b,.)l C,d, А - операнд шины 10; содержимое регистра 5 операндов ; содержимое регистра б операндов ; микроопераций передачи операндов на вход сумматора, в том числе передача на вход сумматора прямого кода операнда; передача на вход сумматора обратного кода операнда; запрет передачи на сумматор: микрооперации сумматора, в том числе арифметическое сложение; увеличение содержимого сумматора на единицу; сумма по модулю два; микрооперации коммутации операнда со входов коммутатора 4 на его вход, в том числе передача операнда с шины 10; передача суммы по модулю два; передача арифмети5 еской суммы; передача обратного кода арифметической суммы; передача арифметической суммы со сдвигом влево; передача арифметической суммы со сдвигом вправо; запрет передачи; микрооперации ввода информации с выхода коммутатора 4 в регистры 5.и 6 операндов , в том числе ввод в регистр 5 операндов со стиранием предыдущего значения; ьвод в регистр б операндов со стиранием предьщущего значения; логическое сложение с содержиг.шм регистра б операндов и ввод результата в регистр б;. логическое умножение с содержимым регистра 6 опер дов и-ввод результата в ре гистр б ; запрет ввода в регистры 5 и 6 операндов. Микрооперации выполняются с помощью коммутаторов 2 и 3 под упра лением сигналов . Так, при еди ничном значении сигнала 21 и нулево значении сигнала 22 через коммутато 2 проходит прямой код регистра 5 операнда (микрооперация а), при ед ничном значении сигнала 22 и нулевом - 21 проходит обратный код регистра 5 (32), при нулевых значениях сигналов 21 и 22 операнд регистра 5 через коммутатор 2 не проходит (а). Аналогично проводятся микрооперации над операндами ре.гист ра б под действием сигналов 23 и 24 Микрооперации Ь; выполняются сум матором 9. Увеличение содержимого сумматора на единицу (микрооперация Ь) производится сигналом в цепи 25, которая является входом пе реноса в младший разряд сумматора. Сумма по модулю два (Ьд) дополнител ных затрат в оборудовании сумматора не требует, поскольку может быть по лучен как промежуточный результат при формировании арифметической сум мы. Для выполнения операции с задает ся ее двоичный номер по цепям 1315, и коммутатор 4 коммутирует на выход операнд с соответствующего на правления. Микрооперации d выполняются региртрами 5 и б операндов и элементами 7 и 8 по управляющим сигналам 16-19 (соответственно для микроопераций d , d, d4 с12.Ввод в регистры 5 и б операндов (d и dg.) осуществля ется по заднему фронту управляющих сигналов, поступающих на входы с. При логическом сложении операнд с коммутатора 4 ,через элемент И 7 и единичный вход S вводится в регистр Поскольку через нулевой вход R регистра б в этой микрооперации запис запрещена (по цепи 18 должен быть нулевой сигнал), то все разряды реги стра б, находящиеся в единичном состоянии, в этом же состоянии и остаются, т.е. выполняется лотическое сложение операнда с выхода коммутатора 4 с содержимым регистра б. При логическом умножении обратный код операнда с коммутатора 4 через элементы И 8 поступает на нулевые входы R регистра 6, за счет чего переводятся в нулевое состояние разряды регистра, соответствующие единичным разрядс1М обратного кода операнда . Выполнение операнда арифметикологическим устройством в целом задается установкой в одном такте управляющих сигналоь, вызывающих микрооперации в соответствии с логическими выражениями (1), (2) и (3). Группа операций, описанных выражением (1) выполняется над операндами шины 10, результат заносится в один из регистров 5 или 6. Например, при установке по цепям 13-15 кода, соответствующего направлению шины 10, и сигнала по цепи 17 (заданы микрооперации с и dj. ранд с шины 10 проходит через коммутатор 4 и логически складывается с содержимым регистра б, т.е. проводится операция Р Рассмотренная операция записана в П.1 таблицы операций. Другие возможные операции по выражению (1) приведены в пп.2-4 таблицы операций и выполняются аналогично. Операции по выражению (2) выполняются над содержимым регистров 5 и , б, результатом является выход сумматора 9.Например, при установке в единичное состояние цепей 21 и 24 (микрооперация d для Р5 и d2 для Р6), на вход сумматора поступают прямой код операнда с регистра 5 и обратный код с регистра 6, на выходе сумматора получим Р5-Р6. Эта операция приведена в п.6 таблицы. Другие возможные операции по данному выражению приведены в ,пп. 5-15 табл. Операции ро выражению (3) выполняются над содержимым регистров 5 и б, результат заносится в один из этих же регистров.. Например, при установке единичного состояния сигналов 19,24, 25 и комбинации из 13-15 для передачи обратного кода с сумматора, выполняются одновременно микрооперации а 2 (для Рб), С4 и dj а в целом выЛлнится операия Рб : Рб - 1.

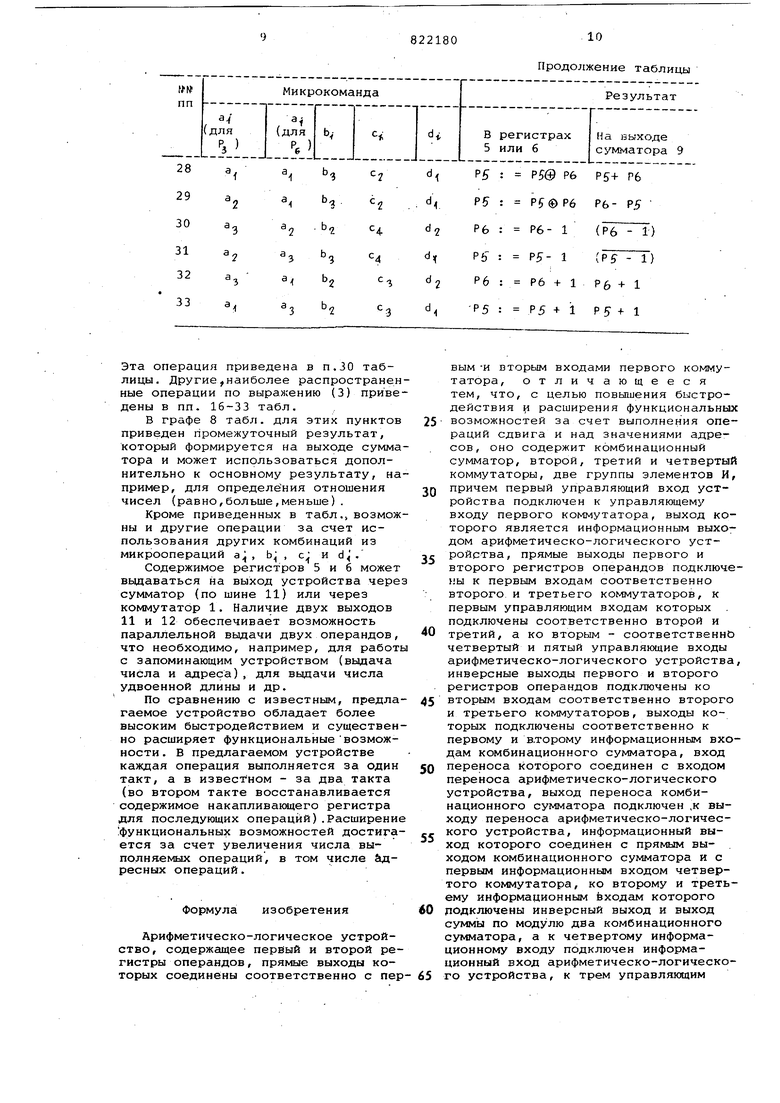

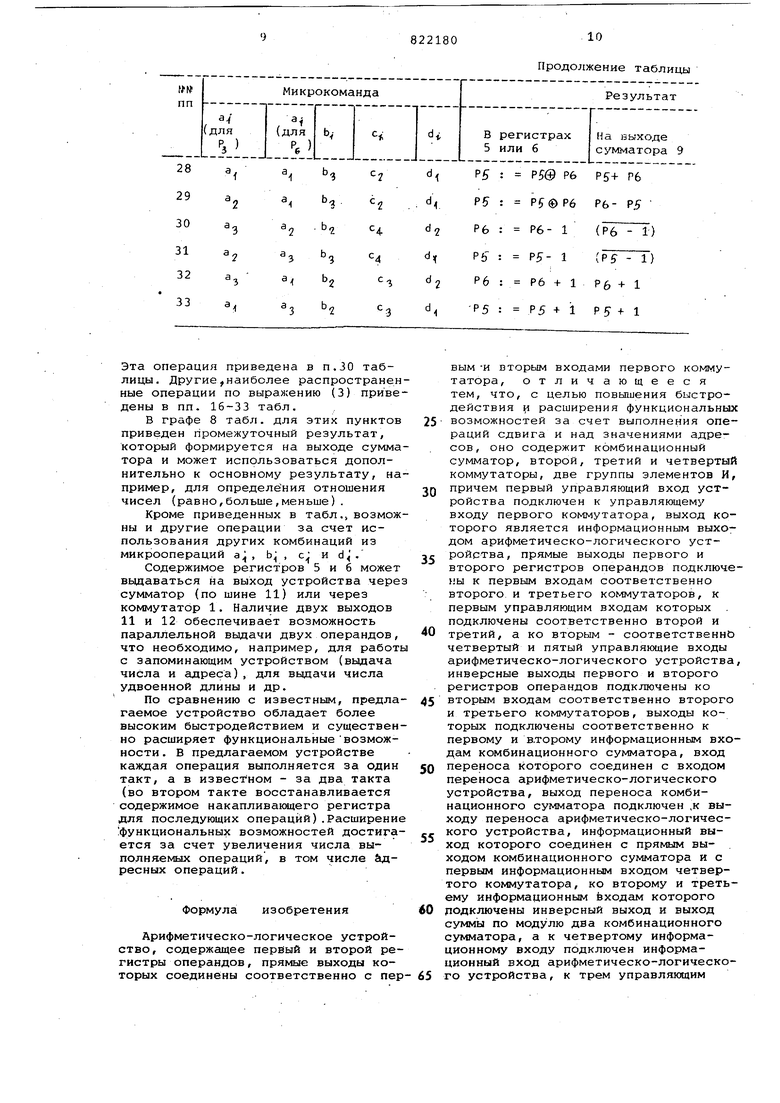

Таблица операций Эта операция приведена в п.30 таблицы. Другие,наиболее распростране ные операции по выражению (3) приве дены в пп. 16-33 табл. В графе 8 табл. для этих пункто приведен промежуточный результат, который формируется на выходе сумм тора и может использоваться дополнительно к основному результату, н пример, для определения отношения чисел (равно,больше,меньше). Кроме приведенных в табл. возмо ны и другие операции за счет использования других комбинаций из микроопераций а , Ь , с и . Содержимое регистров 5 и б може выдаваться на выход устройства чер сумматор (по шине 11) или через коммутатор 1. Наличие двух выходов 11 и 12 обеспечивает возможность параллельной выдачи двух операндов что необходимо, например, для работ с запоминающим устройством (выдача числа и адреса), для выдачи числа удвоенной длины и др. По сравнению с известным, предла гаемое устройство обладает более высоким быстродействием и существен но расширяет функциональныевозможности . В предлагаемом устройстве каждая операция выполняется за один такт, а в известном - за два такта (во втором такте восстанавливается содержимое накапливакицего регистра для последующих операций).Расширени функциональных возможностей достига ется за счет увеличения числа выполняемых операций, в том числе йщресных операций. Формула изобретения Арифметическо-логическое устройство, содержащее первый и второй ре гистры операндов, прямые выходы которых соединены соответственно с пе

Продолжение таблицы вым -и вторым входами первого коммутатора, отличающееся тем, что, с целью повышения быстродействия и расширения функциональных возможностей за счет выполнения операций сдвига и над значениями адресов, оно содержит комбинационный сумматор, второй, третий и четвертый коммутаторы, две группы элементов И, причем первый управляющий вход устройства подключен к управляющему входу первого коммутатора, выход которого является информационным выходом арифметическо-логического устройства, прямые выходы первого и второго регистров операндов подключены к первым входам соответственно второго и третьего коммутаторов, к первым управляющим входам которых подключены соответственно второй и третий, а ко вторым - соответственно четвертый и пятый управляющие входы арифметическо-логического устройства, инверсные выходы первого и второго регистров операндов подключены ко вторым входам соответственно второго и третьего коммутаторов, выходы которых подключены соответственно к первому и в.торому информационным входам комбинационного сумматора, вход переноса которого соединен с входом переноса арифметическо-логического устройства, выход переноса комбинационного сумматора подключен ,к выходу переноса арифметическо-логического устройства, информационный выход которого соединен с прямым вы- . ходом комбинационного сумматора и с первым информационным входом четвертого коммутатора, ко второму и третьему информационным входам которого подключены инверсный выход и выход суммы по модулю два комбинационного сумматора, а к четвертому информационному входу подключен информационный вход арифметическо-логического устройства, к трем управляющим

входам четвертого коммута ора подключены соответственно шестой, седьмой и восьмой управляющие входы арифметическо-логического устройства, прямой выход четвертого коммутатора подключен по входам первого и второго регистров операндов, а также к первым входам элементов И первой группы, вторые входы которых соединены с девятым управляющим входом арифметического устройства, десятый и одиннадцатый управляняцие входы которого подключены к управляющим входам со ответственно первого и второго регистра операнда, инверсный выход четвертого коммутатора соединен

с первыми входами элементов И второй группы, вторые входы которых соединены с двенадцатым управляющим входом арифметическо-логического устройства, выходы элементов И первой и второй групп подключены соответственно к прямому и инверсному установочным входам второго регистра операнда .

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-04-15—Публикация

1979-06-06—Подача