(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СИГНАЛА

ПЕРЕНОСА ПРИ СУММИЮВАНИИ МНОГОФАЗНЫХ

КОДОВ2

.Изобретение относится к цифровой технике и предназначается в основном для использования в электроприводах постоянного и переменного тока с цифровым управлением, а также системах автоматики.

Известны цифровые электроприводы, где используется сложение цифровыхсигнсшов в старшем разряде многофазного кода с учетом результата сложения- (сигнала переноса) в младших разрядах и .

Известен сумматор для работы с многофазными кодами (основание пу2) где применяется матричный сумматор размерами пхп и матрица сложения переноса размером 2хп. Из этого сумматора может быть выделена схема . формирования сигнала переноса в старший разряд, которая содержит матрицу слО|Жения переноса и часть элементов квадратной матрицы ниже главной диагонали 2.

Отличительной особенностью такого, устройства являетсявысокое быстродействие, но оно содержит много элементов и требует многократных преобразований из кода в код.

Наиболее близким к изобретению является устройство для формирования сигнала переноса,которое может быть выделено из сумматора, при этом один операнд поступает непосредственно в многофазном коде, а второй преобразуется в блоке дешифратора в промежуточный код. Входные шины первого операнда поступают на вход блока сложения переноса размером 2хп/2, выходные шины которого совместно с

10 выходными шинами блока дешифра ции поступают в матричный сумматор размерами п/2хп/2, часть элементов этого матричного сумматора участвует в формировании сигнала переноса

15 в старший разряд, выходные шинц . этих элементов матричного сумматора соединены с выходами логического блока, другие входные шииы которого соединены с шинами операндов разря20да и шиной переноса из младшего разряда 3 .

Данное устройство содержит меньше элементов, но также требует многократных преобразований из кода в код, и, кроме того, количество обо25рудования его все же сравнительно

велико.

Цель изобретения - повышение быстродействия и уменьшение количества

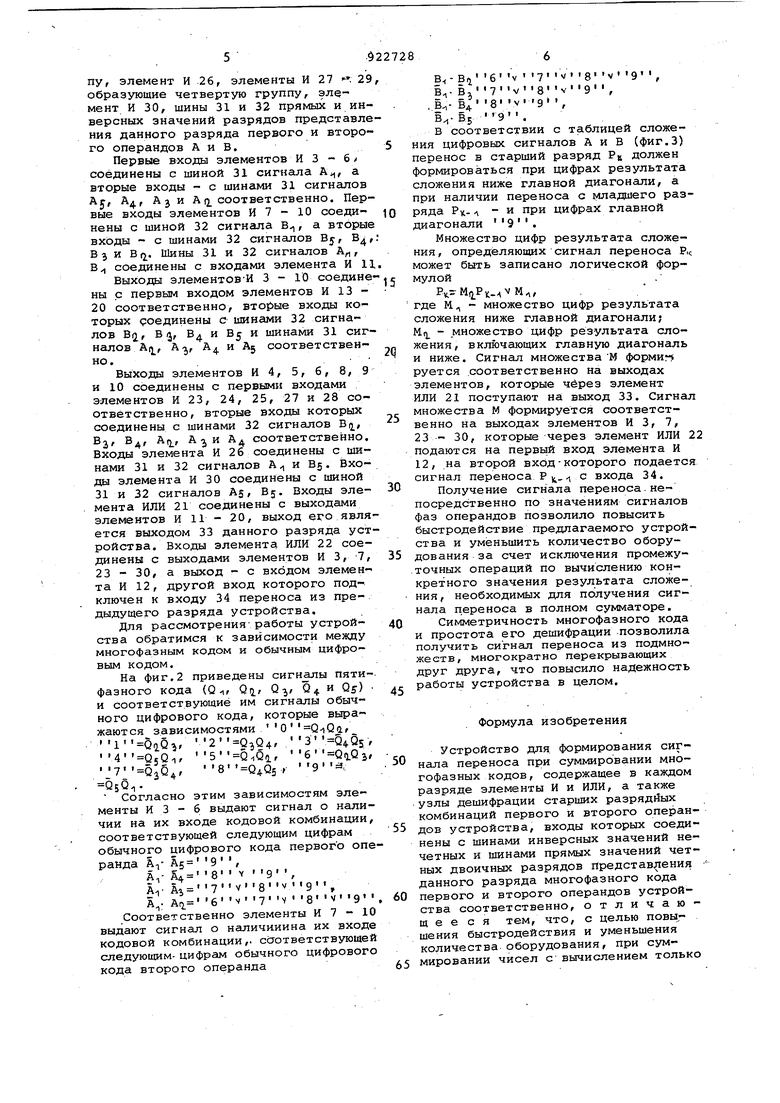

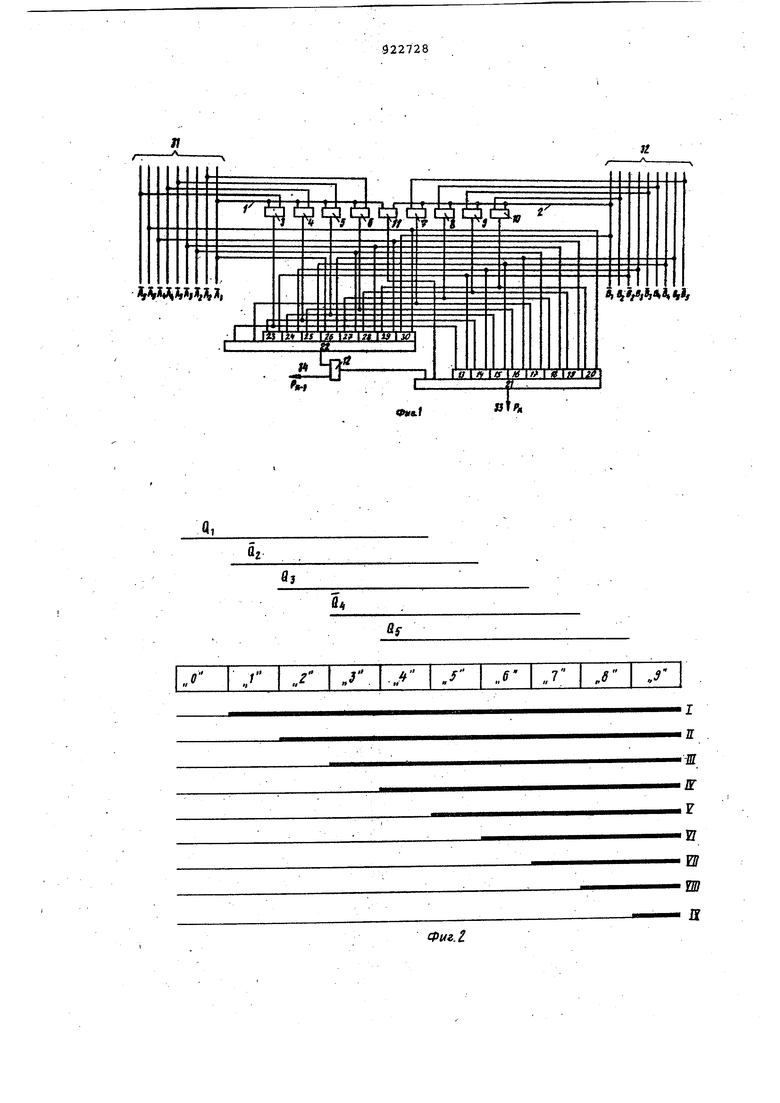

30 оборудования.Поставленная цель достигается тем, что в устройстве формирования сигнала переноса при суммировании многофазных кодов, содержащем в каж дом разряде элементы И и ИЛИ, а так же узлы дешифрации старших разрядных комбинаций первого и второго операндов устройства, входы которых соединены с шинами инверсных значе. НИИ нечетных и шинами прямых значений четных двоичных разрядов представления данного разряда много фазного кода первого и второго операндов устройства соответственно при суммировании чисел с вычисление только значения переноса первые вхо |Ды элементов И первой группы соединены с соответствующими выходами уз ла дешифрации старших разрядных ком бинаций первого операнда, второй вход каждогр нечетного элемента и первой группы соединен с шиной инверсного значения соответствующего четного двоичного разряда представления данного разряда многофазного кода второго операнда устройству, второй вход каждого четного элемента И первой группы соединен с шиной прямого значения последующего .нечет ного двоичного разряда представления данного разряда .многофазного кода второго операнда устройства, первые входы элементов И второй гру пы соединены с соответствующими выходами узла дешифрации старших разрядных комбинаций второго операнда, второй вход каждого нечётного элемента И второй группы соединен с ши ной инверсного значения соответствующего нечетного двоичного разряда представлений данного разряда много фазного кода первого операнда устройства, второй вход каждого четного элемента И второй группы соедине с шиной прямого значения последующего нечетного двоичного разряда представления данного разряда много файного кода первого операнда устройства, -выходы элементов И первой и второй групп и первого и второго элементов И соединены с входами пер вого элемента ИЛИ, выход которого соединен с выходом -переноса из данного разряда устройства, первые входы элементов И третьей и четвертой групп соединены с выходами узлов дешифрации старших разрядных комбинаций первого и второго операндов соответственно, начиная с вторых выходов, второй вход каждого нечетного элемента И третьей группы соединен с шиной инверсного значения соответствующего четного двоичного разряда представления данного разряда многофазного кода второго операнда- -устрой ства, второй вход каждого четного элемента И третьей группы соединен с шинойпрямого значения последующего нечетного двоичного разряда представления данного разряда многофазного кода второго операнда устройства за исключением последнего двоичного разряда, второй вход каждого нечетного элемента И четвертой группы соединен с шиной инверсного значения соответствующего четного двоичного разряда представления данного разряда многофазного кода первого операнда устройства, второй вход каждого четного элемента И четвертой группы соединен с шиной прямого значения последующего нечетного двоичного разряда представления данного разряда многофазного кода первого операнда устройства за исключением последнего двоичного разряда, входы первого элемента И соединены с шинами инверсных значений первых двоичных разрядов представления данного разряда многофазного кода первого и второго операндов устройства, выходы элементов И третьей и четвертой группы, выходы третьего . и четвертого элементов И и первые выходы узлов дешифрации старших разрядных комбинаций первого и второго операндов соединены с входами второго элемента ИЛИ, выход которого подключен к первому входу второго элемента И, второй вход которого соединен с ВХ.ОДОМ переноса в данный разряд устройства, входы третьего элемента И соединены с шиной инверсного значения первого двоичного разряда представления данного разряда многофазного кода первого операнда устройства и с шиной прямого значения последнего двоичного разряда представления данного разряда многофазного кода второго операнда устройства, входы четвертого элемейта И соединены и шиной инверсного значения первого двоичного разряда представления данного разряда многофазного кода второго операнда устройства и с шиной прямого значения последнего двоичного разряда представления данного разряда многофазного : кода первого операнда устройства. На фиг.1 приведена функциональная схема одного разряда устройства;на фиг.2 - зависимость между сигналами пятифазного кода и сигналами обычного десятичного кода; на фиг.З таблица сложения. Устройство содержит узлы 1 и 2 дешифрации старших разрядных комбинаций первого и второго операндов, содержащие элементы И 3 - б-. ,и элементы И 7 - 10 соответ-ственко, элементы И 11 и 12, элементы И 13 - 16, образующие первую группу, элементы И 17, - 20, образующие вторую группу, элементы ИЛИ 21 и 22, элементы И 23 - 25, образующие третью группу, элемент И 26, элементы И 27 i. 29 образующие четвертую группу, элемент И 30, шины 31 и 32 прямых и инверсных значений разрядов представления данного разряда первого и второго операндов А и В.

Первые входы элементов И 3 - 6 соединены с шиной 31 сигнала А,, а вторые входы - с шинами 31 сигналов Ау/ А, АЗ и А fj соответственно. Первые входы элементов И 7 - 10 соединены с шиной 32 сигнала В, а вторые входы - с шинами 32 сигналов By, В Вз и В 0. Шины 31 и 32 сигналов А,,, Bxf соединены с входами элемента И Ц

Выходы элементовИ 3 - 10 соединены с первым входом элементов И 13 20 соответственно, вторые входы которых соединены с шинами 32 сигналов Вд, В (J, В и Bt; и шинами 31 сигналов А|, Ат|, А и Ag соответственно..

Выходы элементов И 4, 5, б, 8, 9 и 10 соединены с первыми входами элементов И 23, 24, 25, 27 и 28 соответственно, вторые входы которых соединены с шинами 32 сигналов Bi, Bj, В, А(, Ад соответственно. Входы элемента И 26 соединены с шинами 31 и 32 сигналов А и Вд. Входы элемента И 30 соединены с шиной 31 и 32 сигналов AS, BS- Входы элемента ИЛИ 21 соединены с выходами элементов И 11 - 20, выход его является выходом 33 данного разряда устройства. Входы элемента ИЛИ 22 соединены с выходами элементов И 3, -7, 23 - 30, а выход - с входом элемента И 12, другой вход которого подключен к входу 34 переноса из предыдущего разряда устройства.

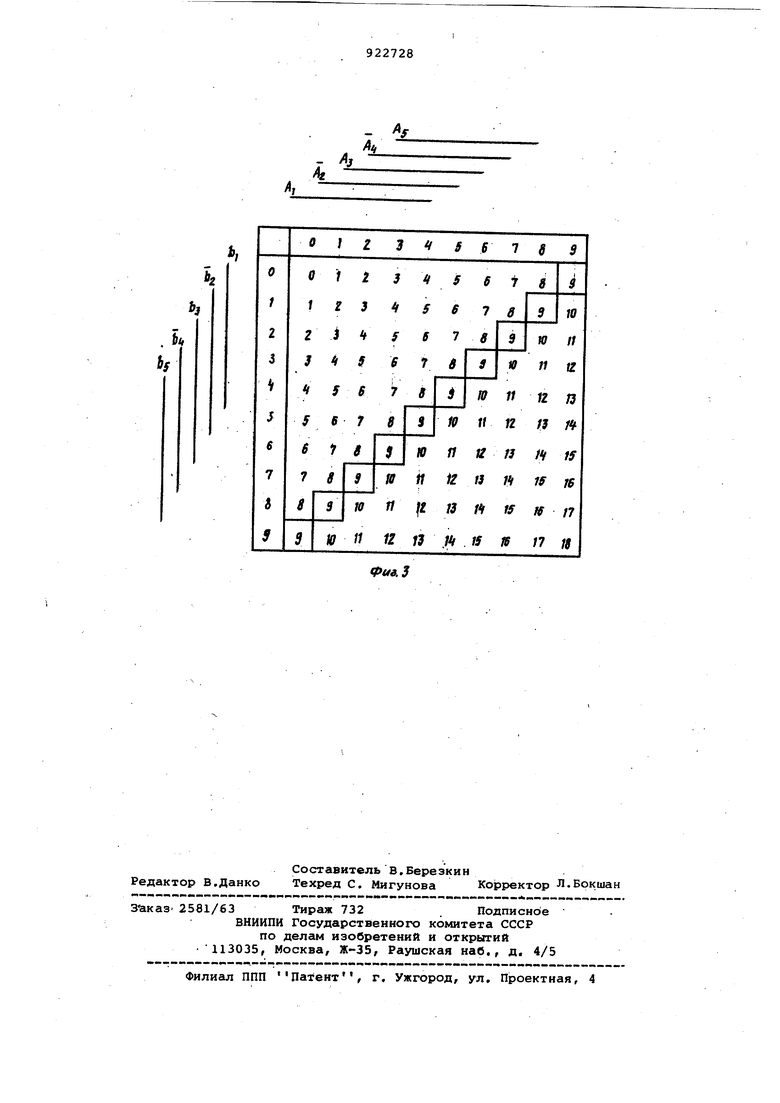

Для рассмотрения-работы устройства обратимся к зависимости между многофазным кодом и обычным цифровым кодом.

На фиг.2 приведены сигналы пятифазного кода (Q , QQ, Q , Qj) и соответствующие им сигналы обычного цифрового кода, которые выражаются зависимостями О

2 9з04 , ,, ,Qi, .Q3, 7 ., , Q5Q,.

Согласно этим зависимостям элементы И 3 - 6 выдают сигнал о наличии на их входе кодовой комбинации, соответствующей следующим цифрам обычного цифрового кода первого операнда AT 9 ,

А,- 4 8- - 9 ,

А. А,,: 7 9,

А.- 6 V 7 V 8 V 9

м: Соответственно элементы И 7 - 10 выдают сигнал о нгшичииина их входе кодовой комбинации,. саоТветствующей следующим- цифрам обычного цифрового кода второго операнда

B -Bfi6v7 8v9,

BV Вл , , §4 8 W -9 ,

9.

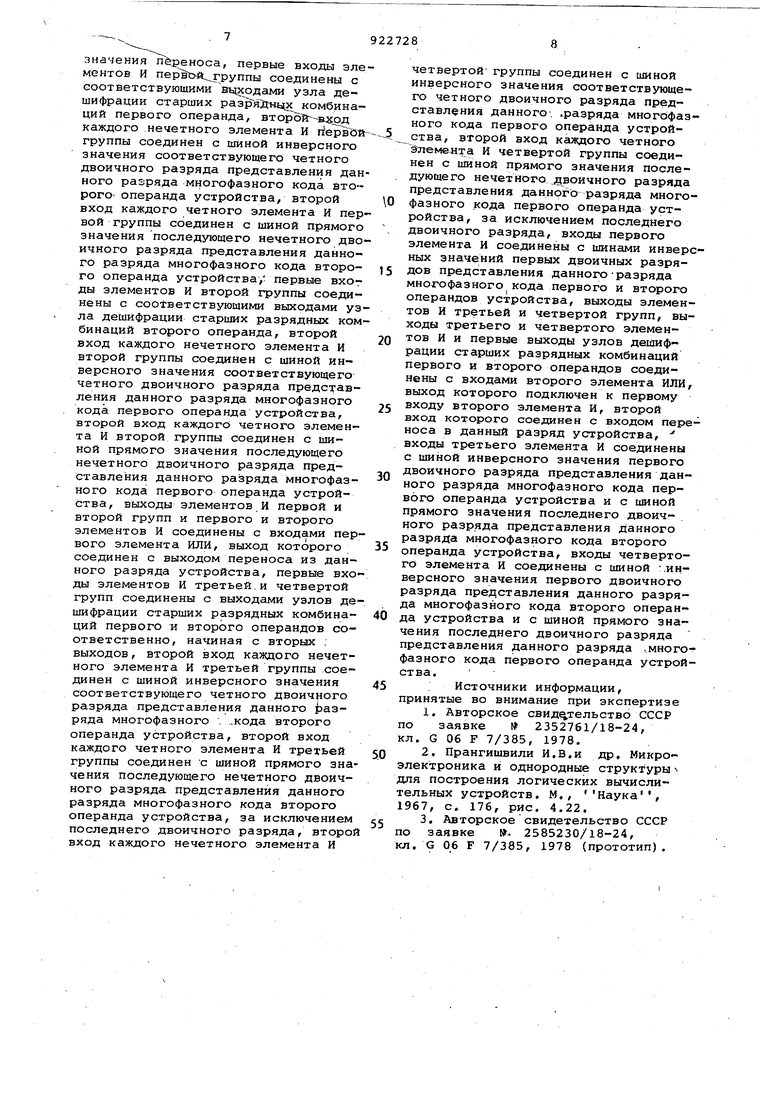

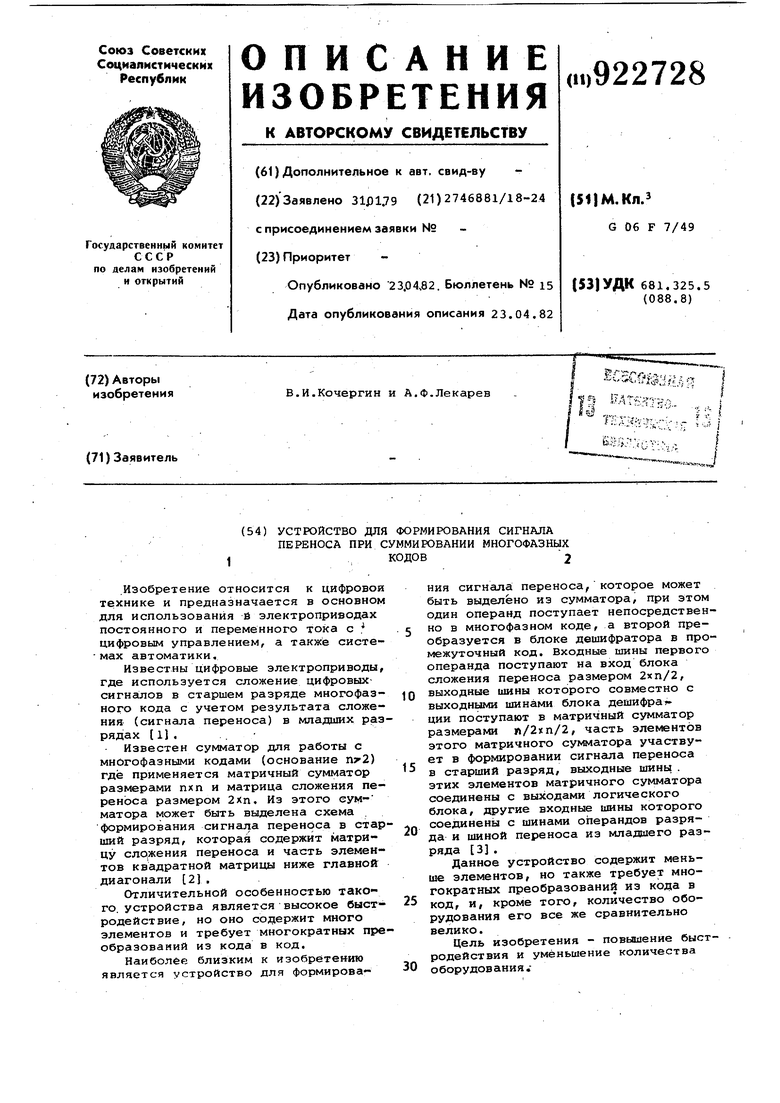

В соответствии с таблицей сложения цифровых сигналов А и В (фиг.З) перенос в старший разряд РК должен формироваться при цифрах результата сложения ниже главной диагонали, а при наличии переноса с младшего разряда РК-л - и при цифрах главной

0 диагонали 9 .

Множество цифр результата сложения , определяющих сигнал переноса Р,; может быть записано логической формулой

,

где М - множество цифр результата сложения ниже главной диагонали; М.Г1 - множество цифр результата сложения, включающих главную диагональ и ниже. Сигнал множестваМ формиг руется .соответственно на выходах элементов, которые через элемент ИЛИ 21 поступают на выход 33. Сигнал множества М формируется соответст5венно на выходах элементов ИЗ, 7, 23 - 30, которые через элемент ИЛИ 22 подаются на первый вход элемента И 12, .на второй вход-которого подается сигнал переноса Р , с входа 34.

0

Получение сигнала переноса.непосредственно по значениям сигналов фаз операндов позволило повысить быстродействие предлагаемого устройства и уменьшить количество обору5дования за счет исключения промежуточных операций по вычислению конкретного значения результата сложения, необходимых для получения сигнала переноса в полном сумматоре.

Симметричность многофазного кода

0 и простота его дешифрации позволила получить сигнсш переноса из подмножеств, многократно перекрывающих друг друга, что повысило надежность работы устройства в целом.

5

Формула изобретения

Устройство для формирования сигнала переноса при суммировании многофазных кодов, содержащее в каждом разряде элементы И и ИЛИ, а также узлы дешифрации старших разрядных комбинаций первого и второго операндов устройства, входы которых соединены с шинами инверсных значений нечетных и шинами прямых значений четных двоичных разрядов представления данного разряда многофазного кода первого и второго операндов устройства соответственно, отличающееся тем, что, с целью повы шения быстродействия и уменьшения количества оборудования, при суммировании чисел с вычислением только

значения п эеноса, первые входы элементов И пер ъл группы соединены с соответствующими Вь ходами узла дешифрации старших paspiijftKbyc комбинаций первого операнда, второй- ж} д каждого нечетного элемента И riepsenгруппы соединен с шиной инверсного значения соответствующего четного двоичного разряда представления данного разряда многофазного кода второго- операнда устройства, второй вход каждого четного элемента И первой группы соединен с шиной прямого значения последующего нечетного двоичного разряда представления данного разряда многофазного кода второго операнда устройства, первые вхог ды элементов И второй группы соединены с соответствующими выходами узла дешифрации старших разрядных комбинаций второго операнда, второй вход каждого нечетного элемента И второй группы соединен с шиной инверсного значения соответствующего четного двоичного разряда представления данного разряда многофазного кода первого операнда устройства, второй вход каждого четного элемента И второй группы соединен с шиной прямого значения последующего нечетного двоичного разряда представления данного разряда многофазного кода первого операнда устройства, выходы элементов И первой и второй групп и первого и второго элементов И соединены с входами первого элемента ИЛИ, выход которого соединен с выходом переноса из данного разряда устройства, первые входы элементов И третьей.и четвертой групп соединены с выходами узлов дешифрации старших разрядных комбинаций первого и второго операндов соответственно, начиная с вторых . выходов, второй вход каждого нечетного элемента И третьей группы соединен с шиной инверсного значения соответствующего четного двоичного разряда представления данного разряда многофазного . ..кода второго операнда устройства, второй вход каждого четного элемента И третьей группы соединен с шиной прямого значения последующего нечетного двоичного разряда представления данного разряда многофазного кода второго операнда устройства, за исключением последнего двоичного разряда, второ вход каждого нечетного элемента И

четвертой группы соединен с шиной инверсного значения соответствующего четного двоичного разряда представления данного. .разряда многофазного кода первого операнда устройства, второй вход каждого четного

Элемента И четвертой группы соединен с шиной прямого значения после. дующего нечетного .двоичного разряда представления данного разряда многофазного .кода первого операнда устройства, за исключением последнего двоичного разряда, входы первого элемента И соединены с шинами инверсных значений первых двоичных разря5 Дов представления данного-разряда многофазного кода первого и второго операндов устройства, выходы элементов И третьей и четвертой групп, выходы третьего и четвертого элеменQ тов И и первые выходы узлов дешифрации старших разрядных комбинаций первого и второго операндов соединены с входами второго элемента ИЛИ, выход которого подключен к первому

5 входу второго элемента И, второй

вход которого соединен с входом переноса в данный разряд устройства, входы третьего элемента И соединены с шиной инверсного значения первого

двоичного разряда представления данного разряда многофазного кода первого операнда устройства и с шиной прямого значения последнего двоичного разряда представления данного разряда многофазного кода второго операнда устройства, входы четвертого элемента И соединены с шиной :.инверсного значения первого двоичного разряда представления данного разряда многофазного кода второго операнда устройства и с шиной прямого значения последнего двоичного разряда представления данного разряда ..многофазного кода первого операнда устройства.

5 Источники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР по заявке № 2352761/18-24, кл. G 06 F 7/385, 1978.

0 2, Прангишвили И.В.и др. Микроэлектроника и однородные структуры для построения логических вычислительных устройств. М,, Наука, 1967, с. 176, рис. 4.22.

3. Авторскоесвидетельство СССР по заявке №. 2585230/18-24, кл. G 06 F 7/385, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сложения по модулю | 1982 |

|

SU1064278A1 |

| Устройство для формирования сигнала переноса при суммировании многофазных кодов | 1989 |

|

SU1633393A1 |

| Многоразрядное устройство для сложения и вычитания | 1981 |

|

SU993264A1 |

| Одноразрядный сумматор | 1978 |

|

SU739530A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для умножения (его варианты) | 1984 |

|

SU1249508A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Устройство для умножения | 1979 |

|

SU826341A1 |

| Арифметическое устройство с микропрограммным управлением | 1988 |

|

SU1541594A1 |

| Устройство для суммирования | 1979 |

|

SU868750A1 |

I iff

.-Ж

iff

lE 27 :Ey

.

Авторы

Даты

1982-04-23—Публикация

1979-01-31—Подача