ойства. В таком устройстве увеличиается скорость передачи кода адреа из процессора, однако скорость ередачи информации .возрасти не моет, так как из различных строк марицы информация поступает по общим инам, и скорость ее обработки опрееляется быстродействием блоков паяти. Время проверки запоминающего стройства зависит от его ёмкости и от скорости обработки информации запоминающим устройством. Так, для проверки устройства с временем цикла 1 МКС, емкостью 4096 бит по -теоту скачущие единицы и нули необходимо затратить время, определяемое по формуле

t 8 4096 1 10 2,24 мин где N - емкость проверяемого устройства, 1ц - время цикла проверяемого

устройства.

Для проверки устройства емкостью 16384 бит с тем же быстродействием потребуется уже 35,84 мин. Резкое увеличение времени проверки необходимо учитывать при разработке полупроводниковых запоминающих устройств с высокой информационной емкостью, так как при этом снижается производительность контрольного оборудования, увеличивается стоимость контроля и себестоимость устройства.

Целью изобретения является повь. шение информационной емкости устройства.

Поставленная цель достигается тем, что в полупроводниковое запоминающее устройство, содержащее матричный накопитель, выходы которого подключены к одним из входов селектора и выходным шинам устройства, одни из входов матричного накопителя через формирователи выборки соединены d выходами дешифратора адреса, входы которого подключены к одним из выходов регистра адреса, другие выходы которого через адресные формирователи подключены к адресным входам матричного накопителя, информационные шины и шины записи-считывания, в него введены дополнительный дешифратор адреса, элементы ИЛИ и ИЛИ-НЕ, причем один из входов дополнительного дешифратора адреса подключен к первой шине записи-считывания, другие входы - к другим входам селектора и соответствующим выходам регистра адреса, выходы дополнительного дешифратора адреса подключ;ены к первым входам элементов ИЛИ, вторые входы которых подключены -к второй шине записи-считывания, а выходы элементов ШШ подключены к другим входам матричного накопителя, информационные входы которого подключены к выходам соответствующих элементов ИЛИ-НЕ, входы которых подключены к входным информационным шинам.

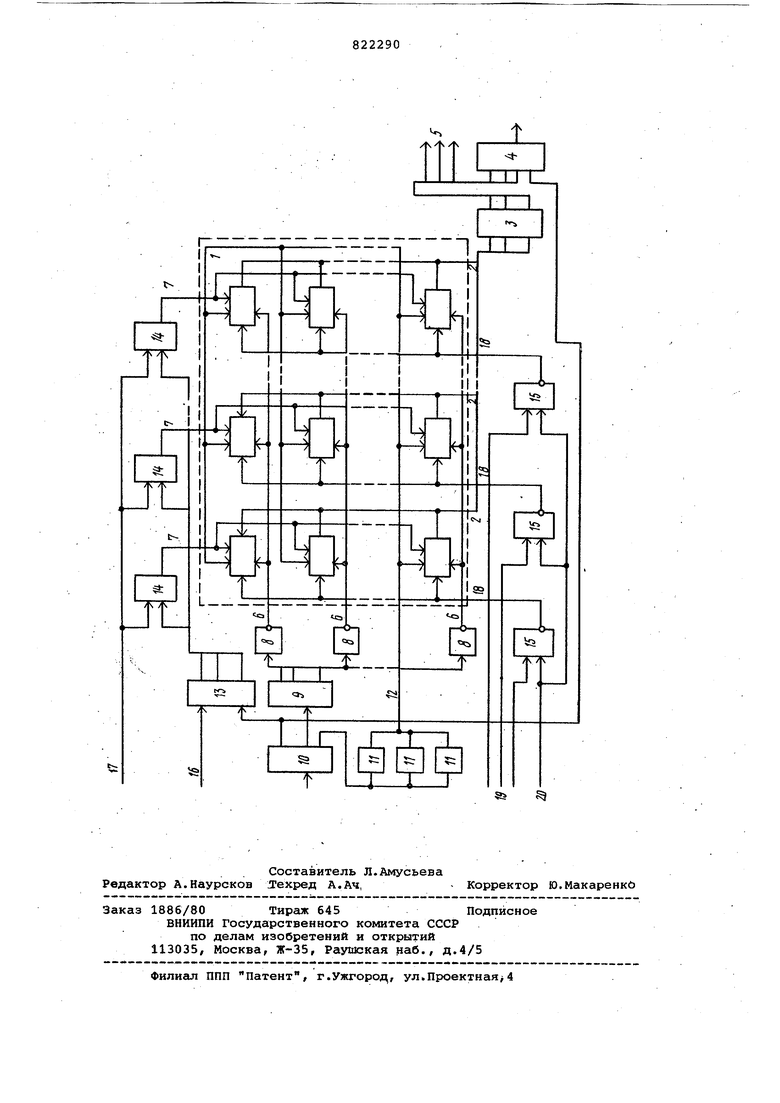

На чертеже представлена функциональная схема полупроводникового запоминающего устройства.

Устройство содержит блоки памяти, объединенные в матричный накопитель 5 1, выходцые шины 2, регистр 3 инфорг мации, селектор 4, выходные шины 5 устройства, входы 6 и 7 матричного накопителя, формирователи 8 выборки, дешифратор 9 адреса, регистр 10 адреса, адресные формирователи 11, адресный вход 12 матричного накопителя, дополнительный дешифратор 13 адреса, элементы 14 ИЛИ, элементы 15 , шины 16 и 17 записи-считывания, информационные входы 18 матричного 5 накопителя, входные информационные шины 19 и 20..

Устройство имеет два режима работы: режим работы в составе видеотер. минального комплекса и режим контроля.

Во время работы в составе, видеотерминального комплекса запись информации осуществляется, как в одноразрядное ЗУ. Код адреса с выходов 5 регистра 10 адреса поступает на входы формирователей 11, входы дешифратора 9 и дешифратора 13. Входная информация поступает по шине 20, код операции записи - по шине 16. Формирователи 8 выборки выбирают необходимую строку блоков памяти матричного накопителя 1, дешифратор 13 выбирает необходимый блок в выбранной строке, который по коду операции, поступающему по шине 16, переключается в режим записи, а ос альные блоки данной строки остаются в режиме чтения. Информация, поступившая по шине 20, записывается в выбранный блок памяти. В режиме чтения информация считывается одновременно со всех блоков памяти выбранной строки и записывается в регистр 3. информации, который работает в режиме сдвига информации и преобразует параллельный код ин

5 формации в последовательный, что

увеличивает скорость передачи информации. Предусмотрена также возможность, передачи на выходные шины одного разряда информации через.селектор 4.

В режиме контроля код записи поступает по шине 17, а информация по шинам 19. Выбор блоков памяти осуществляется дешифратором 9 строк. Запись информации осуществляется . одновременно во все блоки пгиляти выбранной строки. При чтении в режиме контроля считанная информация поступает на выходные шины 5 через регистр 3 информации параллельным кодом.

0 В предлагаемом устройстве используются для дешифрации входы записьочитывание блоков памяти, что позво, ляет увеличить емкость уст эойства не за счет увеличения числа блоков

5 в столбце, а за счет увеличения вы хидов дешифратора кода операции.При этом уменьшается емкость входных и выходных информационных шин, что уве личивает быстродействие устройства. Одновременное чтение информации со всех блоков памяти выбранной строки и передача ее послёдовательнвл« кодом позволяют значительно увеличить ско,рость обработки информации запоминаю щих устройств видеотерминального комплекса, у которого осуш.ествляется последовательная выборка информации. Одновременное считывание и выдача . информации со всех блоков памяти выбранной строки в режиме контроля позволяют уменьшить время его контро ля и снизить себестоимость.устройства. Формула изобретения Полупроводниковое запоминающее устройство, содержащее матричный накопитель, выход которого подключены к одним из входов селектора и выходным шинам устройства, одни из входов матричного накопителя через формирователи выборки соединены с выходами дешифратора адреса, входы которого подключены к одним из выходов регистра адреса, другие выходы которого через адресные формирователи подключены к адресным входам матричного на копителя, информационные шины и шины записи-считывания, отличающееся тем, что, с целью повышения информационной емкости устройства, в него введены дополнительный дешифратор адреса, элементы ИЛИ и ИЛИНЕ, причем один из входов дополнительного дешифратора адреса.подключен к первой шине записи-считывания, другие входы - к другим входам селектора и соответствующим выходам регистра адреса, выходы дополнительного дешифратора адреса подключены к первым входам элементов ИЛИ, вторые входы которых подключены к второй шине записи-считывания, а выходы элементов ИЛИ подключены к другим входам матричного накопителя, информационные входы которого подключены к выходам соответствующих элементов ИЛИ-НЕ, входы которых подключены к входным информационным шинам. Источники информации, принятые во внимание при экспертизе 1. Виталиев Г.В. и др. Разработка полупроводниковых сверхоперативных запоминающих устройств. Вопросы радиоэлектроники. Сер.Электронная вычислительная техника, 1977, вып.5, рис.12. .2. Авторское свидетельство СССР № 598120, кл.С 11 С 11/40, 1975 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое запоминающее устройство с произвольной выборкой | 1984 |

|

SU1215135A1 |

| Запоминающее устройство | 1987 |

|

SU1460740A1 |

| Ассоциативно-адресное оперативное запоминающее устройство | 1987 |

|

SU1451773A1 |

| Полупроводниковое запоминающее устройство | 1984 |

|

SU1238157A1 |

| Ассоциативное запоминающее устройство | 1990 |

|

SU1718274A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Запоминающее устройство | 1980 |

|

SU920832A1 |

| Запоминающее устройство | 1985 |

|

SU1252816A1 |

| Ассоциативное запоминающее устройство | 1989 |

|

SU1741175A1 |

| Постоянное запоминающее устройство | 1977 |

|

SU746731A1 |

S

Авторы

Даты

1981-04-15—Публикация

1979-07-09—Подача