Изобретение относится к вычислительной технике, в частности к области запоминающих устройств, и может быть использовано при построении микроЭВМ, имеющих в своем составе оперативное и постоянное запоминающие устройства.

Цель изобретения - упрощение устройства.

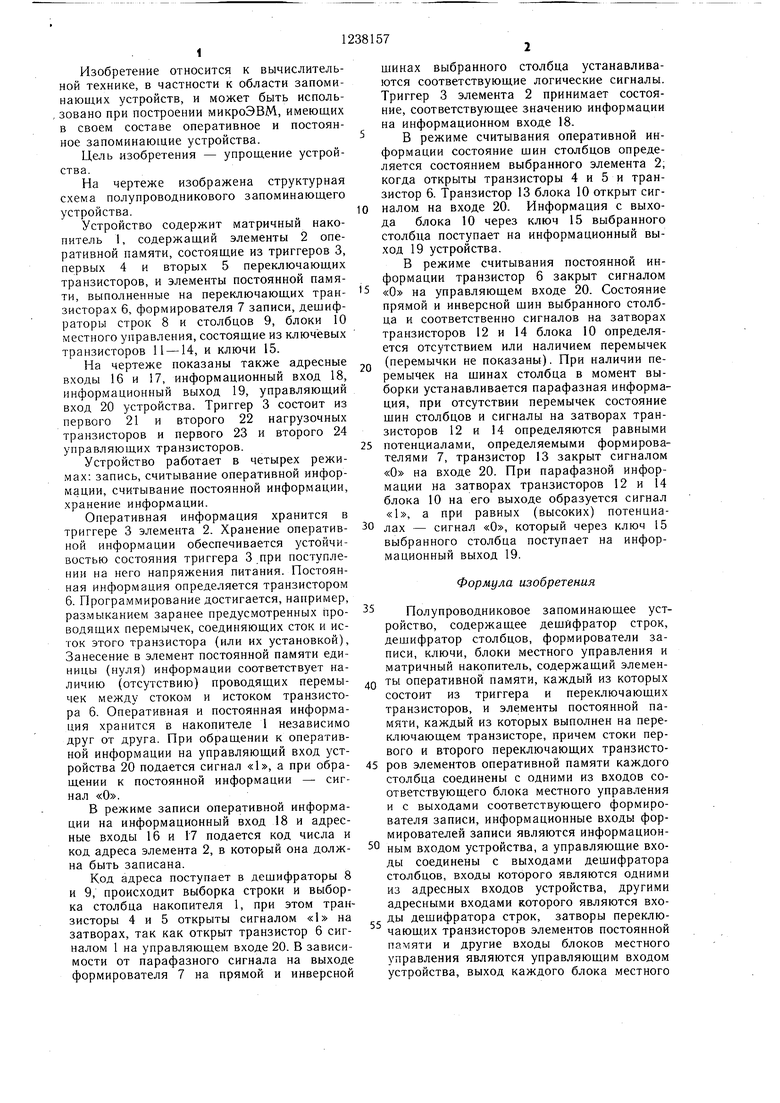

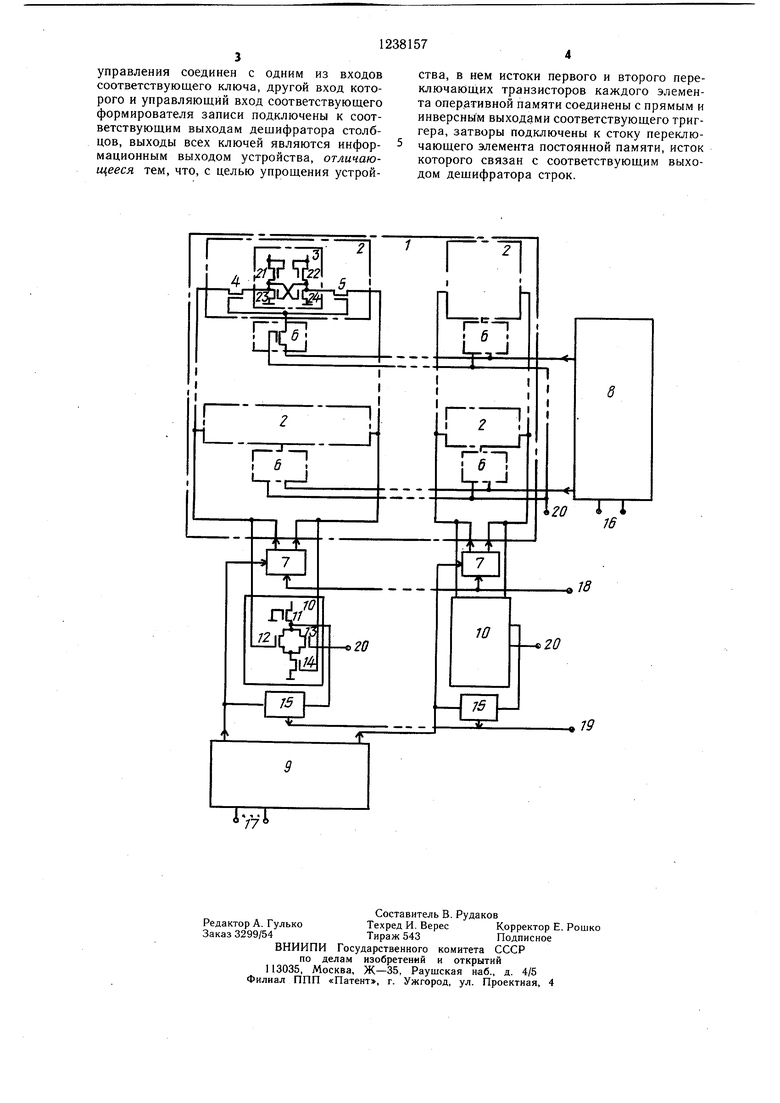

На чертеже изображена структурная схема полупроводникового запоминающего устройства.

Устройство содержит матричный накопитель 1, содержащий элементы 2 оперативной памяти, состоящие из триггеров 3, первых 4 и вторых 5 переключающих транзисторов, и элементы постоянной памяти, выполненные на переключающих транзисторах 6, формирователя 7 записи, дещиф- раторы строк 8 и столбцов 9, блоки 10 местного управления, состоящие из ключевых транзисторов 11 -14, и ключи 15.

На чертеже показаны также адресные входы 16 и 17, информационный вход 18, информационный выход 19, управляющий вход 20 устройства. Триггер 3 состоит из первого 21 и второго 22 нагрузочных транзисторов и первого 23 и второго 24 управляющих транзисторов.

Устройство работает в четырех режимах: запись, считывание оперативной информации, считывание постоянной информации, хранение информации.

Оперативная информация хранится в триггере 3 элемента 2. Хранение оперативной информации обеспечивается устойчивостью состояния триггера 3 при поступле- Е1ИИ на него напряжения питания. Постоянная информация определяется транзистором 6. Программирование достигается, например, размыканием заранее предусмотренных проводящих перемычек, соединяющих сток и исток этого транзистора (или их установкой). Занесение в элемент постоянной памяти единицы (нуля) информации соответствует наличию (отсутствию) проводящих перемычек между стоком и истоком транзистора 6. Оперативная и постоянная информация хранится в накопителе 1 независимо друг от друга. При обращении к оперативной информации на управляющий вход устройства 20 подается сигнал «1, а при обращении к постоянной информации - сигнал «О.

В режиме записи оперативной информации на информационный вход 18 и адресные входы 16 и 17 подается код числа и код адреса элемента 2, в который она должна быть записана.

Код адреса поступает в дешифраторы 8 и 9, происходит выборка строки и выборка столбца накопителя 1, при этом транзисторы 4 и 5 открыты сигналом «1 на затворах, так как открыт транзистор 6 сигналом 1 на управляющем входе 20. В зависимости от парафазного сигнала на выходе формирователя 7 на прямой и инверсной

шинах выбранного столбца устанавливаются соответствующие логические сигналы. Триггер 3 элемента 2 принимает состояние, соответствующее значению информации на информационном входе 18.

В режиме считывания оперативной информации состояние шин столбцов определяется состоянием выбранного элемента 2, когда открыты транзисторы 4 и 5 и транзистор 6. Транзистор 13 блока 10 открыт сигналом на входе 20. Информация с выхода блока 10 через ключ 15 выбранного столбца поступает на информационный выход 19 устройства.

В режиме считывания постоянной информации транзистор 6 закрыт сигналом

5 «о на управляющем входе 20. Состояние прямой и инверсной шин выбранного столбца и соответственно сигналов на затворах транзисторов 12 и 14 блока 10 определяется отсутствием или наличием перемычек

Q (перемычки не показаны). При наличии перемычек на щинах столбца в момент выборки устанавливается парафазная информация, при отсутствии перемычек состояние щин столбцов и сигналы на затворах транзисторов 12 и 14 определяются равными

5 потенциалами, определяемыми формирователями 7, транзистор 13 закрыт сигналом «О на входе 20. При парафазной информации на затворах транзисторов 12 и 14 блока 10 на его выходе образуется сигнал «1, а при равных (высоких) потенциа0 лах - сигнал «О, который через ключ 15 выбранного столбца поступает на информационный выход 19.

Формула изобретения

Полупроводниковое запоминающее устройство, содержащее дещИфратор строк, дешифратор столбцов, формирователи записи, ключи, блоки местного управления и матричный накопитель, содержащий элемен- 0 ты оперативной памяти, каждый из которых состоит из триггера и переключающих транзисторов, и элементы постоянной памяти, каждый из которых выполнен на переключающем транзисторе, причем стоки первого и второго переключающих транзисто- 5 ров элементов оперативной памяти каждого столбца соединены с одними из входов соответствующего блока местного управления и с выходами соответствующего формирователя записи, информационные входы формирователей записи являются информационо ным входом устройства, а управляющие входы соединены с выходами дешифратора столбцов, входы которого являются одними из адресных входов устройства, другими адресными входами которого являются вхо- ды дешифратора строк, затворы переключающих транзисторов элементов постоянной памяти и другие входы блоков местного управления являются управляющим входом устройства, выход каждого блока местного

управления соединен с одним из входов соответствующего ключа, другой вход которого и управляющий вход соответствующего формирователя записи подключены к соответствующим выходам дещифратора столбцов, выходы всех ключей являются информационным выходом устройства, отличающееся тем, что, с целью упрощения устройства, в нем истоки первого и второго переключающих транзисторов каждого элемента оперативной памяти соединены с прямым и инверсным выходами соответствующего триггера, затворы подключены к стоку переключающего элемента постоянной памяти, исток которого связан с соответствующим выходом дешифратора строк.

| название | год | авторы | номер документа |

|---|---|---|---|

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2047919C1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Постоянное запоминающее устройство | 1988 |

|

SU1594603A1 |

| Постоянное запоминающее устройство | 1985 |

|

SU1288756A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Устройство для считывания информа-ции из диНАМичЕСКОгО МАТРичНОгОНАКОпиТЕля | 1978 |

|

SU798996A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

Изобретение относится к вычислительной технике, в частности к области запоминающих устройств, и может быть использовано при построении микроЭВМ, имеющих в своем составе оперативное и постоянное запоминающее устройство. Цель изобретения - упрощение устройства. Устройство содержит матричный накопитель, состоящий из элементов оперативной памяти и элементов постоянной памяти, каждый из которых выполнен на одном переключающем транзисторе. Программирование элемента постоянной памяти осуществляется либо размыканием заранее установленной (на стадии изготовления устройства) проводящей перемычки, соединяющей сток и исток соответствующего транзистора, либо установкой этой перемычки (в процессе программирования). Наличие указанной перемычки соответствует, например, записи единицы. 1 ил. и ьо 00 00 ел

J9

| Горн Л | |||

| С., Хазанов Б | |||

| И | |||

| Элементы микромощных цифровых устройств, М.: Атомиздат, 1980, с | |||

| Способ сопряжения брусьев в срубах | 1921 |

|

SU33A1 |

| Полупроводниковое запоминающее устройство | 1983 |

|

SU1142861A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1986-06-15—Публикация

1984-04-04—Подача